Fターム[5B047EB03]の内容

Fターム[5B047EB03]の下位に属するFターム

リード、ライトタイミング制御 (59)

Fターム[5B047EB03]に分類される特許

1 - 20 / 47

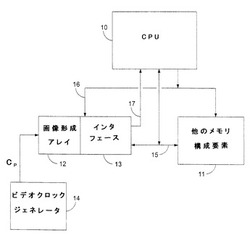

画像形成アレイ用ホストインタフェース

【課題】システムプロセッサがアクセスする画像形成データを直接的に受信することのできる画像形成アレイと共に累積可能なインタフェースを提供する。

【解決手段】画像形成アレイ12を有する画像センサとクロックジェネレータ1Aとからデータを受信し、このデータをプロセッサシステム10へ転送するインタフェース13は、画像形成アレイデータを、該クロック信号により決定された速度で記憶するメモリを備える。このメモリにおけるデータの量に応じて、信号ジェネレータが前記プロセッサシステム10へ伝送するための信号を生成し、また、回路が前記プロセッサシステム10により決定された速度で、前記メモリからのデータの転送を制御する。前記メモリは、先入れ先出し(FIFO)バッファ、または、アドレス可能メモリであり、このインタフェース13は、前記画像センサと同一のダイ上に集積される。

(もっと読む)

メモリ制御方法、メモリ制御装置、および画像形成装置

【課題】シリアル−パラレル変換とパラレル−シリアル変換を効率的に実行する。

【解決手段】画像処理前のラインデータを記憶するラインメモリと画像処理後のラインデータを記憶するラインメモリとを同一素子で構成し、シリアルデータ形式で入力されるラインデータをラインメモリで記憶する処理前・メモリ入力タイミング,記憶された処理前のラインデータをパラレルデータ形式で読み出す処理前・メモリ出力タイミング,処理後のパラレルデータ形式のラインデータをラインメモリで記憶する処理後・メモリ入力タイミング,記憶された処理後のラインデータをシリアルデータ形式で読み出す処理後・メモリ出力タイミング,の4タイミングで制御し、同一ライン周期内に処理前・メモリ出力タイミングの直後に処理後・メモリ入力タイミングを実行すると共に、同一ライン周期内に処理後・メモリ出力タイミングの直後に処理前・メモリ入力タイミングを実行する。

(もっと読む)

画像形成装置、画像形成方法、およびプログラム

【課題】読み取った原稿画像データを順次DMA転送する際に、1枚ずつの原稿処理完了時間を短縮化し、データ転送が正常終了か異常終了かを判別できるようにする。

【解決手段】スキャナユニット14で読み取った画像データをDMA転送するためのDMAC18a〜18cを有するスキャナ画像処理部15と、スキャナ画像処理部15から画像データを受けて、メモリアドレスを発生しメモリ33に書き込むDMAC29を有するコントローラ処理部22と、スキャナ画像処理部15とコントローラ処理部22とを結び、アドレス情報とデータ情報とを用いてやりとりする汎用バスとを備え、スキャナ画像処理部15は、画像データを汎用バス経由でコントローラ処理部22に転送し、画像データの転送完了時にデータ転送終了を示す転送終了信号をコントローラ処理部22に送り、DMAC29は、転送終了信号を受けるとメモリ33への書き込みを終了する。

(もっと読む)

画像処理システム,データ記憶制御装置,データ出力制御装置,データ記憶制御プログラム,データ出力制御プログラム

【課題】二つの情報記憶媒体を用いて画像データの記憶・出力を並行して実行する場合における処理効率を更に向上させることのできる画像処理システムを提供すること。

【解決手段】ハードディスクA1が選択されて画像データD1が記憶されると(時点t1),ハードディスクA2への画像データD2の記憶が開始されると共に,ハードディスクA1からの画像データD1の表示出力が開始される。その後,画像データD1の表示出力が終了すると(時点t2),ハードディスクA2への画像データD2の記憶が中止されてハードディスクA1への画像データD3の記憶が開始されると共に,ハードディスクA2からの画像データD2の表示出力が開始される。即ち,ハードディスクA2への画像データD2の記憶処理は,画像データD1の表示出力が終了するまでの間継続する。

(もっと読む)

動き検出回路

【課題】 本発明の課題は、縮小画像を用いる粗探索と元画像を用いる詳細探索による階層型の動き検出において、先行して行われる粗探索結果から外部メモリから読み出すべき領域をアクセス粒度で行うことにより効率よくメモリアクセスを行うことを目的とする。

【解決手段】 上記課題は、外部メモリから動き検出用バッファに画像データを読み込む際に、縮小画像を用いて動き検出を行った粗探索結果に基づく元画像を用いる詳細探索の動き検出における詳細探索範囲を、該外部メモリのアクセス粒度でなる領域に拡張して読み込むように制御する制御手段と、前記動き検出用バッファに格納されている前記詳細探索範囲を用いて前記詳細探索の動き検出を行う動き検出詳細探索手段と、を有することを特徴とする動き検出回路により達成される。

(もっと読む)

画像処理装置、画像処理方法、コンピュータプログラム

【課題】 入力画像に対して複数種類の画像処理を行う場合、それぞれの画像処理に適した画像を生成するのが望ましい。しかしながら、それらの画像を同時に保持しようとすると、多くのメモリが必要になってしまう。

【解決手段】 本発明では、入力画像に対して複数種類の画像処理(領域解析処理、文字部ベクトル化処理、図画部ベクトル化処理など)を行う場合、各画像処理を実行する前にそれぞれの画像処理に適した画像を生成する。そして、画像処理の処理結果は領域情報に格納するとともに、各画像処理で使用したワークメモリを開放してから、次の画像処理を行う。

(もっと読む)

画像処理装置および画像処理方法、並びにプログラム

【課題】本発明は、メモリの帯域の無駄な消費を抑制すると共に、主メモリへの重複アクセスを抑制することができる画像処理装置を提供する。

【解決手段】主メモリ102上に展開された画像データから主走査方向及び副走査方向に分割された矩形の単位で画像データを読み取り画像処理を行う画像処理装置100において、分割された矩形を囲む矩形の領域であって、隣り合う2つの矩形間の境界を含むように互いに重複する部分を有する参照領域に対して画像処理を行う画像処理手段が、重複する部分に画像処理を行うときに、読み取った画像データをキャッシュに格納する。

(もっと読む)

画像処理装置および画像処理方法

【課題】デバイスドライバからアプリケーションプログラムへの不要な通知を減らすことにより、性能の低下を防ぐことを可能とする。

【解決手段】複数の入力側のディスクリプタ情報を参照してDMA読み出しする入力側DMAC161と、DMA読み出しされた複数のブロックに回転処理を実施する回転処理部162aと、複数の出力側ディスクリプタ情報を参照してDMA書き込みする出力側DMAC163と、を含むASIC16を備え、各ディスクリプタ情報は、当該ディスクリプタ情報を参照して行われたDMA読み出しまたはDMA書き込みが完了したことを表す信号がASIC16からデバイスドライバに出力されたときに、そのことをデバイスドライバプログラムからアプリケーションプログラムへ通知することが必要であるか否かを表す情報を含むテンポラリ領域を有する。

(もっと読む)

画像処理装置、画像処理装置の制御方法及び制御プログラム

【課題】 原稿の両面同時読取を実行する際に、転送側の転送処理能力と受信側の受信処理能力との差分を補間するための専用の記憶手段を削減すること。

【解決手段】 CPU1220は、スキャナI/F 1210を介し、リーダ部1100の原稿データ読取クロックの周波数を片面読取時の半分に対応する周波数に設定する(S402)。

CPU1220は、表面読取部1110が表面原稿データの読み取りを開始し、裏面読取部1120が裏面原稿データの読み取りを開始するよう制御する(S406)。

CPU1220は、リーダ制御部1130を制御して、転送クロックの立上がりエッジで表面のデータを転送し転送クロックの立下りエッジで裏面のデータを転送する(S407)。

CPU1220は、スキャナI/F 1210を制御して、転送クロックの両エッジで表面と裏面のデータを受信し、RAM1250に書き込む(S408)。

(もっと読む)

メモリ制御装置およびカメラシステム

【課題】カメラシステムにおいてアクセス先アドレスが頻繁に切り替わるデータの処理に関しては、データの先読み機能が有効に発揮されない。最小限のメモリ追加によるシステム構成で、アクセスアドレスを随時切り替える必要のある特定のアクセスパターンにおいても、高速なアクセスを実現し、高いアクセス効率を確保する。

【解決手段】メモリ制御部7が外部メモリ30にアクセスする際のアドレスを取得するアドレス取得手段10と、順次取得されるアドレスの差分情報を一時記憶するアドレスメモリ部11と、差分情報を基に順次アクセスのアドレスが一定周期をもつかを認識する周期認識手段12と、一定周期の連続回数が閾値を超えるか否かを判定する一定周期判定手段14とを備える。メモリ制御部7は、一定周期の連続回数が閾値を超えると判定されたときに先読み機能をアクティブにし、次回アクセスが予想されるアドレスに従って外部メモリに対し先読みのアクセスを行って、その先読みデータをバッファ部9にバッファリングする。

(もっと読む)

データ処理回路、画像処理装置、及び、データ処理方法

【課題】簡易な構成により、入力クロックに対して両エッジのタイミングで入力されるデータを、ライン等時性を実現しつつ、内部クロックに同期させるデータ処理回路、画像処理装置、及び、データ処理方法を提供すること。

【解決手段】第一のメモリ領域、及び、前記第一のメモリ領域と同一の内部アドレス空間を有する第二のメモリ領域を有する第一のメモリと、前記第一のメモリに入力されるデータのうち、第一のクロック信号に応答するデータを前記第一のメモリ領域に取り込む第一のデータ入力回路と、前記第一のメモリに入力されるデータのうち、前記第一のクロック信号の反転クロック信号である第二のクロック信号に応答するデータを、前記第二のメモリ領域に取り込む第二のデータ入力回路と、を有するデータ処理回路。

(もっと読む)

メモリコントローラおよび画像処理装置

【課題】高速なメモリアクセスができるメモリコントローラを得ること。

【解決手段】夫々のメモリ領域に対応するアクセス制御ポインタの値を、予め夫々のメモリ領域に対して設定されているアクセスモードに応じて夫々異なるタイミングで単位SIMD分インクリメントするポインタ算出ハードウェア部32と、メモリ領域のアクセス制御ポインタの値に基づいてメモリ領域におけるアクセス先アドレスを算出し、該算出したアクセス先アドレスへアクセス手段にSIMD単位のメモリアクセスを行わせるメモリアクセス制御ハードウェア部33と、を備える。

(もっと読む)

指紋画像形成装置及び指紋画像形成方法

【課題】画像伸縮の少ない指紋画像形成装置及び指紋画像形成方法を提供することを目的とする。

【解決手段】部分センサ上10をスイープする指70の指紋画像を、前記部分センサ10により取得された部分画像を合成することにより形成する指紋画像形成装置であって、

前記部分センサで取得された部分画像データを記録する部分画像データ更新を行うべき指の移動量及び/又は移動位置に相当する値を設定する部分画像データ更新位置設定手段40と、

該部分画像データ更新位置設定手段により設定された部分画像データ更新位置と指の移動量及び/又は移動位置に相当する値に基づいて、前記部分画像データを記録するか否かを判定する部分画像データ更新手段とを有し、

該部分画像データ更新位置設定手段は、前記指の総移動量及び/又は移動位置に対する、記録した前記部分画像データ総量の過不足量Δαを算出し、前記過不足量Δαを相殺するように次の部分画像データ更新判定位置を設定する。

(もっと読む)

画像処理装置、画像処理方法、画像処理プログラム及び記憶媒体

【課題】不揮発性メモリにおける画像データの書込みや揮発性メモリへの退避のタイミングを正しく管理可能な画像処理技術を提供する。

【解決手段】IMH61は、エンジン部3に対してエンジンディスクリプタを設定すると共に、仮想ビデオ入力ドライバ71aに対して仮想ディスクリプタを設定し、MEM15に書き込まれた画像データのHDD14への記憶を制御する。仮想ビデオ入力ドライバ71aは、エンジン部3がエンジンディスクリプタの設定内容に従って画像データをPCIダイレクトアクセスによりMEM15に書き込む場合に、PCIダイレクトアクセスに対する割り込みの発生をハンドリングして、MEM15に書き込まれた画像データをHDD14へ記憶させる。

(もっと読む)

画像処理装置および画像処理プログラム

【課題】レジずれを補正する際、記憶領域上で一度にアクセスできる範囲やアクセス位置の移動についての自由度の向上を図る。

【解決手段】画像処理装置1は、画像データの主走査方向に区分された単位領域毎に副走査方向の補正量を決定する補正量決定部21と、複数のメモリで構成される記憶領域上のアクセス先のアドレス範囲を特定する情報を取得し、該情報からアクセス先の記憶装置上のアドレスを特定し、該アドレスへアクセスする制御を行うアクセス制御部22とを有する。記憶領域は、各単位領域に対応する単位記憶領域を含み、次の条件を満たす。各単位記憶領域は、対応する補正量に応じた個数分のアドレスを有する。各単位記憶領域の各アドレスには、記憶装置上のアドレスが一対一で割り当てられる。各単位記憶領域において、該単位記憶領域の連続する所定の複数個のアドレスには、それぞれ異なる記憶装置が割り当てられる。

(もっと読む)

画素入出力方法、画像圧縮方法、画素入出力装置、画像圧縮装置、画像処理装置、画像形成装置、コンピュータプログラム及び記録媒体

【課題】クロック速度を変更することなく、書き込み用及び読み出し用のメモリを用いて画素を効率よく入出力することができる画素入出力方法、画像圧縮方法、画素入出力装置、画像圧縮装置、画像処理装置、画像形成装置、コンピュータプログラム及び記録媒体を提供する。

【解決手段】パック部41は、入力DMA部21から画素が入力された場合に、入力された画素をM個ずつパックしてなるパックデータを出力し、メモリ制御部42は、パック部41が出力したパックデータを、パック部41に画素が入力された入力周期のM倍の周期で書き込み用のラインメモリ431に書き込みつつ、読み出し用のラインメモリ432からパックデータを入力周期に等しい周期で読み出して処理部20へ出力する。また、メモリ制御部42は、書き込みが終了した書き込み用のラインメモリ431を読み出し用とし、読み出しが終了した読み出し用のラインメモリ432を書き込み用とする。

(もっと読む)

画像処理装置

【課題】

本発明は、同一の高速メモリをCPUのキャッシュメモリおよび画像処理モジュールのワークメモリとして、相互に排他的に使用できるように動的に割り当て可能な画像処理装置を提供する。

【解決手段】

中央演算処理部と、主記憶部と、複数の画像処理部と、中央演算処理部と画像処理部とで共有可能で同時にアクセス可能な高速の高速記憶部と、高速記憶部の記憶領域を中央演算処理部のキャッシュメモリまたは画像処理部のワークメモリとして排他的、かつ動的に割り当てる割当手段とを具備する。

(もっと読む)

画像処理方法及び画像処理装置

【課題】本発明は、出力した画像データを全て初期化する前に、次に出力する画像データを書き込む際に、書き込む画像データの大きさに関係なく最適に行える画像処理方法及び画像処理装置を提案することを目的とする。

【解決手段】ページメモリ2に対して、第2の書込制御部4による画像データの書き込みと、第1の書込制御部3による白データの書き込みが、並列して行われる。このとき、白データが書き込まれるアドレスの、画像データが書き込まれるアドレスに対する先行の度合いによって、第2の書込制御部4による画像データの書き込みの可否が設定される。

(もっと読む)

画像処理装置、画像処理制御方法、画像処理制御プログラム及び記録媒体

【課題】本発明は、外部IFを介して外部装置と通信を行うとともに画像形成処理、画像読み取り処理等のデータ処理を実行する画像処理装置、画像処理制御方法、画像処理制御プログラム及び記録媒体に関する。

【解決手段】複合装置1は、画像読み取り部4、画像印刷部5及び操作部6及び外部IF部12に対応して、それぞれDMAC9〜12を備えており、また、読み取りジョブ制御処理プログラム、印刷ジョブ制御処理プログラム、操作制御処理プログラム及び複写ジョブ制御処理プログラムを備え、各プログラムが、それぞれの動作制御の開始時に、各DMAC9〜12への動作データの設定制御処理において、それぞれの制御対象の処理を優先させる割り込み優先度を動作データとして設定して割り込み発生タイミングを設定し、該動作制御の終了時に、該割り込み優先度を所定の初期割り込み優先度に戻している。

(もっと読む)

画像処理装置

【課題】タイミング信号を生成するための回路やソフトウェアを必要とせず、様々な撮像装置を用いることが出来る画像処理装置を提供する。

【解決手段】画像処理装置は、部分画像データを読み込み順次記憶する部分画像記憶手段と、部分画像記憶手段から得られる部分画像データを合成して合成画像データを生成する画像合成手段と、からなる。部分画像記憶手段は、合成未完了信号が不存在のときのみ、読み込んだ部分画像データを格納して格納が完了すると格納完了信号を生成する。画像合成手段は、格納完了信号の存在下において、合成画像データの生成中の場合は、合成未完了信号を生成し、合成画像データの生成中でない場合は、部分画像記憶手段から部分画像データのうちの少なくとも1つを読み込んでこれを用いて合成画像データの生成を開始する。

(もっと読む)

1 - 20 / 47

[ Back to top ]