Fターム[5B048DD17]の内容

デジタル計算機の試験診断 (4,118) | 試験手段 (1,073) | シミュレータ (206) | 模擬入出力 (61)

Fターム[5B048DD17]に分類される特許

1 - 20 / 61

トランザクションを再生するためのデータを生成する装置及び方法

【課題】サーバのテストのためにトランザクションを再生する際に、トランザクションの再生による不正の発生を抑制し、かつ、トランザクションの再生に要する時間を短縮する。

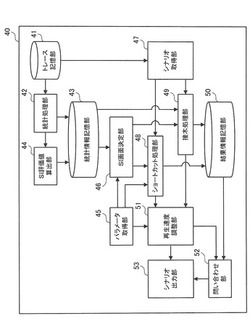

【解決手段】再生シナリオ生成装置40では、SI画面決定部46が、どの画面からでも遷移可能なSI画面をトレースの統計処理結果から決定し、シナリオ取得部47が開始点でアクティブなセッションのシナリオをトレースから取得すると、ショートカット処理部48が、そのシナリオを、認証画面から開始点までの同じSI画面の間の画面遷移をカットすることで短縮し、接木処理部49が、そのシナリオを、認証画面から開始点以前のSI画面までの画面遷移に代えて、トレースの統計処理結果から得られた最短画面遷移を接木することで短縮し、再生速度調整部51が、シナリオの再生速度を調整し、シナリオ出力部53が、これらの処理の結果を出力する。

(もっと読む)

制御プログラム試験装置、制御プログラム試験システム、及び制御プログラムの試験方法

【課題】 被制御装置を模擬した装置模擬プログラムをダウンロードすることなく、制御プログラムの試験を可能とする。

【解決手段】 被制御装置を模擬した装置模擬プログラム30を有するパソコン3に接続されたコントローラ2に、被制御装置を制御する制御プログラム20、被制御装置に対して実際にデータを入出力する実I/O25、被制御装置に対して仮想的にデータを入出力する仮想I/O24、装置模擬プログラム30及び制御プログラム20のいずれか一方からの指令に応じて実I/O25と仮想I/O24とを切替えるI/O切替部23を備え、仮想I/O24からの指令を実行して値変化イベントが発生した場合、I/O切替部23が装置模擬プログラム30に値変化イベントを送信する。

(もっと読む)

オープンソースソフトウェアを利用したハードウェア・ソフトウェア協調検証方法

【課題】 初期導入コストを安く抑えたハードウェアエミュレータを提供し、ハードウェアモデルとハードウェアエミュレータとを容易に接続する技術を提供することを目的とする。

【解決手段】 オープンソースソフトウェアを利用したハードウェア・ソフトウェア協調検証方法であって、オープンソースソフトウェアであるQemuを改変することにより、Qemuとハードウェアモデルの接続するTLMインターフェースを介して、ハードウェアモデルに対してデータI/Oを行う手段と、ハードウェアモデルをQemu上でエミュレートしているPCIバスに接続されているPCIデバイスとして見せる手段と、SystemCシミュレータからQemuを起動する手段とを備えたオープンソースソフトウェアのPCエミュレータを実現する。

(もっと読む)

負荷シミュレーション装置、シミュレーション装置、負荷シミュレーション方法、シミュレーション方法及びプログラム

【課題】仮想ウェブクライアントがリクエストメッセージの送信とレスポンスメッセージの受信とを適切に行えるシナリオを作成できるようにする。

【解決手段】作成されたシナリオに基づいてサーバに対してアクセス負荷をかける負荷シミュレーション装置は、サーバに対して予め実行されたリクエストと、該リクエストに対するレスポンスとを対応付けて記憶する第1記憶部と、記憶された各リクエストが有するリクエストパラメータと、記憶された各レスポンスが有するレスポンスパラメータとの間で一致するものを検索する検索部と、前記検索の結果に基づいて、各リクエストパラメータと、各レスポンスパラメータとの対応関係を記憶する第2記憶部と、記憶された各リクエストを、該リクエストが有するリクエストパラメータを前記対応関係に基づいて変更して、実行する実行部とを備える。

(もっと読む)

情報処理装置及びプログラム

【課題】不要な処理による処理効率の低下を防ぎつつ、必要な精度での模擬時刻の同期を行う情報処理装置を提供する。

【解決手段】情報処理装置は、検証対象のターゲットコードを実行するターゲットCPUの動作を模擬するCPUコアシミュレータ104と、ターゲットCPUの制御対象装置の動作を模擬する装置シミュレータ103と、ターゲットCPUに対するタイマ部の動作を模擬するタイマシミュレータ111と、タイマシミュレータ111の設定からCPUコアシミュレータ104に発生するタイマイベントの時刻を判定し、判定したタイマイベントの時刻までの模擬動作を装置シミュレータ103に指示するシミュレータ接続部102と、を備えている。

(もっと読む)

試験装置、検証モデル開発方法及びプログラム

【課題】様々なインターフェイスに応じた検証環境を短期間に容易に構築する。

【解決手段】被試験対象モデル11との間で信号の入出力を行う信号入出力制御部131と、信号入出力制御部131が実行するインターフェイスの機能を指定するプログラムPを格納した記憶部132と、プログラムPに応じて、信号入出力制御部131の設定を行う疑似プロセッサ133を有し、被試験対象モデル11がアクセスする装置の動作を模擬する疑似モデル13を設ける。

(もっと読む)

インサーキットエミュレータ

【課題】エミュレーション時に、プログラム実行を停止させることなくレジスタ情報を外部に読み出し、且つ、エミュレーション対象と同じプログラム動作を実現すること。

【解決手段】インサーキットエミュレータは、プログラムを実行するプロセッサをエミュレートするメインプロセッサと、周辺機能をエミュレートする第1、第2周辺プロセッサと、外部と通信可能なエミュレーション制御回路と、アクセス制御回路と、を備える。第1周辺プロセッサは、メインプロセッサによってアクセスされる第1周辺レジスタを備え、第2周辺プロセッサは、第1周辺レジスタと内容が同期した第2周辺レジスタを備える。アクセス制御回路は、エミュレーション制御回路によって発行される読み出し要求に応答して、バイパス処理を実行する。そのバイパス処理において、アクセス制御回路は、第2周辺レジスタからデータを読み出し、当該読み出しデータをメインプロセッサを介することなくエミュレーション制御回路に出力する。

(もっと読む)

分散制御システム試験実行管理装置

【課題】分散制御システム試験実行管理装置において、入出力模擬装置の処理負荷を考慮して、効率的に再試験する。

【解決手段】試験項目に対応付けて予め決められた手順に基づいて分散制御システムにおける被制御装置の模擬装置として制御装置の入出力手段との入出力動作を行なう入出力模擬装置2a〜cは、得られた処理負荷の測定結果と該当する試験項目での入出力結果とを出力し、試験実行管理装置1が有する試験結果判定手段16によってその入出力結果と該当する試験項目での期待する入出力結果とから合否判定を行った結果と、前記処理負荷とを試験項目格納手段14が該当する試験項目に対応付けて格納し、実施する試験項目を選択する試験項目選択手段13は、その格納結果を参照して実施する試験項目を選択する。

(もっと読む)

電子機器および電子機器の制御装置

【課題】簡略な構成を追加するのみで、サブCPU単体で動作確認を可能にした制御装置を提供する。

【解決手段】データをメインCPUに送信する第1の機能部、メインCPUからデータを受信する第2の機能部の一方または両方を備え、さらに、第1の機能部、第2の機能部とメインCPUとの通信を制御するデータ通信部と、を備えた電子機器の制御装置に、単体動作モード時に、データ通信部をメインCPUに接続するためのデータ経路を自己宛に切り換え、第1の機能部のデータの受信または第2の機能部に対するデータの送信を含むメインCPUの動作をシミュレートする単体動作制御部をさらに備えた。

(もっと読む)

シミュレーション装置

【課題】並列化されていないソフトウェアを用いて、マルチコアプロセッサを有する情報処理システムで並列化したソフトウェアを動作させたときの性能を評価する。

【解決手段】並列化前のソフトウェア109を命令セットシミュレータ102で動作させながら、命令セットシミュレータでのシミュレーションにより要求されたバスアクセスを分割条件に従って分割し、バスシミュレータ103にて、バスの各ポートに対して分割されたバスアクセスについてバスモデルに対するバスアクセスを生成させバスモデルに供給するようにして、ソフトウェアの並列化を行うことなく、マルチコアプロセッサを有する情報処理システムで並列化したソフトウェアを動作させたときのバスアクセスを再現する。

(もっと読む)

アプリケーションサーバ、アプリケーション障害再現方法、およびアプリケーション障害再現プログラム

【課題】アプリケーションの障害発生時に、本番環境に即した環境を再現し、障害再現を自動的に行うことができるアプリケーションサーバを提供する。

【解決手段】リクエストに基づいてアプリケーションを実行する実行手段と、アプリケーションの動作状態を取得する取得手段と、前記動作状態がアプリケーションの障害発生状態である場合に、該障害発生時におけるリクエストに応じた障害再現用リクエストを送信するための擬似クライアント実行手段を生成する生成手段および前記アプリケーションを複製した障害再現用アプリケーションを実行する障害再現用アプリケーション実行手段を生成する生成手段と、擬似クライアント実行手段に対して障害再現用リクエストを障害再現用アプリケーション実行手段に送信させ、前記障害再現用アプリケーションの実行に伴うログデータを取得する障害再現手段と、を備えるアプリケーションサーバ。

(もっと読む)

データ処理装置及びデータ処理方法及びプログラム

【課題】実システムの受信データを用いて試験システムを試験する場合に、受信データに対応する実システムのデータベースを試験システムのデータベースに復元する。

【解決手段】実システム200は実際に稼働している計算機システムであり、試験システム400は試験対象の計算機システムである。試験装置100は、計算機202が外部システム300から受信する受信データ、計算機202でのデータ処理の推移を示す計算機内部データ、データベース201での更新の経過が示されるデータベース状態データを収集し、収集したデータを用いて、計算機202が受信データに対するデータ処理を行う時点でのデータベース201を復元し、復元したデータベース201に一致させて試験用データベース401を更新し、受信データを試験対象計算機402に出力し、更新後の試験用データベース401を用いて受信データに対する応答を行わせる。

(もっと読む)

プログラム変更検証装置及びプログラム変更検証方法

【課題】プログラムの変更内容を効率よく評価できるプログラム変更検証装置を提供する。

【解決手段】複数の演算処理と、各演算処理の結果に基づいて異常の有無を検出して対応する診断コードを生成する複数の診断処理とを含み、任意の演算処理が変更された評価対象プログラムを実行するプログラム実行部2と、前記プログラム実行部2で実行されたときに、前記診断処理で生成された診断コードをメモリに記憶する診断コード記憶処理部3と、前記診断コード記憶処理部3によりメモリに記憶された診断コードを表示部に表示する診断コード表示処理部4と、を備え、前記診断コード表示処理部4は、メモリに記憶された過去の診断コードと今回の診断コードを対比して診断コードの変動情報を生成し、当該変動情報を表示部に表示することを特徴とするプログラム変更検証装置。

(もっと読む)

ソフトウェア開発装置、実車試験方法、及びエミュレーション方法

【課題】先行開発された電子制御装置の制御ロジックを迅速かつ適切に検証可能なソフトウェア開発装置を提供する。

【解決手段】マイクロコンピュータのCPUにより実行される制御ロジックを実行する制御ロジック処理部と、当該マイクロコンピュータのCPUにより実行される周辺回路に対するI/O処理を模擬するI/O処理部を備え、制御ロジック処理部が、基本機能が同一である複数の制御ロジックを並行して実行するように構成され、制御ロジック処理部とI/O処理部との間に介在して、I/O処理部を経由した入力データを制御ロジック処理部で実行される各制御ロジックに個別に供給し、入力データに基づき各制御ロジックにより演算されたそれぞれの出力データの何れか一方をI/O処理部に出力するインタフェース部を備えているソフトウェア開発装置。

(もっと読む)

通信システム

【課題】通信動作の確認方法を、通信ケーブルを用いた外部通信によって行う方法と、外部通信を行わずに仮想的に行う方法とで切り替えうる通信システムを提供する。

【解決手段】通信システム1は、仮想通信確認手段と外部通信確認手段とを備えており、更に、これら仮想通信確認手段及び外部通信確認手段のいずれかを選択する選択手段を有している。また、仮想通信確認手段は、通信ポート割当手段と仮想送受信手段とを備えており、選択手段により仮想通信確認手段が選択された場合、仮想送受信手段により、一のアプリケーションプログラムから他のアプリケーションプログラムに対してデータの仮想的な送受信を行い、その送受信結果に基づいてデータの通信動作を確認する。

(もっと読む)

操作記録同時再生システム

【課題】操作者が操作対象に対して操作を行った後に、同一もしくは他の操作対象に対して前回と同じ操作を同じタイミングで行い、それに加え、前回操作時の操作対象の動作との違いを視覚的にわかるようにする。

【解決手段】操作者が第1の操作対象10に対して行った操作の操作内容を操作履歴取得部11によって取得し、またその時の操作対象の動作を映像取得部12によって映像で取得し、時刻情報を元に操作履歴と映像を同期記録部13によって同期させ、記録部14に記録する。そして、同期再生部15によって記録部14に記録された操作履歴と映像を呼び出し、操作履歴再現部17によって第2の操作対象18に前回と同じ操作を同じタイミングで行いながら、映像表示部16によって映像を再生する。これにより、前回操作時の操作対象の動作の映像と前回と同一操作を行なった時の操作対象の動作を比較することが出来る。

(もっと読む)

プログラムテスト装置、およびプログラム

【課題】従来、ハードウェアがエラーの場合のテスト対象プログラムのテストも自動的に容易にできない、という課題があった。

【解決手段】テスト対象プログラムをテストするために当該テスト対象プログラムに与える情報である入力情報と動作パターンとを有するテスト情報を受け付けるテスト情報受付部と、テスト情報が有する動作パターンを取得し、シミュレータプログラムに渡すテスト制御部と、テスト情報が有する入力情報をテスト対象プログラムに与え、当該テスト対象プログラムを実行し、かつ、当該テスト対象プログラムの実行結果であるプログラム情報と、テスト制御部がシミュレータプログラムに渡した動作パターンとを用いてシミュレータプログラムを実行する実行部とを具備するプログラムテスト装置により、ハードウェアがエラーの場合のテスト対象プログラムのテストも自動的に容易できる。

(もっと読む)

模擬マイクロコンピュータ装置

【課題】CPUに暴走等の異常が発生しても、制御対象が安全に作動可能な模擬マイクロコンピュータ装置を提供する。

【解決手段】模擬マイクロコンピュータ装置は、制御対象の動作を制御するためのプログラムである第一のプログラムを実行する第一のCPUと、第一のCPUの周辺リソースとして機能し、前記第一のCPUからの前記制御対象を制御するための信号の出力を制御する第二のプログラムを実行する第二のCPUと、第一のCPUと第二のCPUの異常を監視し、第一のCPUと第二のCPUの少なくとも一方の異常を検出すると、第二のCPUにリセット信号を出力する異常監視部とを備え、前記リセット信号が入力されると、第二のCPUは前記制御対象が安全な動作を行なうように制御するプログラムである第三のプログラムを実行するように構成される。

(もっと読む)

電子機器

【課題】マイコンの異常を、簡単な通信で正確に検知できるようにする。

【解決手段】画像処理装置は、複数のマイコンを備え、これら複数のマイコンにより、車両前方の路面を撮影するカメラからの入力画像データを処理し、レーンマーク(白線等)の形状及び自車両との位置関係を特定して、これらの情報を表す道路パラメータを、外部ECUに送信する。メインマイコンは、上記入力画像データをフィルタ処理してエッジ情報を生成し、これをサブマイコンに入力する。サブマイコンは、エッジ情報を受信すると、受信したエッジ情報に基づき道路パラメータを算出すると共に、サブマイコンの異常をメインマイコンが検知できるよう所定の宿題演算を実行し、道路パラメータと共に、宿題演算結果Y及び宿題演算に用いた変数値Cを送信する。メインマイコンは、道路パラメータと共に値Y,Cを受信し、受信値Y,Cに基づき、サブマイコンに異常があるか否かを判断する。

(もっと読む)

エミュレーション装置及びエミュレーションプログラム

【課題】実際の運用データに基づくテストデータを、テストの目的に応じた柔軟な送信タイミングで送信可能なエミュレーション装置を提供することを課題とする。

【解決手段】データ配信サーバ5によるデータ提供環境を擬似提供するエミュレーション装置10であって、第1接続状態において、データ配信サーバ5からデータを受信する要求API14aと、受信されたデータと当該データが受信された受信時刻を特定するための受信時刻情報とを相互に関連付けて格納する受信データDB12と、第2接続状態において、受信データDB12に格納されたデータを被テストサーバ7に送信する送信タイミングを、当該データに関連付けて受信データDB12に格納された受信時刻情報に基づいて決定し、当該決定した送信タイミングにて当該データを被テストサーバ7に送信する発行API14eとを備える。

(もっと読む)

1 - 20 / 61

[ Back to top ]