Fターム[5B060AA06]の内容

メモリシステム (7,345) | アロケーション、リロケーション (1,705) | 空間、領域管理手段 (388) | テーブル、表 (138)

Fターム[5B060AA06]に分類される特許

1 - 20 / 138

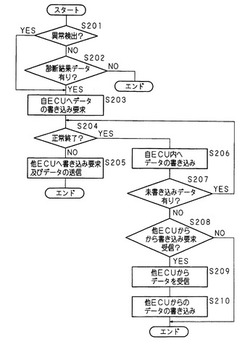

電子制御システム及び電子制御装置

【課題】自装置に十分な記録容量がない場合、又は記録装置が故障している場合であっても、自他装置の記録しておくべきデータを損失することなく記録することができる電子制御システム及び電子制御装置(ECU)を提供する。

【解決手段】データを記録する記録手段及び通信手段を有し、制御対象物の動作を制御する複数の電子制御装置を、通信線を介してデータ通信することが可能に接続してある。一の電子制御装置は、記録手段に所定のデータを記録することが可能であるか否かを判断し、可能であると判断した場合、記録手段にデータを記録する。可能ではないと判断した場合、他の電子制御装置へデータを送信する。他の電子制御装置は、受信したデータを記録手段に記録する。

(もっと読む)

フラッシュメモリ装置、メモリ制御装置、メモリ制御方法、ストレージシステム

【課題】フラッシュメモリ装置について、ガベージコレクション(GC)の発生頻度を効果的に減らすことにより記録速度の向上を図る。

【解決手段】ブロックサイズ未満のデータがシーケンス書込されるように制御する。ブロックレベルとページレベルの2種の管理でデータ書込を行う従来のフラッシュメモリ装置では、書込データがブロックサイズと一致する場合はブロックレベル管理による記録を行いブロックサイズ未満の場合はページレベル管理による書込を行うため、例えばブロックサイズ未満のデータについてそれらが論理アドレス的に連続している個々のデータであったとしても、それらのデータはページレベル管理で書き込まれてしまう。これに対し本技術によれば、ブロックサイズ未満のデータについてシーケンス書込ができ、結果GCの発生頻度を低下させて記録速度の向上が図られる。

(もっと読む)

半導体装置、不揮発性メモリ装置の制御方法

【課題】長寿命化などを実現できる半導体装置を提供する。

【解決手段】本半導体装置(メモリモジュールMM0)の制御回路(SC0)は、データ書込みの要求に対し、上書き可能な不揮発性メモリ装置(NVM)へのデータ書込みの際、上書き要求であっても上書き動作せずに、データの書込と消去のサイズを同じにして、メモリ(NVM)のアドレスを連続的に割当てて使用し、メモリ(NVM)の使用のバラツキを抑え平準化する仕組みにより、長寿命化などを実現する。制御回路(SC0)は、(a)第1のアドレスのデータの消去動作、またはフラグ値を無効に設定する動作と、(b)第1のアドレスとは別の第2のアドレスに対するデータの書込動作、またはフラグ値を有効に設定する動作との2種類の動作のセットによりデータ書込みを実現する。

(もっと読む)

メモリシステム、不揮発性記憶装置及びその制御方法

【課題】読み出し動作を高速化し、かつ書き込みに利用可能なフリーブロックを増加させる。

【解決手段】メモリシステム1は、不揮発性記憶装置3と情報処理装置2とを有する。情報処理装置2は、不揮発性記憶装置3の第1の論理アドレス領域からデータを読み出し、第1の論理アドレス領域に対応する読み出しデータが関数で表されるデータと同じである場合に、不揮発性記憶装置3に、第1の論理アドレス領域のデータを無効にするための削除通知を行う第1の制御回路を含む。不揮発性記憶装置3は、有効なデータに対応する論理アドレスと物理アドレスとを関連付ける管理テーブルと、削除通知により指定された論理アドレスを無効にするように管理テーブルを書き換え、情報処理装置2から受信した読み出し命令に含まれる論理アドレスが無効である場合に、関数で表されるデータを情報処理装置2に送信する第2の制御回路とを含む。

(もっと読む)

半導体装置及びメモリ保護方法

【課題】情報を効果的に保護できる半導体装置を提供すること。

【解決手段】実施形態の半導体装置1は、プロセッサ10と、不揮発性半導体記憶装置22を有し、プロセッサ10に対する主記憶として機能するメモリ装置20とを備える。プロセッサ10は、複数のプログラムCD1、CD2を実行する際に、プログラムを実行するために必要な情報をプログラム毎にワークセットWS1、WS2として管理すると共に、各々のワークセットWS1、WS2に必要な情報と、その情報のメモリ装置20内におけるアドレスとの関係を保持するテーブルPT1、PT2を、ワークセットWS1、WS2毎に作成する。メモリ装置20に対するアクセスは、ワークセットWS1、WS2毎に対応するテーブルPT1、PT2を参照して実行される。

(もっと読む)

メモリ装置およびメモリシステム

【課題】書き込み時の論理アドレスによらず書き込み速度を低下させずデータを書き込むことが可能で低消費電力化が可能なメモリ装置およびメモリシステムを提供する。

【解決手段】メモリコントローラ200は、論物変換テーブル204を持ち、消去済みの物理ブロックアドレスとその不揮発性メモリ、不揮発性メモリ毎の消去済みの物理ブロック数を管理する消去済み物理ブロック管理部206と、消去可能物理ブロックアドレスとその不揮発性メモリ、不揮発性メモリ毎の消去可能の物理ブロック数を管理する消去可能物理ブロック管理部205と、メモリ制御部207と、を含み、メモリ制御部は、消去済み物理ブロック管理部で管理される一の不揮発性メモリの第1の物理ブロックにデータの書き込みを行い、書き込みと並行して消去可能物理ブロック管理部で管理される他の不揮発性メモリの第2の物理ブロックの消去を行う。

(もっと読む)

半導体記憶装置

【課題】管理情報を記憶するランダムアクセス可能なメモリの記憶容量を増大させることなく、ランダムリード及びランダムライト性能を向上させる。

【解決手段】実施形態においては、ランダムアクセス可能な第1の半導体メモリに含まれる第1の記憶部と、ページ単位で読み出し及び書き込みが行われ、ページより大きなブロック単位で消去が行われる不揮発性の第2の半導体メモリに含まれる第2の記憶部と、第2の半導体メモリの記憶領域を、ブロック単位で前記第2の記憶部に割り当てるコントローラと、第2の記憶部のデータを第1の管理単位で管理するための第1の管理テーブルであって、第2の半導体メモリに記憶される第1の管理テーブルと、第2の記憶部のデータを第1の管理単位より大きな第2の管理単位で管理するための第2の管理テーブルであって、第1の半導体メモリに記憶される第2の管理テーブルとを備える。

(もっと読む)

メモリコントローラ、及びデータ記録装置

【課題】管理テーブルを不揮発性メモリに保存する時の応答遅延時間を縮減し、データ記録装置の電源遮断後に、不揮発性メモリに保存した情報から管理テーブルを復元する機能を備えるメモリコントローラを提供する。

【解決手段】不揮発性メモリ1011は、管理テーブル格納ブロックと、データ書き込みのために割り当てたスクラッチブロックと、データを保持するデータブロックと、データを消去した消去済みブロックを持つ。メモリ1012は、データの格納場所を管理する論理・物理アドレス変換テーブル10120と、ブロック履歴管理テーブル10125を持つ。管理テーブル格納ブロックは、論理・物理アドレス変換テーブル10120とブロック履歴管理テーブル10125を保存する管理テーブルページを持つ。メモリコントローラ1010は、論理・物理アドレス変換テーブル10120の一部を不揮発性メモリ1011の管理テーブル格納ブロックに保存する。

(もっと読む)

電力制御方法、計算機システム、及びプログラム

【課題】サーバに搭載されているメモリの消費電力を制御し、消費電力を削減する。

【解決手段】一つ以上の業務サーバ、業務サーバを管理する管理サーバ、及び、業務サーバと管理サーバとを接続するネットワーク、を備える計算機システムで実行されるメモリの消費電力を制御する方法であって、業務サーバは、メモリの消費電力を制御できる単位である一つ以上のメモリチップと、メモリチップの消費電力を省電力状態と通常状態とに切り替える制御を実施する電力制御機構と、一つ以上の仮想サーバを稼動させる仮想化機構と、を備え、管理サーバが、メモリチップのうち通常状態のメモリチップを特定し、管理サーバが、特定された通常状態のメモリチップのうち、仮想サーバに対して未割り当てのメモリチップを特定し、管理サーバが、特定された未割り当てのメモリチップの消費電力を省電力状態に変更するように業務サーバに指示する。

(もっと読む)

メモリコントローラ及びメモリコントローラを備える不揮発性メモリシステム、並びに不揮発性メモリの制御方法

【課題】ホストシステムから与えられるデータを格納するための領域を減少させることなく、論理ページと物理ページの対応関係を効率良く管理する。

【解決手段】それぞれの物理ブロックにおいて、物理ブロック内の物理ページをn個(nは2以上の整数)のグループに分割し、物理ブロック内のそれぞれの物理ページに、ホストシステムから与えられるユーザデータを書き込む際に、当該ユーザデータを書き込む物理ページに、当該ユーザデータに対応する論理ページを示す番号と共に、当該物理ページと同じグループに属する他の物理ページに格納されているユーザデータに対応する論理ページを示す番号を書き込む。

(もっと読む)

メモリコントローラ及びメモリコントローラを備えるフラッシュメモリシステム、並びにフラッシュメモリの制御方法

【課題】データの書き換えにおいて、書き換え後のデータを、書き換え前のデータと同じ物理ブロックに格納できる確率を高くする。

【解決手段】所定の期間毎に、論理ゾーンに含まれるそれぞれの論理ブロックに対する書き込み比率を算出し、この書き込み比率に基づいて、それぞれの論理ブロックに分配する予備論理ページの分配数の比率を決定する。この予備論理ページの分配数の比率に基づいて、それぞれの論理ブロックに分配するマッピング論理ページを決定する。

(もっと読む)

半導体記憶装置、その制御方法および情報処理装置

【課題】コマンド応答速度および書き込み効率が改善される半導体記憶装置を提供すること。

【解決手段】キャッシュメモリとしての第1の記憶部と、ページ単位で読み出し及び書き込みが行われ、ページ単位より大きなブロック単位で消去が行われる不揮発性半導体メモリに含まれる第2及び第3の記憶部と、不揮発性半導体メモリの記憶領域を、1以上の前記ブロックに対応付けられた論理ブロック単位で、第2及び第3の記憶部に割り当てるコントローラとを備え、コントローラは、不揮発性半導体メモリのリソース使用量が所定の閾値を越えている場合に、不揮発性半導体メモリのデータを整理してリソースを増加させる整理部と、ホストから整理状態通知要求が入力されると、整理部による整理状態を判別し、その判別結果を整理状態通知としてホストへ出力する整理状態通知部とを備える。

(もっと読む)

電子機器及びメモリの初期化方法

【課題】製造コストを増大させることなく、メモリの初期化を高速に行い、提供するサービスの遅延を防ぐこと。

【解決手段】第1のCPU101は、第2のメモリ104に対する電源の供給が開始された場合においてデータ送信要求を受けた際に、各々のメモリブロックを所定の順番で特定するメモリブロック識別子を順次生成し、所定の順番に従ってメモリブロックにデータを書き込むとともにメモリブロック識別子を転送管理テーブル205に書き込む。第2のCPU103は、転送管理テーブル205から順次読み出したメモリブロック識別子により特定される所定の順番に従って、メモリブロックに書き込まれたデータを順次読み出すとともに、データを読み出したメモリブロックを特定するメモリブロック識別子をメモリ管理テーブル203に順次書き込むことにより第2のメモリ104を初期化する。

(もっと読む)

半導体記憶装置及び半導体記憶装置の制御方法

【課題】CPUからの1コマンドでコンパクション動作が実行される半導体記憶装置。

【課題を解決するための手段】半導体記憶装置は、不揮発性メモリのコマンドをキューイングするキューイングバッファ(26)と、不揮発性メモリのリードコマンドを発行するリード手段(#102)と、リード手段により前記不揮発性メモリから読み出されたデータをユーザデータと管理データとに分離する分離手段(#104)と、不揮発性メモリのライトアドレスを管理するライトポインタ情報により示されるアドレスを分離手段により得られた管理データに対して加えてライトコマンドを発行し、キューイングバッファへ自動的にキューイングするライトコマンド発行手段(#110)と、ライトコマンド発行手段により発行されたライトコマンドを不揮発性メモリに与え、データを不揮発性メモリに書き込むライト手段(#114)とを具備する。

(もっと読む)

不揮発性メモリのコントローラ及び不揮発性メモリの制御方法

【課題】コンパクション処理の対象候補となるブロックの検索動作がメインメモリへのアクセス速度に影響しない不揮発性メモリのコントローラを提供する。

【解決手段】不揮発性メモリのコントローラ(1)であって、不揮発性メモリへのデータ書き込み時にデータ書き込みに伴い無効にすべきページが属するブロックの有効ページ数をカウントする手段(5)と、前記カウント手段によりカウントされた有効ページ数が所定数以下の場合、前記ブロックをコンパクション処理の対象とする追加手段(61)とを具備するコントローラ。

(もっと読む)

メモリ制御システム

【課題】CPUからメモリへのアクセス時間を短縮する。

【解決手段】内部メモリ206は外部メモリ203に格納されているデータの複製を所定サイズのデータブロック単位で格納している。読み出し対象データの複製が内部メモリ206に格納されていない場合に、メモリアクセス制御プログラム210は、読み出し対象データを外部メモリ203から読み出し、読み出した読み出し対象データをCPU201の読み出し要求元に供給し、その後、メモリアクセス制御プログラム210は、読み出し対象データを含むデータブロックを外部メモリ206から読み出し、DMAコントローラ703を用いて、読み出したデータブロックを内部メモリ206に格納する。

(もっと読む)

マルチコアプロセッサシステム

【課題】キャッシュの一貫性を保ちつつマルチコアプロセッサがメインメモリとして使用できる領域を動的に追加/削除することができるマルチコアプロセッサシステムを提供する。

【解決手段】マルチコアプロセッサは、被管理領域31に含まれる小領域毎に、プロセッサコアに割り当てられていない未割り当て状態かまたはすでにプロセッサコアに割り当てられている割り当て済み状態であるかを管理するとともに小領域毎のメモリアクセスプロトコルを管理する状態管理部(21、22、33および34)と、被管理領域のうちの未割り当て状態の小領域を増減させることによって被管理領域31を増減させる被管理領域増減部23と、を備える。

(もっと読む)

ノンユニフォームアクセスメモリにおけるスケーラブルなインデックス付け

多数のレコードにスケールし、高トランザクションレートを提供するインデックスを構築するための方法及び装置である。ノンユニフォームアクセスメモリデバイスが、そのメモリデバイスにとって効率的であるIO(入力/出力)トラフィックに遭遇しながら、インデックス付けアルゴリズムがそのアルゴリズムにとって自然(効率的)である方法で行うことを保証するために、新しいデータ構造及び方法が提供される。インデックス付けアルゴリズムによって見なされた論理バケットを、メモリデバイス上の物理バケットにマップする、あるデータ構造である変換テーブルが作成される。このマッピングは、ノンユニフォームアクセスSSD及びフラッシュデバイスへの書込み性能が強化されるようにするものである。バケットを集め、大きい順次書き出しとして、メモリデバイスへ順次書き出すために、もう1つのデータ構造である連想キャッシュが使用される。インデックス付けアルゴリズムによって必要とされる(レコードの)バケットでキャッシュをポピュレートするために、方法が使用される。フリー消去ブロックの生成を容易にするために、追加のバケットが、デマンド読出し中に、或いはスキャベンジング処理によって、メモリデバイスからキャッシュへ読み出されてもよい。  (もっと読む)

(もっと読む)

メモリシステムおよびメモリシステムの管理方法

【課題】上書き不可能な不揮発性メモリにおけるブロック移動を伴うデータ書き込み処理の効率化、高速化をなし得るメモリシステムを提供すること。

【解決手段】同一論理ブロックが第1および第2のメモリの各1つの物理ブロックと対応付けられるように論理ブロックと第1および第2のメモリの物理ブロックとの対応を管理し、同一論理ブロックで対応付けられた物理ブロック間ではデータが記憶されるページが重複しないように同一論理ブロックに含まれるページのデータを記憶し、第1のメモリに対して行う処理と、第2のメモリに対して行う処理とを並行に実行する。

(もっと読む)

電子装置及びそのブーティング方法

【課題】 ブーティングの速度が改善される電子装置及びそのブーティング方法を提供する。

【解決手段】 本発明の実施形態による装置初期化ファイルと装置実行ファイルとが貯蔵されている非揮発性の第1貯蔵部と、揮発性の第2貯蔵部を含む電子装置のブーティング方法は、初期ブーティングの時、前記装置実行ファイルを前記第1貯蔵部から前記第2貯蔵部にロードする段階と;ロードされた装置実行ファイルに対する参照情報を生成する段階と;前記電子装置のパワー・オフの時、前記第2貯蔵部の電源供給を維持する段階と;再ブーティングの時、前記装置初期化ファイルを前記第1貯蔵部から前記第2貯蔵部にロードして実行する段階と;前記参照情報を参照して前記第2貯蔵部に貯蔵されている前記装置実行ファイルを実行する段階と;を含む。

(もっと読む)

1 - 20 / 138

[ Back to top ]