Fターム[5B060AA13]の内容

メモリシステム (7,345) | アロケーション、リロケーション (1,705) | 管理項目、処理項目 (539) | アドレス (79)

Fターム[5B060AA13]に分類される特許

1 - 20 / 79

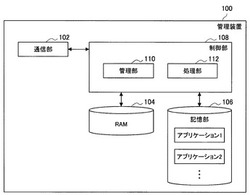

管理装置、管理方法、およびプログラム

【課題】複数のアプリケーションが順次に実行される場合において、効率的なメモリ管理を行うことが可能な、管理装置、管理方法、およびプログラムを提供する。

【解決手段】複数のアプリケーションの実行順序を示す実行制御情報に基づいて、アプリケーションが実行されるときにアプリケーションが一時的に記憶される記録媒体における、実行領域と、キャッシュ領域とを管理する管理部を備える、管理装置が提供される。

(もっと読む)

メモリへのデータ格納方法

【課題】様々な変数条件で発生する学習値を、各条件により細分化された学習メモリ領域に効率的に格納できるメモリへのデータ格納方法を提供する。

【解決手段】本発明は、メモリへのデータの格納方法であって、特定変数条件により特定データが得られると、複数のセルに分割されている全メモリ領域で、特定変数条件に該当するセルを指定する段階と、特定データをセルに格納する段階と、特定データが格納されたセルを分割する段階と、を有し、

以後、新しい特定変数条件により新しい特定データが得られるごとに、全メモリ領域で、新しい特定データが発生した変数条件に該当するセルの指定と、新しい特定データの格納と、データが格納されたセルの分割と、を繰り返すことを特徴とする。

(もっと読む)

メモリ装置

【課題】 外部に読み出されるパラメータが示すユーザー領域の総容量に含まれない拡張ユーザー領域を準備することにより、ファイルシステムのフォーマット等により、特定のデータの消去を防止可能なメモリ装置を提供する。

【解決手段】 不揮性半導体メモリ18は、第1の記憶領域18cと、第2の記憶領域18eを有する。制御部11aは、ホスト20からの第1のコマンドを受け、第1のコマンドに基づき前記第2の記憶領域の使用を許可する。制御部11aは、ホスト20からの第2のコマンドを受け、第2のコマンドに基づき第1の記憶領域の容量を示すパラメータをホストに送信し、制御部は、ホストからの第3のコマンドを受け、第3のコマンドに基づき第1の記憶領域にアクセスし、制御部は、前記第2の記憶領域の使用が許可されたとき、ホストから前記第3のコマンドを受け、第3のコマンドに基づき前記第2の領域にアクセスする。

(もっと読む)

メモリシステムの制御方法、情報処理装置、及びプログラム

【課題】ユーザにとって任意のタイミングで容易に性能を向上させることが可能なメモリシステムの制御方法を提供する。

【解決手段】実施形態のプログラム3により実行される不揮発性メモリ11を備えたメモリシステム10の制御方法は、メモリシステムを備えた情報処理装置1に搭載されたオペレーティングシステム2から未使用記憶領域を取得し、未使用記憶領域の他のプログラムによる利用を禁止し、未使用記憶領域のアドレスを取得する。メモリシステムの制御方法は、未使用記憶領域のアドレスをメモリシステムへ通知する。メモリシステムの制御方法は、ユーザによる変更指示があるまで禁止を維持する。

(もっと読む)

コンピュータのメモリ使用についての情報を提供するシステム及び方法

【課題】コンピュータのメモリ使用に関する情報を提供する。

【解決手段】ディスプレイユニットに接続されるクライアントユニット8を有する呼出コンピュータ2、駆動システムコア4、駆動システムコアユニット5、カップリングユニット6、及び中継ユニット7を有する被呼出コンピュータ1、及び少なくとも1つの呼出コンピュータと少なくとも1つの被呼出コンピュータとを接続する通信チャネルとを備え、カップリングユニットは、駆動システムコアに統合される駆動システムコアユニットと、少なくとも1つの被呼出コンピュータに統合される中継ユニットとに接続され、中継ユニットと駆動システムコアユニットとの間で中間のデータ転送装置としての役割を果たし、駆動システムコアユニットへのアクセスを確立し、中継ユニットから駆動システムコアユニットにデータを転送し、駆動システムコアユニットから中継ユニットにデータを伝送する。

(もっと読む)

画像形成装置

【課題】 揮発性記憶装置上の配分の変更がOSの起動後に不可能な領域に対して配分を変更することができる画像形成装置を提供する。

【解決手段】 MFP10は、画像データを記憶する領域を含む複数の領域が確保されるRAM23と、RAM23上の領域の配分の情報である配分情報31を記憶するフラッシュメモリ30と、RAM23上に領域を確保するOSと、OSをブートするブート手段と、フラッシュメモリ30に記憶されている配分情報31を変更する配分情報変更手段とを備えており、配分情報31は、RAM23上の配分の変更がOSの起動後に不可能な領域の配分の情報を含んでおり、ブート手段は、配分情報31をOSの起動前にRAM23に書き込み、OSは、ブート手段によってブートされるとき、フラッシュメモリ30にアクセス可能となる前に、RAM23に記憶されている配分情報に基づいてRAM23上に領域を確保することを特徴とする。

(もっと読む)

メモリコントローラ

【課題】フラッシュメモリにおける検索効率を向上させる。

【解決手段】メモリコントローラ20は、機器制御部10からデータの書き込み要求を受けると、フラッシュメモリ30にアクセスして、指定されたデータサイズ分の空きセクタを検索する。空きセクタがない場合、何れかのブロックのデータを消去することで、指定されたデータサイズ分の空きセクタを確保する。その際、使用中のセクタのデータは、所定の移動方向に基づいて、他のセクタに移動される。メモリコントローラ20は、機器制御部10からデータの書き込み指示を受けると、機器制御部10から転送されたデータを、検出又は確保した空きセクタに書き込む。そして、メモリコントローラ20は、機器制御部10からデータの読み出し指示を受けた際に、当該データが当初に書き込んだセクタに存在しないと、上記の移動方向に基づいて絞り込んだ領域の範囲で当該データを検索する。

(もっと読む)

メモリコントローラ及びメモリコントローラを備えるフラッシュメモリシステム、並びにフラッシュメモリの制御方法

【課題】データの書き換えにおいて、書き換え後のデータを、書き換え前のデータと同じ物理ブロックに格納できる確率を高くする。

【解決手段】所定の期間毎に、論理ゾーンに含まれるそれぞれの論理ブロックに対する書き込み比率を算出し、この書き込み比率に基づいて、それぞれの論理ブロックに分配する予備論理ページの分配数の比率を決定する。この予備論理ページの分配数の比率に基づいて、それぞれの論理ブロックに分配するマッピング論理ページを決定する。

(もっと読む)

バス変換回路

【課題】各制御装置から各カードにアクセスできるアドレス空間領域の大きさを制御装置の数に依存せずに維持したまま、競合を回避する制御手順を省略し、カード制御にかかる時間を短縮することができるバス変換回路を実現する。

【解決手段】複数の制御装置が接続される第1のバスとこの第1のバスとは異なる種類の第2のバスとの間に配置され、第1のバスを介して入力された制御装置からのパケットに含まれる第1のアドレスを第2のバスの第2のアドレスに変換するバス変換回路において、制御装置毎に第2のバスのベースアドレスを記憶し、パケットに含まれる制御装置を特定する固有値に応じて、制御装置に対応したベースアドレスを用いて第1のアドレスを第2のバスの第2のアドレスに変換する。

(もっと読む)

メモリ装置、メモリ装置を備えたメモリシステム及びマイクロコントローラ、並びに、メモリ制御装置

【課題】ミスアラインデータに対して高速に読み出すことのできるメモリ装置、メモリシステムを提供する。

【解決手段】複数のワード線と複数のビット線を設け、複数のワード線とビット線によりアドレスを特定してアクセスできるように構成されたメモリ装置であって、一本のワード線に対応して連続するアドレスの複数のメモリセルが配置され、それぞれに対応する複数のビット線から並列に連続するアドレスの複数のメモリセルにアクセスできるように構成され、複数のワード線のうち、第一のワード線と第一のワード線と連なるアドレスを指定する第二のワード線との間で重複するアドレス範囲を設け、第一のワード線に接続される第一のメモリセルと第二のワード線に接続される第二のメモリセルが同一アドレスに対応して重複して設けられている。

(もっと読む)

メモリチップおよびメモリシステム

【課題】複数のポートを備え、各ポートからの同時アクセスを行うこと。

【解決手段】複数の単位領域に分割され、前記複数の単位領域は夫々個別にアクセスを受ける不揮発性のメモリセルアレイ10と、アクセスコマンドの入力を夫々受け付ける複数のポートと、アクセスコマンドに基づいて前記メモリセルアレイに夫々個別にアクセスするポート毎に備えられる複数の処理系11と、複数の処理系11の夫々が受け付けたアクセスコマンドに含まれるアクセス先アドレスを相互に比較することによってアクセス先の単位領域が複数の処理系11間で競合しているか否かを判定する競合判定を実行する競合判定部12と、を備え、複数の処理系11の夫々は、競合判定部12による競合判定結果が競合ありであるとき、アクセスの開始を待機し、競合判定結果が競合なしであるとき、アクセスを開始する。

(もっと読む)

記憶装置

【課題】迅速な処理でウェアレベリングを実現する記憶装置を提供すること。

【解決手段】不揮発性メモリ52は、アドレスが付されたブロックを複数有し、当該複数のブロックに当該ブロックの数よりも少ない数のユーザデータを記憶するユーザデータ領域52Aと、ユーザデータ領域52Aへのユーザデータの記憶を制御するデータを含む管理データを記憶する管理データ領域52Bとを備え、管理データ領域52Bは、制御部により最も新しく記憶されたユーザデータが記憶されているユーザデータ領域52Aのブロックに付されているアドレスを管理データとして記憶するアドレス記憶部521Bを有し、制御部は、新たにユーザデータを記憶させる場合、アドレス記憶部521Bに記憶されたアドレスより大きいアドレスが付されたユーザデータ領域52Aのブロックにユーザデータを記憶させた後、当該ブロックに付されたアドレスをアドレス記憶部521Bに記憶させる。

(もっと読む)

メモリ制御装置、画像形成装置およびメモリ制御方法

【課題】 1ページ分の画像データについて同じページメモリ部を複数回使用する際、必要なメモリ量を少なくする。

【解決手段】 画像入力部3は画像データを入力する。バンド化部5は画像データの複数ライン毎を1バンドにする。ページメモリ部9は、画像データの1ページ分に必要な必要記憶領域と1個の追加バンド分の追加記憶領域を確保する。第1の処理部7は画像データに第1の処理をする。第2の処理部7は第1の処理がされた画像データに第2の処理をする。メモリ制御部17は、第1の処理のなされた画像データをページメモリ部9先頭より記憶する。メモリ制御部17は、記憶画像データを読み出して第2の処理をなし、既記憶画像データに連続記憶して、記録に用いるバンドが追加記憶領域に達したとき、ページメモリ部9の先頭に戻って記憶する。

(もっと読む)

メモリアクセス制御システムおよびメモリアクセス制御方法

【課題】効率的なメモリアクセスを行う。

【解決手段】アクセス頻度通知部200が、CPU100から主記憶400−1〜400−2へのアクセス頻度を、主記憶400−1〜400−2にあらかじめ設定されたアドレスごとに監視し、監視したアクセス頻度があらかじめ設定された頻度閾値を超えたアドレスがある場合、CPU100へ通知を行い、そのアドレスをレジスタに保持し、アクセス頻度通知部200からCPU100へ通知があった場合、割り当て変更部300が、レジスタに保持されているアドレスに基づいて、CPU100における主記憶400−1〜400−2のアドレスの割り当てを変更する。

(もっと読む)

メモリ制御システム

【課題】CPUからメモリへのアクセス時間を短縮する。

【解決手段】内部メモリ206は外部メモリ203に格納されているデータの複製を所定サイズのデータブロック単位で格納している。読み出し対象データの複製が内部メモリ206に格納されていない場合に、メモリアクセス制御プログラム210は、読み出し対象データを外部メモリ203から読み出し、読み出した読み出し対象データをCPU201の読み出し要求元に供給し、その後、メモリアクセス制御プログラム210は、読み出し対象データを含むデータブロックを外部メモリ206から読み出し、DMAコントローラ703を用いて、読み出したデータブロックを内部メモリ206に格納する。

(もっと読む)

メモリコントローラ、画像処理システムおよびメモリアクセスの制御方法

【課題】 画像データを読み書きする半導体メモリのアクセス効率を向上する。

【解決手段】 アクセスコスト計算部は、読み出しアクセスおよび書き込みアクセスの少なくともいずれかに必要なサイクル数をアクセスコストとして複数のメモリマップ毎に計算する。メモリマップ選択部は、メモリマップの中からアクセスコストが最も低いメモリマップを選択する。パラメータ変換部は、メモリマップ選択部が選択したメモリマップに基づいて、アクセスアドレスを変換する。アクセス制御部は、変換されたアクセスアドレスに基づいて半導体メモリにアクセスするための制御信号を生成する。アクセスコストの低いメモリマップを用いて半導体メモリにアクセスすることで、半導体メモリのアクセス効率を向上できる。

(もっと読む)

メモリ制御方法、メモリ制御装置

【課題】フリップフロップを他の論理と兼用することができるメモリ制御方法、メモリ制御装置を提供する。

【解決手段】メモリに対するデータの書き込みにおける書き込み位置を選択する場合、メモリの格納領域のうち、少なくとも1つ以上の格納領域を有する格納ブロックにおける格納領域のアドレスと、格納ブロックに対して冗長化され、少なくとも1つ以上の格納領域を有する複数の冗長化ブロックのいずれかにおける格納領域のアドレスとを書き込み位置として選択し、データの書き込みによりメモリに書き込まれたデータの読み出しにおける読み出し位置を選択する場合、格納ブロックにおける格納領域のアドレスと、複数の冗長化ブロックのアドレスのうち、書き込み位置の選択において選択されたアドレスとを前記読み出し位置として選択する。

(もっと読む)

ネットワーク中継装置

【課題】連想メモリを使用して各属性用の専用記憶領域を用意することなく、属性に応じた処理を可能とするネットワーク中継装置を提供する。

【解決手段】受信したデータに対応するエントリが登録されたCAMと、CAMの動作を制御する制御部とを備え、エントリはデータの属性を表す属性情報と、同一属性のデータの処理順序を管理するページ情報とを含み、制御部はCAMに新たなエントリを登録する際にCAMの空きエントリのアドレスを取得し、該取得したアドレスが新たなエントリの属性情報と同一属性の最後のエントリのアドレスよりも大きい場合、新たなエントリのページ情報を最後のエントリのページ情報と同じページ番号とし、小さい場合新たなエントリのページ情報を最後のエントリのページ情報とは異なるページ番号として、新たなエントリを取得した空きエントリのアドレスに追加することにより、上記課題を解決する。

(もっと読む)

メモリ管理システム、電子機器及びメモリ管理プログラム

【課題】 メモリのフラグメンテーションの発生を防ぎ、連続した大容量のメモリ空間を確保しやすくすること。

【解決手段】 メモリ管理システムにおいて、メモリのフラグメンテーションの発生を防ぎ、連続した大容量のメモリ空間を確保しやすくするという目的を物理メモリの割当て位置を示すメモリコントロールブロック表を有して、物理アドレス空間でのメモリの割当を管理するメモリコントロールブロック表管理部と、前記メモリコントロールブロック表をアプリケーション毎に纏めるメモリコントロールブロック制御表を有して、前記メモリコントロールブロック表管理部が管理する物理メモリの割当をアプリケーション毎に管理するメモリコントロールブロック制御表管理部とを有することにより解決した。

(もっと読む)

管理型不揮発性メモリのアドレスマッピングのためのアーキテクチャー

ここに開示するアーキテクチャーは、アドレスマッピングを使用して、ホストインターフェイスにおけるブロックアドレスを不揮発性メモリ(NVM)装置の内部ブロックアドレスへマップする。ブロックアドレスは、そのブロックアドレスで識別される同時アドレス可能なユニット(CAU)を選択するための内部チップセレクトへとマップされる。ここに開示するアーキテクチャーは、読み取り、書き込み、消去及び状態取得オペレーションのための一般的なNVMコマンドをサポートする。又、このアーキテクチャーは、複数のCAUアーキテクチャーをレバレッジする読み取り及び書き込みオペレーションをサポートするための拡張コマンドセットもサポートする。 (もっと読む)

1 - 20 / 79

[ Back to top ]