Fターム[5B060AB25]の内容

Fターム[5B060AB25]の下位に属するFターム

論理→物理アドレス変換 (277)

実効アドレスの算出 (28)

アドレス更新制御 (7)

Fターム[5B060AB25]に分類される特許

1 - 20 / 70

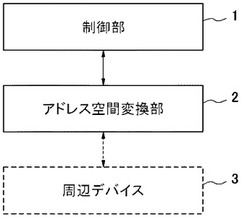

アドレス空間変換装置及びそのアドレス空間変換方法、並びにコンピュータ・プログラム

【課題】

処理bit数の少なさに起因するアクセス空間の制約を回避することによって、大規模な入出力データを処理するアドレス空間変換装置等を提供する。

【解決手段】

アドレス空間変換装置は、制御部と、その制御部によって制御されるアドレス空間変換部とを備える。このアドレス空間変換装置において、前記制御部は、前記アドレス空間変換部に接続された周辺デバイスに、前記アドレス空間変換部を制御することによってアクセスするのに先立って、所定の上位アドレスの範囲を、記憶領域単位を成すアドレス空間に論理的に区画し、そのアドレス空間の区画を、前記アドレス空間変換部に割り当てた後に、その割り当てたアドレス空間の範囲において前記周辺デバイスの下位アドレスを特定する。

(もっと読む)

マルチCPUコア・プロセッサ用DMAC付きDRAMアドレス・マッピング回路

【課題】CPUシステム(PC,TabletPC,PDA etc.)において、CPUコアもしくはOSが32bitであると主記憶サイズは4GB以下の3.5GB程度に制約される。 現状4GB(3.5GB)を超えて搭載したメモリーは無駄となる。 また、実行速度改善に効果がある現在のRAMDISKは主記憶を使う為、主記憶サイズの制限は、32bitシステムでの性能向上の足かせとなっている。

【解決手段】DRAMのローカル・アドレスをシステム物理アドレスにマッピングする回路にDMA機能を持たせる事により、主記憶に割り振れなかったDRAM領域をRAMDISKとして経済的に使用し、かつ、それに関わるデータ転送をDRAMのローカルバス上で局所的に行う事で、従来の主記憶を使ったRAMDISKより、実行効率の良いRAMDISKを供給する。

(もっと読む)

メモリ回路システム及び方法

【課題】メモリ回路システムを提供する。

【解決手段】インタフェース回路104が複数のメモリ回路102及びシステム106と通信できる。使用時、インタフェース回路は、メモリ回路の命令スケジューリングにおける制約を減少させるため、メモリ回路及びシステムをインターフェースするように動作する。別の実施形態では、インタフェース回路が、複数のメモリ回路、及びシステムと通信することができる。使用時、インタフェース回路は、システムとメモリ回路との間で伝達される命令に関連付けられているアドレスを変換するように動作する。更に別の実施形態では、少なくとも1つのメモリ積層体が、複数のDRAM集積回路を備えている。DRAM集積回路とホストシステムの間で1つ以上の物理パラメータを変換する目的で、ホストシステムに結合されたバッファ回路を使用して、ホストシステムにメモリ積層体をインターフェースする。

(もっと読む)

フラッシュメモリ装置、メモリ制御装置、メモリ制御方法、ストレージシステム

【課題】フラッシュメモリ装置について、ガベージコレクション(GC)の発生頻度を効果的に減らすことにより記録速度の向上を図る。

【解決手段】ブロックサイズ未満のデータがシーケンス書込されるように制御する。ブロックレベルとページレベルの2種の管理でデータ書込を行う従来のフラッシュメモリ装置では、書込データがブロックサイズと一致する場合はブロックレベル管理による記録を行いブロックサイズ未満の場合はページレベル管理による書込を行うため、例えばブロックサイズ未満のデータについてそれらが論理アドレス的に連続している個々のデータであったとしても、それらのデータはページレベル管理で書き込まれてしまう。これに対し本技術によれば、ブロックサイズ未満のデータについてシーケンス書込ができ、結果GCの発生頻度を低下させて記録速度の向上が図られる。

(もっと読む)

プログラマブルコントローラシステムおよびメモリ整理方法

【課題】プログラマブルコントローラとプログラミングツールとが接続されたプログラマブルコントローラシステムで、変数を追加する際に断片化されたメモリ領域を整理し、連続領域を確保できるプログラマブルコントローラシステムを得ること。

【解決手段】プログラミングツール10は、変数に割当てられているプログラマブルコントローラのデータメモリ24内の使用領域が連続した領域となるように、変数のデータメモリ24内での割当先を変更する割付変更情報を生成し、変数の割当先の変更に伴うプログラムの実行コードの変更箇所を変更情報として取得し、プログラマブルコントローラに送信する。プログラマブルコントローラは、プログラミングツール10からの変更情報に基づいて、プログラムメモリ22中のプログラムの実行コードを書換えると同時に、データメモリ24中の割当先の変更前のアドレスに記憶されていたデータを割付変更情報に基づいて移動する。

(もっと読む)

メモリの電源制御を行う情報処理装置およびメモリ電源制御プログラム

【課題】仮想マシンを有する情報処理装置のメモリの消費電力を削減すること。

【解決手段】複数の仮想メモリバンクのうちの第1の仮想メモリバンクに有効なデータが無い場合に、前記複数の仮想メモリバンクの各々が前記物理メモリの複数の物理メモリバンクのいずれに属するかを示す情報を格納する仮想メモリバンクプール管理部を参照し、前記第1の仮想メモリバンクに割り当てられた物理メモリバンクが電源オフ可能か判定し、可能であれば電源オフ対象として前記第1の仮想メモリバンクに割り当てられた物理メモリバンクを指定し、前記指定された物理メモリバンクの電源をオフとする。

(もっと読む)

プログラム切替回路、および電子機器

【課題】 プロセッサに特別な機能を持たせることなく、異なるアドレスに格納された別のプログラムを切り替えて、同一のアドレスで実行することのできるプログラム切替回路を得る。

【解決手段】 メモリコントローラ3から送出されるチップセレクト信号5およびアドレス信号6aのアドレスが所定の条件に合致する場合に、アドレス判定/変換部71によって所与のアドレスにオフセットを加えたアドレスを、アドレス信号6bからメモリ4に送出する。

(もっと読む)

入出力制御装置、及び情報処理装置

【課題】未使用の記憶領域の生成を防ぐ

【解決手段】第1処理装置、第2処理装置、第1記憶装置、及び第2記憶装置に対してデータを入出力する入出力制御装置であって、第1処理装置が出力する第1データを分割するデータ分割部と、分割した第1データを、第1記憶装置及び第2記憶装置にそれぞれ格納するとともに、第2処理装置が出力し且つ第1データよりビット数が少ない第2データを、第1記憶装置及び第2記憶装置の何れか1つに格納する格納制御部と、を備える入出力制御装置が提供される。

(もっと読む)

メディアメモリシステム

【課題】親プロセッサアドレス変換をメディアプロセッサのアドレス変換に整合させ、複数のメディアプロセッサに別々の変換テーブル情報によって同時共有メモリアクセスを与えるための方法および装置を提供する。

【解決手段】所定メディアアプリケーションに対するページディレクトリは、メディアアプリケーションが親プロセッサおよびメディアプロセッサ上で実行されるメディアアプリケーションによって共有されるべきメモリを割り当てる場合にメディアプロセッサのページディレクトリにコピーされる。

(もっと読む)

メモリコントローラ、撮像装置

【課題】広帯域メモリアクセス要求に対するインターリーブアクセスと狭帯域メモリアクセス要求に対する非インターリーブアクセスを動的に切り替える。

【解決手段】インターリーブアクセス手段7aと非インターリーブアクセス手段7bを備えたメモリコントローラ10であって、ページ単位でアドレスを変換する記憶管理手段13をさらに有し、前記記憶管理手段13は、ページ毎にインターリーブアクセスと、非インターリーブアクセスを切り替える、ことを特徴とする。

(もっと読む)

コントローラ、データ記憶装置、及びプログラム

【課題】通常利用時の性能を向上させることができるコントローラ、データ記憶装置、及びプログラムを提供する。

【解決手段】書込指示部150は、書込対象データを第1物理アドレスが示すデータ記憶部105の記憶領域へ書き込むことをデータアクセス部106に指示し、アドレス変換情報の更新を管理情報アクセス部121に指示し、第1物理アドレスの更新を第1アクセス部131に指示する。コンパクション部170は、コンパクション対象データの物理アドレスを抽出し、物理アドレスが示すデータ記憶部105の記憶領域に記憶されたコンパクション対象データの読み出しをデータアクセス部106に指示し、第2物理アドレスが示すデータ記憶部105の記憶領域へのコンパクション対象データの書き込みをデータアクセス部106に指示し、アドレス変換情報の更新を管理情報アクセス部121に指示し、第2物理アドレスの更新を第2アクセス部141に指示する。

(もっと読む)

メモリ制御装置及び情報処理システム

【課題】データ転送におけるオーバヘッドサイクルを解消する。

【解決手段】データを記憶可能な複数のメモリM0〜Mn−1と、複数のメモリに対するアクセス要求を発行するデータ処理装置10と、複数のメモリを第1メモリ群と第2メモリ群とにグループ化し、複数のメモリとデータ処理装置10との間のデータ転送を制御するメモリ制御装置20と、を備える。メモリ制御装置20は、データ処理装置10によって発行されたアクセス要求に含まれる第1アドレスAを用いて第2アドレスf(A)を算出するアドレス算出回路21と、第1アドレスAによりアクセスされる第1メモリ群の動作を制御する第1制御コマンドCmd(A)及び第2アドレスf(A)によりアクセスされる第2メモリ群の動作を制御する第2制御コマンドCmdf(A)を、それぞれ、同一サイクルに第1メモリ群及び第2メモリ群に出力する制御部22と、を備える。

(もっと読む)

情報処理装置

【課題】無駄なデータコピーを最小限にし、また物理メモリの使用量も削減する事を目的とする。

【解決手段】デマンドページング処理をする情報処理装置が、ユーザプログラムにより要求されたデータのサイズの領域をユーザ空間に確保する手段と、前記ユーザプログラムにより要求されたデータがカーネル空間に割り付けられた物理メモリに読み込まれると、読み込まれたサイズを前記ユーザプログラムに返却する手段と、前記データが読み込まれた後に、前記ユーザプログラムによる前記データに対するページフォルトが検出されると、前記物理メモリを前記ユーザ空間の前記領域に割り付ける手段と、有することによって課題を解決する。

(もっと読む)

電子機器

【課題】電子機器では、フラッシュメモリなどの不揮発性半導体メモリを電子機器の記憶部として実用可能にすることが求められている。

【解決手段】電子機器1は、データ書込み処理において既に書込まれたデータに対する上書きが禁止されている不揮発性半導体メモリ16を有し、実データおよび当該実データに対応した管理データを記憶する第1記憶部53と、データ書込み処理において任意の値へのデータ上書きが可能な第2記憶部54と、第1記憶部53に対するデータアクセスを制御する制御部52とを有する。制御部52は、第1記憶部53に記憶されている管理データを、第2記憶部54にコピーし、第2記憶部54に記憶されている管理データを参照して、第1記憶部53の実データにアクセスする。

(もっと読む)

複数のフラッシュパッケージを有するストレージシステム

ストレージシステムが、一以上のRAIDグループを構成する複数のフラッシュパッケージと、複数のフラッシュパッケージに接続されたコントローラとを備える。各フラッシュパッケージは、複数の物理ブロックで構成された複数のフラッシュチップを有する。コントローラは、不要領域に関わる対象領域を特定し、その対象領域に属する論理ブロックに割り当てられている物理ブロックをその論理ブロックから解放し、解放された物理ブロックを空きブロックとして管理する。

(もっと読む)

(もっと読む)

エンディアン変換回路、エンディアン変換方法及びマイクロコントローラ

【課題】効率よくエンディアン変換が可能なエンディアン変換回路を提供する。

【解決手段】アドレス信号の最下位ビットをドントケアビットとして番地指令が行われるデータ保持部11と、エンディアン変換部12を有し、エンディアン変換部12は、データ保持部11へアクセスするアドレス信号の最下位ビットの値に基づいて、データ保持部11への書き込みデータ、またはデータ保持部11からの読み出しデータd1に対してエンディアン変換を行う。

(もっと読む)

電子機器

【課題】比較的簡易な構成により電子機器上で複数のプログラムを選択的に起動させる。

【解決手段】電子機器3は、第1のリアルタイムOS及び第1のアプリケーションソフトを格納する第1のメモリバンク、並びに第2のリアルタイムOS及びバージョンの異なる第2のアプリケーションソフトを格納する第2のメモリバンクを有するフラッシュROM12と、第1及び第2のリアルタイムOSのいずれかと同一バンク内のアプリケーションソフトとを既定の演算開始アドレスから起動させるCPU5と、第1のメモリバンク内の第1のリアルタイムOSの起動アドレス又は第2のメモリバンク内の第2のリアルタイムOSの起動アドレスを、上記演算開始アドレスに一致させるようにバンクを切り替えてアドレス変換を行うバンク切替部9とを備える。

(もっと読む)

USBホストコントローラ、及びUSBホストコントローラの制御方法

【課題】ストレージ機器間のデータ転送時間を短縮することが可能なUSBホストコントローラを提供することである。

【解決手段】本発明にかかるUSBホストコントローラ11は、第1のバッファメモリ領域41と第2のバッファメモリ領域42とを有するUSBパイプ用バッファメモリ2と、第1の機器18と第2の機器19とUSBパイプ用バッファメモリ2の間のデータ転送を制御するバッファメモリ制御部1を備える。バッファメモリ制御部1は、第1の機器18からのデータを第1のバッファメモリ領域41に格納し、第1のバッファメモリ領域41に対応するアドレス情報と第2のバッファメモリ領域42に対応するアドレス情報を入れ替え、当該入れ替えた後の第1のバッファメモリ領域41に対応するアドレス情報に基づき第1のバッファメモリ領域41に格納されているデータを第2の機器19に転送する。

(もっと読む)

ヘテロジニアス処理ユニット間での不均一メモリアクセスのためのチップセットサポート

【課題】第2のプロセッサに関連付けられたメモリに第1のプロセッサがアクセスすることを可能にするための方法を提供すること。

【解決手段】この方法は、第1のプロセッサから、NUMAデバイスのためのMMIOアパーチャを含む第1のアドレスマップを受け取るステップと、第2のプロセッサから、ハードウェアデバイスのためのMMIOアパーチャを含む第2のアドレスマップを受け取るステップと、第1のアドレスマップと第2のアドレスマップを組み合わせることによってグローバルアドレスマップを生成するステップと、第1のプロセッサからNUMAデバイスに送られたアクセス要求を受け取るステップと、第1のアクセス要求と変換テーブルとに基づいて、メモリアクセス要求を生成するステップと、グローバルアドレスマップに基づいて、メモリアクセス要求をメモリにルーティングするステップとを含む。

(もっと読む)

不揮発性半導体メモリドライブ装置および不揮発性半導体メモリドライブ装置のアドレス管理方法

【課題】コストアップ等を招くことなくデータ再配置に伴うアドレステーブルの更新を速やかに実行することを実現した不揮発性半導体メモリドライブ装置を提供する。

【解決手段】論理/物理アドレス管理部2031は、データをNANDメモリ204A〜204Hに書き込む際、書き込み先として指定された論理アドレスと書き込み先を示す物理アドレスとを対応づけるためのクラスタテーブルの更新を行うと共に、その論理アドレスを当該データを書き込むページの冗長領域に格納する処理を行う。そして、コンパクション処理部2032によってコンパクションが実施された際、論理/物理アドレス管理部2031は、再配置対象となったデータの論理アドレスを再配置前のページの冗長領域から取得することで、クラスタテーブルの更新を効率的かつ経済的に実行する。

(もっと読む)

1 - 20 / 70

[ Back to top ]