Fターム[5B060AB26]の内容

メモリシステム (7,345) | アドレス制御 (691) | アドレス修飾、アドレス変換制御 (382) | 論理→物理アドレス変換 (277)

Fターム[5B060AB26]に分類される特許

1 - 20 / 277

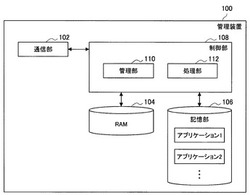

管理装置、管理方法、およびプログラム

【課題】複数のアプリケーションが順次に実行される場合において、効率的なメモリ管理を行うことが可能な、管理装置、管理方法、およびプログラムを提供する。

【解決手段】複数のアプリケーションの実行順序を示す実行制御情報に基づいて、アプリケーションが実行されるときにアプリケーションが一時的に記憶される記録媒体における、実行領域と、キャッシュ領域とを管理する管理部を備える、管理装置が提供される。

(もっと読む)

不揮発性メモリを有するシステムのための高速ツリー平坦化

【課題】不揮発性メモリ(NVM)を有するシステムのための効率的なバッファリングを行うシステム及び方法を提供する。

【解決手段】NVMの論理的スペースと物理的アドレスとの間の論理的−物理的マッピングを含むツリーが揮発性メモリに記憶される。ツリーに使用できるメモリの量が所定のスレッシュホールドより少ないとき、システムは、NVMにおけるデータ断片の数を減少するよう試み、その結果、ツリーの一部分を平坦化する。NVMインターフェイスは、合成すべきツリーのエントリの最適セットを選択する。例えば、ツリーを横切って1つ以上のスライディングウインドウを移動し、条件が満足されたときにスライディングウインドウを拡張し、ツリーをスキャニングしながらプライオリティキューを使用し、及び/又はツリーが更新される間にプライオリティキューを維持する、等の適当な解決策を使用できる。

(もっと読む)

メモリ制御装置およびその方法、データ管理装置およびその方法、並びに、プログラム

【課題】ライトバック処理の発生頻度を抑制することができるようにする。

【解決手段】メモリ制御部は、不揮発性メモリに書き込む書き込みデータを有する上位層としてのファイルシステム制御部から、書き込みサイズ通知により、書き込みデータのサイズを取得する。メモリ制御部は、取得された書き込みデータのサイズの空き領域を検索し、検索結果に基づき、書き込みデータの書き込み先の論理アドレスを上位層に通知する。本技術は、例えば、不揮発性メモリを制御するメモリ制御装置に適用できる。

(もっと読む)

端末装置及び端末装置におけるメモリ制御方法

【課題】消費電力の削減を図るようにした端末装置及び端末装置におけるメモリ制御方法を提供すること。また、アプリケーションが継続して動作できるようにした端末装置及び端末装置におけるメモリ制御方法を提供すること。

【解決手段】アプリケーションプログラムを記憶部に記憶させて前記アプリケーションプログラムを実行することで前記アプリケーションプログラムに対応するアプリケーションを動作させる端末装置において、省電力状態に移行するとき、前記アプリケーションの動作状況と属性に基づいて、前記アプリケーションプログラムが使用される前記記憶部における記憶領域を第1の記憶領域から前記第1の記憶領域より消費電力の少ない第2の記憶領域に移動させるよう前記記憶部を制御するアプリケーション制御部を備える。

(もっと読む)

情報処理装置及び半導体記憶装置

【課題】製造コストの低減に対して有利な情報処理装置及び半導体記憶装置を提供する。

【解決手段】実施形態によれば、ホスト装置と、前記ホスト装置にバスを介して接続された半導体記憶装置とを備える情報処理装置であって、前記ホスト装置は、メインメモリを備え、前記半導体記憶装置は、第1の論物変換テーブル及びデータを格納する不揮発性半導体メモリと、前記第1の論物変換テーブルの一部である第2の論物変換テーブルを格納する記憶部と、前記第2の論物変換テーブルを参照し前記不揮発性半導体メモリにアクセスする制御部とを備え、前記第1の論物変換テーブルの少なくとも一部が前記メインメモリ上にコピーされ、前記第2の論物変換テーブルに前記制御部がアクセスする論理アドレス又は物理アドレスが登録されていない場合、前記メインメモリ上の第3の論物変換テーブルの一部が前記第2の論物変換テーブルにコピーされる。

(もっと読む)

メモリ、メモリ上のプログラム書き換え方法及びプログラム

【課題】メモリ上のプログラム書き換え方法を提供する。

【解決手段】本発明のメモリは、書き換え対象プログラムを記憶する記憶部と、CPUにより実行される前記書き換え対象プログラムが、前記書き換え対象プログラムを読み出す際に参照する仮想アドレスと、物理アドレスとの対応を管理する読出アドレス管理部と、前記CPUにより実行される前記書き換え対象プログラムが、前記書き換え対象プログラムを書き換える際に参照する仮想アドレスと、物理アドレスとの対応を管理する書込アドレス管理部とを備え、CPU(プログラム)からアドレス切替信号契機で読出アドレス管理部および書込アドレス管理部を更新する方法を有する。

(もっと読む)

不揮発性メモリのページ管理方法

【課題】不揮発性メモリの論理−物理アドレス変換テーブルの更新量に影響されずに安定した性能でデータの書き込みができるアドレス変換テーブルの保存及び初期化の方法を提供する。

【解決手段】データ書き込みの度に、論理ページアドレス割り当て履歴144と呼ばれる領域に、物理、論理両方の書き込み先ページアドレスを追記し、一杯になると、論理ページアドレス割り当て履歴144と一緒に、等サイズに分割した論理−物理ページアドレス変換テーブル143の中から1つを、全領域を周回する形で不揮発性メモリに保存する。初期化時は、分割した論理−物理ページアドレス変換テーブル143を保存した順番通りに揮発性メモリに読み出し、読み出しの度に論理ページアドレス割り当て履歴144の内容を反映し、最後に前回の電源断直前に書き込んだデータの物理ページアドレスを反映することで、論理−物理ページアドレス変換テーブル143を復元する。

(もっと読む)

メモリシステム

【課題】 DRAMを用いずに、データの高速な読み出しが可能なメモリシステムを提供する。

【解決手段】 複数の不揮発性メモリ11は、複数のチャネルのそれぞれに接続され、複数のバンクを有している。バッファ17は、複数の不揮発性メモリから読み出されたデータを保持し、同時に読み出し可能なデータサイズのほぼ2倍の容量を有するスタティックメモリにより構成されている。複数のチャネル制御部16-0〜16-7は、複数の不揮発性メモリからデータを読み出すための読み出し要求を複数のチャネル毎に保持するキューを有している。バッファ制御部15は、読み出し要求を複数のチャネル制御部のいずれかのキューに供給するとともに、バッファ内に不揮発性メモリから読み出されたデータを保持するための領域を確保する。

(もっと読む)

半導体装置、不揮発性メモリ装置の制御方法

【課題】長寿命化などを実現できる半導体装置を提供する。

【解決手段】本半導体装置(メモリモジュールMM0)の制御回路(SC0)は、データ書込みの要求に対し、上書き可能な不揮発性メモリ装置(NVM)へのデータ書込みの際、上書き要求であっても上書き動作せずに、データの書込と消去のサイズを同じにして、メモリ(NVM)のアドレスを連続的に割当てて使用し、メモリ(NVM)の使用のバラツキを抑え平準化する仕組みにより、長寿命化などを実現する。制御回路(SC0)は、(a)第1のアドレスのデータの消去動作、またはフラグ値を無効に設定する動作と、(b)第1のアドレスとは別の第2のアドレスに対するデータの書込動作、またはフラグ値を有効に設定する動作との2種類の動作のセットによりデータ書込みを実現する。

(もっと読む)

制御装置、記憶装置、読出制御方法

【課題】不揮発性メモリの各論理ブロックの記憶状況確認のためのページ読み出しを効率化する。

【解決手段】同時読出可能な第1〜第nの不揮発性メモリのそれぞれの物理ブロックを含んで形成される論理ブロックについて、各論理ブロック毎に、論理ブロックの記憶状況確認のために読み出す対象となる確認読出対象ページ(例えば先頭論理ページ)が上記第1〜第nの不揮発性メモリの物理ページに分散配置されるように各論理ブロックの論理ページを管理する。そして各論理ブロックのそれぞれから確認読出対象ページを読み出す際には、第1〜第nの不揮発性メモリへの並列的なアクセス制御により、複数の論理ブロックの確認読出対象ページの同時的な読み出しを実行する。

(もっと読む)

メモリシステムおよびプログラム

【課題】論物変換テーブルのサイズを低減可能なメモリシステムおよびプログラムを提供する。

【解決手段】実施形態のメモリシステムは、複数のブロックをそれぞれが有する複数の半導体メモリと、第1テーブルと、受信部と、作成部と、第2テーブルと、書き込み部とを備える。第1テーブルは、各ブロックにそれぞれ対応するとともに欠陥情報が記憶される複数の記憶領域を有する。作成部は、第1テーブルの複数の行のうちの何れかを示すインデックス番号と、第1テーブルとに基づいて、半導体メモリごとに、データの書き込みが行われるブロックを1つずつ選択してブロックの組を作成する。第2テーブルは、論理アドレスごとに、インデックス番号と、チャネル番号とを対応付けて記憶する。書き込み部は、受信部で書き込みコマンドを受信した場合、組を構成する複数のブロックのうち、選択したチャネル番号に対応するブロックに対して、データを書き込む。

(もっと読む)

メモリシステム、不揮発性記憶装置及びその制御方法

【課題】読み出し動作を高速化し、かつ書き込みに利用可能なフリーブロックを増加させる。

【解決手段】メモリシステム1は、不揮発性記憶装置3と情報処理装置2とを有する。情報処理装置2は、不揮発性記憶装置3の第1の論理アドレス領域からデータを読み出し、第1の論理アドレス領域に対応する読み出しデータが関数で表されるデータと同じである場合に、不揮発性記憶装置3に、第1の論理アドレス領域のデータを無効にするための削除通知を行う第1の制御回路を含む。不揮発性記憶装置3は、有効なデータに対応する論理アドレスと物理アドレスとを関連付ける管理テーブルと、削除通知により指定された論理アドレスを無効にするように管理テーブルを書き換え、情報処理装置2から受信した読み出し命令に含まれる論理アドレスが無効である場合に、関数で表されるデータを情報処理装置2に送信する第2の制御回路とを含む。

(もっと読む)

光ディスク記録再生用半導体集積回路およびその動作方法

【課題】特殊な記録動作や特殊な再生動作への対応を容易とすること。

【解決手段】半導体集積回路は、再生ECC回路18と記録ECC回路17とホストインターフェース回路19とメモリ制御回路20を具備して、メモリ制御回路20は調停回路200とカウント回路202を含む。事前設定の優先順位で調停回路200は、ECCアクセスをホスト機器2とのホストインターフェースのアクセスより高い優先順位で調停する。カウント回路202はECCリクエストの出力回数をカウントして、カウント出力回数が動作モードの所定の出力回数と一致すると、カウント回路202はカウント終了信号を生成する。調停回路200では優先順位の切り替えが実行され、ECCよりもホストを高い優先順位で調停される。所定の出力回数は、1個のECCブロック又はその整数倍のデータに関係して半導体メモリ22のアクセスに必要なECCアクセスリクエストの出力回数に対応する。

(もっと読む)

記憶装置

【課題】非選択データの冗長な書き込み操作を不要とでき、ページの配列を書き換えに効率の良い状態に最適化することが可能な記憶装置を提供する。

【解決手段】並列にアクセス可能な2チップのフラッシュメモリ35,36と、フラッシュメモリ35,36から並列にデータを取得し、一時記憶するページレジスタ32と、ページレジスタ32に並列格納されるデータ単位で論理アドレスと物理アドレスとの対照を管理するアドレス変換テーブルが構築されたRAM37を内蔵した制御回路34と、を有し、アドレス変換テーブルの更新と記憶メディアへの追記によってデータ書き換えを行う。

(もっと読む)

仮想メモリシステム、仮想メモリの制御方法、およびプログラム

【課題】書換え回数の制限のある不揮発性メモリに対するアクセスにおいてアプリケーションからは書込み制限を回避することが可能な仮想メモリシステム、仮想メモリの制御方法、およびプログラムを提供する。

【解決手段】仮想メモリシステム10は、ランダムアクセス可能で、書換え回数に上限があり、物理アドレス空間へのアクセスが仮想アドレスを介して行われる不揮発性メモリ40と、不揮発性メモリ40の物理アドレス空間をページ単位で管理し、物理アドレス空間と仮想アドレス空間をマッピングし、アクセスのあった仮想アドレスを物理アドレスに変換する機能を含む仮想メモリ制御部20と、を有し、仮想メモリ制御部20は、書換えが発生する仮想ページに割り当てる物理メモリ容量を拡張する機能を含む。

(もっと読む)

マルチチャネルを有するメモリ装置及び同装置におけるメモリアクセス方法

【課題】ブロック単位のメモリアクセス処理を、小容量のメモリ領域を用いた管理で高速に実行できるようにする。

【解決手段】実施形態によれば、コマンド生成手段は所定のアクセス処理において、チャネル別のアクセスコマンドの群をメモリインタフェースに逐次投機的に投入する。パージ手段は、複数のチャネルを介してのメモリアクセスのいずれかでエラーが発生した場合、既に投入されている未実行のアクセスコマンドの系列を返却する。コマンド進捗管理手段は、各チャネルにおけるコマンド進捗が、返却された未実行のアクセスコマンドの系列のうちの最も古い未実行のアクセスコマンドの指定する位置を指すようにコマンド進捗情報を更新する。コマンド生成手段は更新された情報に基づき、チャネル別のアクセスコマンドの群をメモリインタフェースに投入する。

(もっと読む)

記憶装置およびそれを搭載した計算機

【課題】記憶装置に搭載するメモリ容量を削減しながら、情報を書き込む際の処理速度の低下を最低限に抑える。

【解決手段】不揮発性メモリ内に、論理/物理アドレス変換テーブルをページ単位に分割した複数の分割変換テーブルを保存し、RAM内には、分割変換テーブルの少なくとも1つ以上を保存する論理/物理アドレス変換テーブルキャッシュと、分割変換テーブルを管理する変換テーブル管理テーブルと、論理/物理アドレス変換テーブルキャッシュの管理を行うキャッシュ管理テーブルを保存し、変換テーブル管理テーブルは、分割変換テーブルが前記論理/物理アドレス変換テーブルキャッシュに保存されていることを示すキャッシュ有無フラグと、前記論理/物理アドレス変換テーブルキャッシュ内での保存先を示すキャッシュエントリ番号を有し、不揮発性メモリと前記RAMの間における前記論理/物理アドレス変換テーブルの情報の読み出し及び書き込みは、ページ単位で行う。

(もっと読む)

不揮発性半導体記憶装置及びデータ処理システム

【課題】キャッシュ機能を用いないで、不揮発性半導体記憶装置における小容量書込みの高速化を図る。

【解決手段】本発明の代表的な実施の形態に係る不揮発性半導体記憶装置(1)は、ホストシステム(2)に接続可能とされ、不揮発性記憶部(11)と、その動作制御を行うコントローラ(12)とを含む。上記コントローラは、論理アドレスと物理アドレスとの対応関係を、上記ホストシステム側のアクセス単位と、上記不揮発性記憶部側のアクセス単位とに分けて管理し、上記ホストシステムからの書込み指示に係るデータのサイズに応じて、上記ホストシステム側のアクセス単位での管理と、上記不揮発性記憶部側のアクセス単位での管理とを判定し、上記不揮発性記憶部における対応領域にデータを書込むことで、バッファメモリへのデータ退避を不要とする。

(もっと読む)

メモリ装置およびメモリシステム

【課題】書き込み時の論理アドレスによらず書き込み速度を低下させずデータを書き込むことが可能で低消費電力化が可能なメモリ装置およびメモリシステムを提供する。

【解決手段】メモリコントローラ200は、論物変換テーブル204を持ち、消去済みの物理ブロックアドレスとその不揮発性メモリ、不揮発性メモリ毎の消去済みの物理ブロック数を管理する消去済み物理ブロック管理部206と、消去可能物理ブロックアドレスとその不揮発性メモリ、不揮発性メモリ毎の消去可能の物理ブロック数を管理する消去可能物理ブロック管理部205と、メモリ制御部207と、を含み、メモリ制御部は、消去済み物理ブロック管理部で管理される一の不揮発性メモリの第1の物理ブロックにデータの書き込みを行い、書き込みと並行して消去可能物理ブロック管理部で管理される他の不揮発性メモリの第2の物理ブロックの消去を行う。

(もっと読む)

半導体記憶装置

【課題】管理情報を記憶するランダムアクセス可能なメモリの記憶容量を増大させることなく、ランダムリード及びランダムライト性能を向上させる。

【解決手段】実施形態においては、ランダムアクセス可能な第1の半導体メモリに含まれる第1の記憶部と、ページ単位で読み出し及び書き込みが行われ、ページより大きなブロック単位で消去が行われる不揮発性の第2の半導体メモリに含まれる第2の記憶部と、第2の半導体メモリの記憶領域を、ブロック単位で前記第2の記憶部に割り当てるコントローラと、第2の記憶部のデータを第1の管理単位で管理するための第1の管理テーブルであって、第2の半導体メモリに記憶される第1の管理テーブルと、第2の記憶部のデータを第1の管理単位より大きな第2の管理単位で管理するための第2の管理テーブルであって、第1の半導体メモリに記憶される第2の管理テーブルとを備える。

(もっと読む)

1 - 20 / 277

[ Back to top ]