Fターム[5B060AC15]の内容

Fターム[5B060AC15]に分類される特許

1 - 9 / 9

メモリアクセス制御装置、プロセッサ及びメモリアクセス制御方法

【課題】メモリアクセス制御装置におけるメモリ帯域の利用効率をさらに向上させる。

【解決手段】命令発行部311は、RAM11に格納された要素データにアクセスするメモリアクセス命令を発行する。監視部231は、RAM11に対するアクセスの混雑度を監視する。保持部324は、監視部231で監視された混雑度に応じて検出されたメモリアクセス命令を保持する。生成部325は、保持部324に保持されたメモリアクセス命令のうち、所定の条件を満たす複数のメモリアクセス命令を圧縮してアクセスリクエストを生成する。リプライデータ処理部331は、生成部325で生成されたアクセスリクエストに対するリプライデータを、圧縮前の複数のメモリアクセス命令各々のリプライデータに分解する。

(もっと読む)

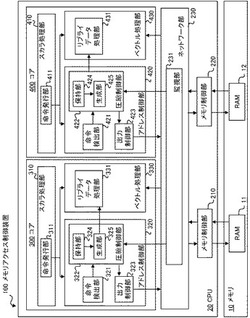

情報処理装置、メモリアクセス制御装置及びそのアドレス生成方法

【課題】アクセス単位が複数ワード長の記憶部を利用しながらアクセス時間を短縮する。

【解決手段】情報処理装置1は、アクセス要求を出力する演算部10と、複数の接続ポートと、同時並行処理が可能な複数のメモリとを備え、接続ポートに対するアクセス単位が複数ワード長の記憶部20と、演算部10から処理サイクル毎に受信する前記アクセス要求に対応する複数のアクセスアドレスを複数の接続ポートに振り分けて、1アクセス単位に演算部10の異なる処理サイクルに属する不連続なワードを含むポート内アドレスを接続ポート毎に生成するメモリアクセス制御部40と、を有する。

(もっと読む)

データ転送装置、演算装置、それを備えた装置およびデータ転送方法

【課題】 データ転送装置から記憶装置へのデータ転送のスループットを向上する。

【解決手段】 データ転送装置1は、複数の一時保存部2(21,・・・2n(nは2以上の整数))と、順序制御部3と、データ読み出し部4と、転送制御部5とを有する。各一時保存部2(21,・・・2n)は、転送先の格納位置を示すアドレス情報付きのデータが入力されるデータ入力部6を通ってデータ転送装置1に入力したデータを保存する。データ読み出し部4は、各一時保存部2から、並列に、データを読み出す。転送制御部5は、その読み出された各データを、当該データに添付されているアドレス情報に基づいた転送先に対応しているデータ出力部7に出力する。順序制御部3は、各一時保存部2から並列に読み出される各データの転送先に対応するデータ出力部7が互いに異なるように、一時保存部2毎にデータの読み出し順を設定する。

(もっと読む)

情報処理装置

【課題】命令で指定したアドレス間隔で記憶された複数の要素データを1命令でアクセスできるベクトルロード命令のようなメモリアクセス命令を、圧縮メモリアクセスリクエストを用いて処理する場合のプロセッサ内での処理量を削減すること。

【解決手段】命令発行制御部110の圧縮可否判定部130は、命令で指定したアドレス間隔で記憶された複数の要素データを1命令でアクセスできるメモリアクセス命令が、メモリバンク210のバンク幅内の複数の要素データをアクセスするか否かを判定する。圧縮メモリアクセスリクエスト生成発行部140は、メモリバンク210のバンク幅内の複数の要素データをアクセスする命令について、メモリバンク210のバンク幅単位で、当該バンク幅の複数の要素データをアクセスするための圧縮メモリアクセスリクエストを生成し、発行する。

(もっと読む)

双極子相互作用の高速演算装置と演算方法

【課題】双極子間の相互作用を高速に演算できる技術を提案する。

【解決手段】高速演算装置を構成する複数の演算装置のそれぞれが、独立かつ並列に演算を実行できるように記述された動作ユニットに基づいて動作する仕組みを提案する。この動作ユニットは、各動作ユニットがデータの読み書きに使用するアドレス範囲をアクセス不可領域として他の動作ユニットに通知する仕組みを提案する。

(もっと読む)

アドレス変換回路、ベクトル処理装置、ベクトル処理システム、および、アドレス変換方法

【課題】アドレス変換の性能が低い。

【解決手段】アドレス変換回路100は、1つのベクトル命令に対し論理アドレスから物理アドレスへのアドレス変換を1回のみ行い物理ベースアドレスを生成し、その後、前記物理ベースアドレスに要素間距離を順次加算し、物理アドレスを順次生成する。

(もっと読む)

改良された置換可能なアドレス・プロセッサ及び方法

幾つかの異なったデータ・フォーマットを処理するようプロセッサを適応させることは、第1の記憶装置からの第1のフォーマットにデータ・ワードをロードすることと、それが算術ユニットに達する前に、データ・ワードの第1のフォーマットを、算術ユニットの本来の順番と両立し得る第2のフォーマットに再順番付けすることと、算術ユニットにおいてデータ・ワードをベクトル処理することと、を含む。  (もっと読む)

(もっと読む)

情報処理装置、情報処理システム、DMAコントローラおよび情報処理方法

【課題】間接ベクトル参照を行う場合の処理効率を向上させることのできる情報処理装置を提供する。

【解決手段】データへのアクセスに利用されるインデックス列を記憶するインデックス列記憶手段112と、インデックス列記憶手段112からインデックス列を取得し、FIFO方式により前記インデックス列を順次出力するFIFOバッファ120と、FIFOバッファ120からインデックス列を順次取得すると、インデックス列に基づいて、データを記憶するデータ記憶手段114への不連続なアクセスを行うための不連続アドレス列を生成するアドレス生成手段130と、アドレス生成手段130によって生成された不連続アドレス列に基づいてデータ記憶手段114にアクセスするアクセス手段130とを備えたことを特徴とする。

(もっと読む)

半導体信号処理装置

【課題】 大量のデータを高速で効率的に演算処理する処理装置を実現する。

【解決手段】 主演算回路(20)に対する演算処理命令を、マイクロ命令メモリ(21)にマイクロプログラムの形態で格納し、このマイクロプログラムに従ってコントローラ22の制御の下に主演算回路の動作制御を実行する。主演算回路(20)においてはメモリセルマット(30)が、それぞれが複数ビットのデータを格納するエントリに分割され、各エントリに対応して演算器(ALU)が配置される。エントリとALUとの間で、ビットシリアル態様で各エントリ並列に演算処理を実行する。マイクロプログラム制御方式に従って効率的に大量のデータを処理することができる。

(もっと読む)

1 - 9 / 9

[ Back to top ]