Fターム[5B060MB08]の内容

Fターム[5B060MB08]に分類される特許

1 - 20 / 43

半導体装置

【課題】データ用電流パスの占有面積を最小化し、かつ動作速度の低下も抑制する。

【解決手段】半導体装置10は、互いに積層されたインタフェースチップIF及び複数のコアチップと、インタフェースチップIFと複数のコアチップのそれぞれとを接続するデータ用電流パスとを備え、インタフェースチップIFは、複数のコアチップに対して同時にリードコマンドを供給するコマンドデコーダ32を有し、複数のコアチップはそれぞれ、メモリセルアレイ50と、当該コアチップに割り当てられた層アドレスLIDを記憶する層アドレス発生回路46と、リードコマンドに応じてメモリセルアレイ50からリードデータを読み出し、層アドレス発生回路46に記憶される層アドレスLIDに応じたタイミングで、上記データ用電流パスを介してインタフェースチップIFに出力するデータコントロール回路54とを有する。

(もっと読む)

半導体装置

【課題】データ処理性能の低下を防止可能な半導体装置を提供すること。

【解決手段】本発明にかかる半導体装置は、インターフェイス回路105−1,105−2と、インターフェイス回路105−1に第1のデータバスを介して結合されると共に、インターフェイス回路105−1から出力される第1のアクセス制御信号に結合されたメモリコア106−1と、インターフェイス回路105−2に第2のデータバスを介して結合されたメモリコア106−2と、第1のアクセス制御信号、又は、インターフェイス回路105−2から出力される第2のアクセス制御信号を選択的にメモリコア106−2に結合させる選択回路107−1と、を備える。

(もっと読む)

情報処理装置および方法、並びにプログラム

【課題】より効率的に処理を実行できるようにする。

【解決手段】制御部は、データをnビット単位でアクセスし、記憶部は、mビット単位の管理データを複数個組み合わせてnビットになるように、管理データを記憶し、変換部は、制御部が管理データにアクセスする場合、mビット単位の管理データをnビット単位の管理データに仮想的に変換する。

(もっと読む)

メモリアクセス制御回路およびメモリアクセス制御方法

【課題】簡易にスイッチングノイズを低減することができるメモリアクセス制御回路およびメモリアクセス制御方法を提供する。

【解決手段】バーストアクセス方式のメモリアクセス制御回路であって、第1バス幅で入力される入力データの連続する前後2つのデータを比較して互いに異なるビットの数を検出する検出手段120と、検出手段が検出した異なるビットの数が閾値を超えたかどうかを判定する判定手段130と、判定手段が閾値を超えたと判断したとき、閾値を超えたと判断されたデータを含む入力データを予め定めた単位で保持するデータ保持手段140と、データ保持手段により保持される入力データの第1バス幅を第2バス幅とすることにより入力データを分割するデータ分割手段140と、データ分割手段により分割された入力データを段階的に出力するデータ出力手段140、150と、を有する。

(もっと読む)

メモリアクセス装置

【課題】ビット幅の異なるメモリへのアクセス性能を高めることができる、メモリアクセス装置を提供する。

【解決手段】カウンタ24は、7個のカウント値をモード情報“MD32”に対応して出力する一方、15個のカウント値をモード情報“MD16”に対応して出力する。分配器26および結合器28は、カウンタ24から出力されたカウント値を1/2の値に変換する。セレクタ32は、カウンタ24から出力されたカウント値に基づく加算値をモード情報“MD32”に対応して生成する一方、結合器28から出力された数値に基づく加算値をモード情報“MD16”に対応して生成する。SDRAMに設けられた複数のアドレスの各々は、32ビットおよび16ビットのいずれか一方に相当するビット幅を有する。F/F回路36は、このようなSDRAMへのアクセスのために、セレクタ32によって選択されたカウント値を統合アドレスとして出力する。

(もっと読む)

メモリシステム

【課題】

実施形態は、複数のバッファ部それぞれに保持されたデータを交換可能なメモリシステムを提供する。

【解決手段】

本実施形態のメモリシステムは、データを保持可能なページバッファを含むNAND型フラッシュメモリと、前記NAND型フラッシュメモリとデータバスを介して電気的に接続された複数の記憶部と、前記NAND型フラッシュメモリ、前記複数の記憶部を制御する制御部とを備え、前記データバスの幅は、前記データの容量よりも小さく、前記制御部は、前記NAND型フラッシュメモリに書き込み又は読み出しを行うとき、前記ページバッファに保持するデータと前記複数の記憶部のうち1の記憶部に保持するータとを交換することを特徴とする。

(もっと読む)

入出力制御装置、及び情報処理装置

【課題】未使用の記憶領域の生成を防ぐ

【解決手段】第1処理装置、第2処理装置、第1記憶装置、及び第2記憶装置に対してデータを入出力する入出力制御装置であって、第1処理装置が出力する第1データを分割するデータ分割部と、分割した第1データを、第1記憶装置及び第2記憶装置にそれぞれ格納するとともに、第2処理装置が出力し且つ第1データよりビット数が少ない第2データを、第1記憶装置及び第2記憶装置の何れか1つに格納する格納制御部と、を備える入出力制御装置が提供される。

(もっと読む)

シリアルメモリ・コントロールシステム、方法およびプログラム

【課題】初期的に設定されるアドレスモード以外のモードでシリアルメモリ・コントローラがリセットされたとき、リセット端子を持たないシリアルメモリとの間でモードの一致を採ることのできるシリアルメモリ・コントロールシステム、方法およびプログラムを得ること。

【解決手段】リセット検出手段13は、シリアルメモリ・コントローラ12がリセットされたことを検出すると、再起動手段14を用いてシリアルメモリ11を再起動する。同期を採るためのクロックが断になったときシリアルメモリ11を再起動してもよい。

(もっと読む)

データ処理システム及びその制御方法

【課題】多彩なバースト動作が可能なデータ処理システムを提供する。

【解決手段】それぞれが複数のデータを有する複数のブロックA〜Dを有する第1の半導体装置210と、第1の半導体装置を制御する第1の制御回路310を有する第2の半導体装置300と、を備え、第1の制御回路は、異なるデータの数をそれぞれ示す複数のバースト長を定義する複数の第1の定義、及び複数のブロックがそれぞれ有する複数のデータの一部の複数のデータと複数のバースト長をそれぞれ構成する異なるデータの数の中の配列の順序との対応付けをそれぞれ定義する複数の第2の定義、を含む複数のアクセス単位で、第1の半導体装置と通信する複数のコマンドを発行し、第1と第2の定義に従った異なるデータの数の複数のデータで、第1の半導体装置と通信する。

(もっと読む)

データ処理装置

【課題】データ転送処理に関して、効率良くアクセスを行うかによって、システム全体の性能を上げる技術を提供する。

【解決手段】内蔵メモリ(2)と、マスタデバイス(6−1〜6−n、7)から渡されたデータをその内蔵メモリ(2)に転送するメモリコントローラ(3)とを具備するデータ処理装置(1)を構成する。ここで、その内蔵メモリ(2)は、第1データバス幅のデータに対応した第1内蔵メモリと、その第1内蔵メモリと独立に動作する第2内蔵メモリとを含むことが好ましい。そして、そのメモリコントローラ(3)は、そのマスタデバイス(6−1〜6−n、7)から供給されたデータのデータバス幅が、その第1データバス幅を超えるとき、その第1内蔵メモリとその第2内蔵メモリとをあわせて単一のメモリデバイスとして機能させる。

(もっと読む)

半導体記憶装置及びこれを備える情報処理システム

【課題】複数のコアチップとインターフェースチップからなる半導体記憶装置において、I/O構成の切り替えを容易とする。

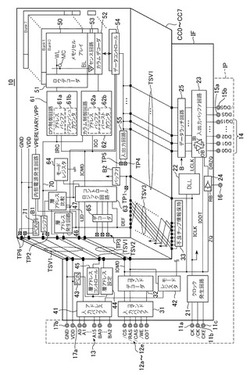

【解決手段】互いに異なるチップ識別情報LIDが割り当てられた複数のコアチップCC0〜CC7と、コアチップCC0〜CC7を制御するインターフェースチップIFとを備える。インターフェースチップIFは、外部との間で同時に入出力する単位外部データのビット数が可変であり、チップ識別情報LIDと比較するためのチップ選択情報SELを、単位外部データのビット数に応じて可変とする。これにより、I/O構成の変更に伴うページ構成の切り替えを不要とすることが可能となる。

(もっと読む)

直列入力データを取り込む装置および方法

【課題】直列入力データ処理装置は、コマンド解釈をコマンドデコーダで高周波数にて行いながら、1ビットの損失もなく直列データを取り込む方法を提供する。

【解決手段】定義済みシーケンスによる直列ビットの個々のバイトがラッチされ、ビットストリームが複数クロックと共に一時格納される。この一時格納は、アドレスを登録するために割り当てられたアドレスレジスタにバイト情報を転送する前に行われる。アドレス登録とデータ登録は、複数クロックの立ち上がり区間で直列入力の全ビットストリームをラッチすることにより実行される。高周波操作時(例えば、1GHzまたは1ナノ秒サイクル時間)においては、コマンドビットストリーム解釈と次のビットデータストリームの間に十分な時間的余裕をもってコマンド解釈中にビットデータを格納する目的のために追加レジスタが要求されることはない。

(もっと読む)

データ処理装置、データ処理方法、およびデータ処理プログラム

【課題】レジデントメモリが接続されたCPUに対して、レジデントメモリのバス幅よりも大きいバス幅を有する増設メモリが接続された場合、増設メモリにおける従来未使用の部分を有効に活用する。

【解決手段】メモリにアクセスする際のバス幅を32ビットのバス幅と64ビットのバス幅とに切り替え可能であり32ビットのバス幅を有するレジデントメモリが接続されたCPUに対して、64ビットのバス幅を有するDIMMが接続された場合(S101:YES)、画像処理装置は、32ビットのバス幅を使用してCPUがアクセス可能なメモリ容量と64ビットのバス幅を使用してCPUがアクセス可能なメモリ容量とを比較し(S104)、比較の結果に基づいて、32ビットのバス幅および64ビットのバス幅のうち、CPUがアクセス可能なメモリ容量が大きくなる方のバス幅を使用することを決定する(S107、S105)。

(もっと読む)

メモリモジュール及びデータ入出力システム

【課題】メモリモジュールの制御に必要とされる制御信号を最小化することができるメモリモジュール及びデータ入出力システムを提供する

【解決手段】本発明に係わるメモリモジュールは、第1メモリチップが装着された第1ランク及び第2メモリチップが装着された第2ランクを備えており、前記第1メモリチップは、第1データ出力モードに設定された場合、複数のデータのうち、既に設定された下位順番のデータを下位データ出力ピンを介して外部に出力し、前記第2メモリチップは、前記第1データ出力モードに設定された場合、複数のデータのうち、前記下位順番と同じ順番のデータを上位データ出力ピンを介して外部に出力するように構成されることを特徴とする。

(もっと読む)

構成可能な仮想ページサイズを有するブリッジデバイス

ディスクリートメモリデバイスと、該デバイスを制御するブリッジデバイスとを備える複合メモリデバイス。ブリッジデバイスは、いくつかのバンクとして編成されたメモリを有し、各バンクは、ページバッファの最大物理的サイズより小さい仮想ページサイズを有する。ページバッファに格納される仮想ページサイズに対応するデータのセグメントのみがバンクに転送される。バンクの仮想ページサイズは、順序付けられた構造を有する仮想ページサイズ(VPS)コンフィギュレーションコマンドで供給され、コマンド内にVPSコンフィギュレーションコードを含むVPSデータフィールドの部分は、最下位バンクから最上位バンクへと順序付けられている異なる複数のバンクに対応する。VPSコンフィギュレーションコマンドは可変サイズであり、最高位のバンク及びそれより低い下位バンクに対するVPSコンフィギュレーションコードのみを含む。  (もっと読む)

(もっと読む)

マルチモードメモリデバイス及び方法

メモリデバイスシステム、システム、及び方法が開示されており、これらは、複数の導電体を介して互いに接続された、複数の積層されたメモリデバイスダイ及びロジックダイを含んでいる。ロジックダイは、プロセッサ等のメモリアクセスデバイスに対するメモリインターフェースデバイスとして動作する。ロジックダイは、2つのモードのうちのいずれかでの選択的な動作を可能にするコマンドレジスタを含み得る。直接モードでは、行及び列アドレス信号と共に一般的なコマンド信号がロジックダイに与えられ、ロジックダイは、本質的に、これらの信号をメモリデバイスダイに直接的に結合し得る。間接モードでは、コマンド及び複合アドレスを含んだパケットがロジックダイに与えられ、ロジックダイは、これらのコマンド及び複合アドレスをデコードして、一般的なコマンド信号並びに行及び列アドレス信号をメモリデバイスダイに与え得る。 (もっと読む)

増設メモリのアクセス方法、電子装置、およびメモリモジュール

【課題】電子装置の増設メモリとして、少なくとも電子装置の内部バスの2倍以上のバス幅のデータ入出力端子を有したメモリモジュールを使用する。

【解決手段】増設メモリスロット3のデータ入出力部を所定ビット幅で区分した複数のセグメントを、入出力すべきワードデータを収容するセグメントを単位として並列に、メモリ制御手段6に接続し、このメモリ制御手段6は、ワードデータを特定する信号をデコードして、前記複数のセグメントから、その信号に割り当てられたワードデータを収容させるべきセグメントを除外したマスク信号を生成するデコード手段4を備え、生成したマスク信号を、アドレスと共に増設メモリスロット3に伝送する。

(もっと読む)

データ信号処理装置、画像処理装置、画像出力装置、および、データ信号処理方法

【課題】バスのプロトコルに応じてデータ信号を変換する場合にメモリ資源の浪費を抑制する。

【解決手段】データ信号処理装置は、第1のプロトコルに従ってデータ信号を伝送する第1のバスと、第2のプロトコルに従ってデータ信号を伝送する第2のバスと、第1のバス上に伝送される第1のデータ信号を第2のバス上に伝送される第2のデータ信号に変換する変換部と、を備える。変換部は、第1のバスを介して第1のデータ信号の供給を受け、第1のデータ信号の供給に同期して、第2のバスに前記第2のデータ信号を出力する。

(もっと読む)

1つもしくはそれ以上のメモリ装置を有するシステム

【解決手段】 高速性能を実現するためリンクトポロジー構成で直列に接続されたメモリ装置を有するシステム。

性能を最大限にするためシステムが最大の共通の数のアクティブデータパッドまでで動作することができ、あるいは消費電力を最小限にするためシステムが単一のアクティブデータパッドで動作することができるように、メモリ装置は動的に構成可能なデータ幅を有する。それ故、システムは、異なるデータ幅を有するメモリ装置の混合を含むことができる。メモリ装置は、ブロードキャスト動作でメモリコントローラからすべてのメモリ装置を介して直列に伝播される単一のコマンドの発行を通じて動的に構成され得る。システムの堅牢な動作は、データ出力禁止アルゴリズムを実施することによって保証され、このアルゴリズムは、読出し出力制御信号が適切なシーケンスから受け取られたとき、有効なデータがメモリコントローラに提供されることを抑制する。

(もっと読む)

データ・アクセスおよびマルチチップ・コントローラ

【課題】アクセス・インタフェースの信号品質を改善し、製造費を低減すること。

【解決手段】記憶装置への単一のデータ・バスは、複数のデータ・バス部分に分割されることができ、その各々は、複数のコントローラ・チップの異なる各々のコントローラ・チップによって管理される。各々の記憶装置へのメモリ・アクセス中に、複数のコントローラ・チップの各々は、データ・バスの異なる対応する部分を制御し、その結果、アクセスが読取りまたは書込みであるか否かに依存して、記憶装置からデータを読み取るか、または、記憶装置にデータを格納する。データ・アクセスを行なうために、シンクロナイザ回路は、複数のメモリ・コントローラ・チップを同期させ、その結果、メモリ・コントローラ・チップのうちの1つが、記憶装置へのアドレス・バスおよび/または制御信号を駆動する。

(もっと読む)

1 - 20 / 43

[ Back to top ]