Fターム[5B060MM02]の内容

メモリシステム (7,345) | メモリモジュール構成、管理技術 (856) | メモリモジュール構成/制御 (384) | ROMとRAMの混在 (154)

Fターム[5B060MM02]に分類される特許

1 - 20 / 154

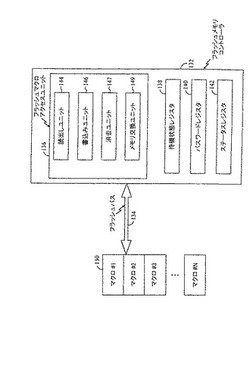

集積化埋込型フラッシュ及びSRAMメモリを有する移動通信装置

【課題】フラッシュ及びSRAMのアクセス時間を改善し、ASICを使用する移動電話機のパワー消費を低減する。

【解決手段】改善されたアクセス時間を備えるフラッシュ及びSRAMメモリを特定用途集積回路(ASIC)の中に埋込む。フラッシュメモリシステムは、個々のフラッシュマクロの組及びフラッシュマクロにアクセスするためのフラッシュメモリコントローラ132を備えるように構成されたフラッシュメモリ列130を含む。フラッシュメモリコントローラは、フラッシュマクロの一つへ、同時にフラッシュマクロの他の一つから読出している間に、書込むための読出し間書込みユニット144,146を含む。フラッシュメモリコントローラは、また、プログラム可能な待機状態レジスタ138及びフラッシュメモリ列の異なる部分のための別々のパスワードを提供するパスワードレジスタ140を含む。

(もっと読む)

集積化埋込型フラッシュ及びSRAMメモリを有する移動通信装置

【課題】ブートローダは、他のデータ及びプログラムが、より適切にアクセスされることができる下位のメモリの中に記憶されることができるような、上位のメモリに交換されるフラッシュメモリシステムを提供する。

【解決手段】フラッシュメモリセルをハイメモリロケーションおよびロウメモリロケーションに区分するための手段が設けられたフラッシュメモリセル及びフラッシュメモリコントローラ132を含む。フラッシュメモリセルは、フラッシュメモリ空間の最下位のメモリアドレスで始まるブートローダを記憶する。区分するための手段は、ブートローダによって実行された動作が完了してしまった後にハイメモリロケーションとロウメモリロケーションを交換するための手段を含む。メモリ交換ユニット149は、ブートローダによって実行される動作の完了に引続いてハイメモリおよびロウメモリを交換するために設けられる。

(もっと読む)

メモリシステム

【課題】不正な電源断やデータ破壊を簡便かつ確実に検出することが可能なメモリシステムを提供する。

【解決手段】実施形態のメモリシステムは、揮発性の第1の記憶部と、不揮発性の第2の記憶部と、データ管理部と、復元制御部と、を備える。前記データ管理部は、前記第1の記憶部に記憶されている前記管理テーブルの更新前後の差分情報である差分ログを並列書き込み処理によって多重化して前記第2の記憶部に記憶させた後、書き込み単位分の所定データを最終書き込み単位分データとして多重化して前記第2の記憶部に記憶させる。前記復元制御部は、前記第2の記憶部に記憶された差分ログおよび前記最終書き込み単位分データのデータ記憶状態に基づいて、前記差分ログを前記第2の記憶部に記憶させる際に不正電源断が発生したか、または前記第2の記憶部でデータ破壊が発生したかの状態判断をシステム起動時に行う。

(もっと読む)

通信装置およびICカード、通信システム

【課題】効率的に不揮発メモリへの記録処理を行うこと可能な通信装置およびICカード、通信システムを提供する。

【解決手段】通信システムはICカードと通信装置とを有する。ICカードは、揮発メモリと、不揮発メモリと、アプリケーションを実行する演算処理手段とを備える。通信装置は、前記ICカードに電力を供給する電源部と、前記電源部の電池残量に関する情報を出力する電源管理手段と、前記電池残量に関する情報に応じて前記揮発メモリあるいは前記不揮発メモリに情報を記憶するように制御する制御コマンドを前記ICカードに送信するように制御する制御手段とを有する。前記演算処理手段は、前記制御コマンドを受信すると、前記アプリケーションの実行により生成された情報を前記揮発メモリあるいは前記不揮発メモリに記憶するように制御する。

(もっと読む)

半導体装置

【課題】 ランダムアクセス時間が早く、大容量、低コストかつ高セキュリティを保つメモリモジュールを提供する。

【解決手段】 ランダムアクセスメモリと、不揮発メモリと、ランダムアクセスメモリおよび不揮発メモリに接続され、ランダムアクセスメモリおよび不揮発モリへのアクセスを制御する制御回路と、を有する半導体装置であって、制御回路からランダムアクセスメモリへの読み出し要求のサイクル時間は、半導体装置の外部から制御回路への読み出し要求のサイクル時間よりも短く、制御回路は、半導体装置の外部から制御回路への読み出し要求のサイクル時間のうち、制御回路からランダムアクセスメモリへの読み出し要求のサイクル時間を除いた時間で、不揮発メモリからランダムアクセスメモリへのデータ転送を行うことを特徴とする。

【効果】 高速なデータの読み出しが可能な高セキュリティを保った大容量、低コストのメモリモジュールが実現できる。

(もっと読む)

メモリを内蔵したマイクロプロセッサ

【課題】プログラムをメモリに転送して動作させるマイクロプロセッサでは、通常動作と特殊動作で使用するメモリの容量が異なるが、メモリ全体に電力を供給していたので、消費電力が増大するという課題があった。本発明ではメモリの消費電力を低減することができるマイクロプロセッサを提供することを目的にする。

【解決手段】メモリを独立して電源が供給できる複数のメモリ領域に分割し、使用するメモリ領域にのみ電源を供給するようにした。マイクロプロセッサの消費電力を低減できる。

(もっと読む)

データ処理装置および制御装置並びにデータ記憶装置

【課題】消費電力をより低減させる。

【解決手段】書き込みデータDが高書き換えデータであるときにはDRAMに書き込みデータDが記憶されるようDRAMを制御し(ステップS100,S110)、書き込みデータDが高書き換えデータでないときにはRRAM書き込み要求信号と書き込みデータDとをSSDに送信し(ステップS100,S120)、RRAM書き込み要求信号が入力されたSSDのメモリコントローラは書き込みデータDがRRAMまたはSRAMに記憶させられるようRRAM,SRAMを制御する。こうすれば、DRAMに記憶されているデータが頻繁に書き換えられることになり、DRAMのリフレッシュ動作の回数を低減して、消費電力の低減を図ることができる。

(もっと読む)

ICカード

【課題】端末の要求に応じて実行されている一連の処理が途中で中断された場合であっても、適切に処理を再開可能なICカードを提供する。

【解決手段】ICカードは、電力を受信する電力受信手段と、端末と通信を行う通信手段と、所定の処理を実行するためのプログラムを記憶するプログラム記憶領域を有する第1の記憶手段と、前記記憶されたプログラムを用いて演算処理を行う処理手段と、前記演算処理が行われる際に用いられるワーク領域を有し、電力を受信できない場合であっても記憶内容を保持する不揮発モードと電力を受信できない場合に記憶内容を消去する揮発モードとを切り換えることが可能な第2の記憶手段とを備える。そして、端末から送信されたコマンドデータに含まれる設定情報に基づいて前記第2の記憶手段を前記不揮発モードあるいは前記揮発モードに設定するように制御する。

(もっと読む)

データ処理装置、半導体装置および制御方法

【課題】RAMの使用効率を向上させるデータ処理装置を提供する。

【解決手段】データ処理装置は、CPU101と、電気的に書き換え可能な不揮発性メモリ107と、RAM105と、RAM105を、不揮発性メモリ107のプログラムをキャッシュするキャッシュメモリとして動作させる制御を行うキャッシュ制御部102と、不揮発性メモリ107を書き換えるための書き換えプログラムと書き換え用のデータとを格納するメモリとしてRAM105を利用し、当該書き換えプログラムを実行することにより不揮発性メモリ107を書き換える書き換えシーケンスを実行するフラッシュ書換部106と、キャッシュ制御部102およびフラッシュ書換部106を択一的に動作させる切換部104とを備える。

(もっと読む)

演算処理装置、および記憶システム

【課題】効率的にデータ転送を高速で行なうことのできるメモリシステムを実現する。

【解決手段】互いに属性の異なる情報を格納する第1および第2のメモリ(601,602)と、これらの第1および第2のメモリの記憶情報をそれぞれキャッシュする第3および第4のメモリ(611,612)と、これらの第1および第2のメモリと第3および第4のメモリの間のデータ転送を制御するコントローラを備える。第3および第4のメモリは、しきい値電圧以外の特性を利用して情報を不揮発的に格納する。

(もっと読む)

メモリシステム

【課題】リード/ライトの高速化が図れるメモリシステムを提供する。

【解決手段】メモリシステムは、電気的にデータの消去、書き込みが可能なメモリセルを複数配設してなるフラッシュ型EEPROMからなる第1のメモリ13−1,…,13−nと、強誘電体メモリ,磁気抵抗メモリ,及び相変化メモリの何れかからなり、第1のメモリよりも小容量で書き込み速度の速い第2のメモリ14と、第1及び第2のメモリ13,14を制御するコントロール回路15と、外部との通信を行うインターフェース回路とを有する。第1のメモリ13にはデータを記憶し、第2のメモリ14にはデータを記憶するためのルート情報、ディレクトリ情報、データのファイル名称、データのファイルサイズ、データの記憶箇所を記憶するファイルアロケーションテーブル情報、及びデータの書き込み終了時間の少なくとも一つを記憶する。

(もっと読む)

電子回路、画像形成装置およびDDR−SDRAMの初期化方法

【課題】DDR−SDRAMの初期化に要する時間を好適に短縮する技術を提供する。

【解決手段】電子回路31は、DDR−SDRAM33より短いアクセス時間を有する内部メモリ47と、不揮発性メモリ32に記憶されたプログラムにしたがって、内部メモリ47およびDDR−SDRAM33を利用して各種処理を実行する制御部41と、制御部41から、内部メモリ47へのアクセスとDDR−SDRAM33へのアクセスとを切替える切替部50とを備える。制御部41は、不揮発性メモリ32から、DDR−SDRAM33を初期化するための初期化プログラムを読み込み、読み込んだ初期化プログラムを内部メモリ47に格納し、内部メモリ47に格納された初期化プログラムを用いてDDR−SDRAM33を初期化する。

(もっと読む)

データプロセッサ及びデータ処理システム

【課題】外部メモリからイニシャルロードするプログラムに対して外部メモリ上の自由なマッピングを簡単な構成によって許容することができるデータプロセッサを提供する。

【解決手段】外部メモリからRAMにイニシャルロードされたプログラムを実行するデータプロセッサに、所定のリセット指示に応答して、外部メモリから転送制御情報をリードし、リードした転送制御情報が示すアドレス情報に基づいて当該外部メモリからプログラムをダウンロードし、ダウンロードしたプログラムを前記RAMに転送し、この転送を完了した後に、前記中央処理装置へ前記所定のリセット解除を指示する、ブートローダコントローラを採用する。プログラムに対して外部メモリ上のマッピングに応じた転送制御情報を用意すればよく、プログラムに対して外部メモリ上の自由なマッピングを簡単な構成によって許容することができる。

(もっと読む)

メモリモジュールとコントローラ

【課題】フラッシュメモリのアクセス時間とSDRAMのアクセス時間との整合を図り、大容量フラッシュメモリを含むメモリモジュールとコントローラを提供する。

【解決手段】フラッシュメモリと、SDRAMと、フラッシュメモリ及びSDRAMの夫々のアクセスを制御し、外部からのストア命令に従って、SDRAMに記憶されるデータをフラッシュメモリに転送するための制御回路とそれに結合された複数の入出力端子を含む。制御回路は、ストア命令に従ってSDRAMに記憶されるデータをフラッシュメモリに転送している間に、SDRAMからのデータ読出し命令が入力された場合において、そのデータ転送を中断し、読み出し命令に従ってSDRAMに記憶されるデータを外部に出力するよう制御する。

(もっと読む)

メモリ管理装置およびメモリ管理方法

【課題】メモリ寿命の長期化に有利なメモリ管理装置およびメモリ管理方法を提供する。

【解決手段】本発明の一態様に係るメモリ管理装置1は、第1メモリ8と不揮発性の第2メモリ9,10とを含む混成メインメモリ2を統合的に管理するメモリ管理装置1であって、外部から前記混成メインメモリの解放位置を指定する論理アドレスに係る解放要求を受けた際、前記指定された論理アドレスと前記第1,第2メモリの物理アドレスとを関連付けたアドレス変換情報13を参照し、前記解放要求のあった論理アドレスに対応するデータが存在する物理アドレスを確認し、前記第1メモリ8上に対応するデータがある場合にはそのデータを消去する。

(もっと読む)

メモリ管理装置

【課題】不揮発性半導体メモリの寿命を延ばす。

【解決手段】本発明の一態様に係るメモリ管理装置1は、第1の半導体メモリと、第1の半導体メモリよりもアクセス可能上限回数の小さい不揮発性の第2の半導体メモリとのうちの少なくとも一方に記憶される各データの特性に基づいて生成され、当該各データの配置領域を決定するヒントとなる配置ヒント情報14を管理する。メモリ管理装置1は、配置ヒント情報14とメモリ使用情報11とメモリ固有情報12とに基づいて、書き込み対象データに対して第1の半導体メモリと第2の半導体メモリとのメモリ領域の中から、書き込み領域を決定する管理部15を具備する。配置ヒント情報14の生成は、オペレーティングシステムによって行われる。

(もっと読む)

1つのインターフェースを有するハイブリッド・メモリ・デバイス

【課題】メモリ・コントローラを、SDRAMとフラッシュ・メモリを内部に有するハイブリッド・メモリ・デバイスの一構成要素とする。

【解決手段】コントローラ308Bは、標準的なSDRAMインターフェースを有するメモリ・デバイスがSDRAM304とフラッシュ306A,306Bへのアクセスを与えることを可能にし、SDRAMアドレス空間の1つ以上の指定ブロック320A,320BにおいてSDRAMを無効にする。コマンド・プロトコルは、メモリ・ページをSDRAMインターフェース・アドレス空間にマッピングし、フラッシュ・メモリを設けることを望む計算機において、1つのピン互換マルチチップ・パッケージと既存のSDRAMとを交換することを可能とし、フラッシュにアクセスするためのソフトウェアの変更が行われる。

(もっと読む)

メモリシステム及びその動作方法

【課題】読み出し速度を向上した、不揮発性メモリ装置を含むメモリシステム及びその読み出し及び書き込み方法を提供する。

【解決手段】本発明のメモリシステムは不揮発性メモリ装置、前記不揮発性メモリ装置を制御するためのメモリコントローラ、及び前記メモリコントローラに含まれ、反復的に書き込み要請されたパターンを有するデータ(パターンデータ)を管理する仮想データインタフェースレイヤを含み、前記仮想データインタフェースレイヤは、前記パターンデータに対する読み出し要請がある場合に前記読み出し要請されたパターンデータを生成する。

(もっと読む)

数値制御装置の初期化方法及び数値制御装置

【課題】CPUの初期化時間を短縮可能な数値制御装置の初期化方法及び数値制御装置を提供する。

【解決手段】数値制御装置1は、第1動作周波数よりも速い第2動作周波数とに切り換えて動作可能なCPU2Aと、初期化するためのブートプログラムが格納されたROM3と、このROM3とCPU2A,2Bとを接続するバス5と、このバス5に介装され複数のCPU2A,2BとROM3との信号伝達を調停可能なバス調停回路6とを有し、CPU2Aの起動時に、CPU2Aとバス調停回路6を第1動作周波数で起動させ、次に、バス5とバス調停回路6を介してROM3からブートプログラムを読み込んでCPU2Aのキャッシュメモリ10に格納し、CPU2Aの動作周波数を第1動作周波数から第2動作周波数に切り換え、CPU2Aの動作周波数の切り換えに応じて、バス調停回路6の動作周波数を第1動作周波数から前記第2動作周波数に切り換える。

(もっと読む)

メモリモジュール、メモリシステム、及び情報機器

【課題】高速読み出し、書き込みが可能な大記憶容量のROMとRAMを含むメモリシステムを提供する。

【解決手段】不揮発性メモリ(CHIP1)、DRAM(CHIP3)、制御回路(CHIP2)、情報処理装置(CHIP4)を含むメモリシステムを構成する。予めFLASHのデータをSRAMおよびDRAMへ転送させて高速化を図る。不揮発性メモリ(FLASH)とDRAM(CHIP3)間のデータ転送は、バックグランドで行えるようにする。これら複数のチップからなるメモリシステムを、各チップが相互に積層して配置され、ボールグリッドアレイ(BGA)やチップ間のボンディングによって配線されたメモリシステム・モジュールとして構成する。Flashのデータをコピーできる領域をDRAMに確保し、電源投入直後あるいはロード命令により、予めDRAMへデータを転送しておくことで、DRAMと同程度の速度でFLASHのデータを読み出すことができるため、携帯機器の高性能化、高機能化が図れる。

(もっと読む)

1 - 20 / 154

[ Back to top ]