Fターム[5B061BA03]の内容

Fターム[5B061BA03]に分類される特許

1 - 20 / 187

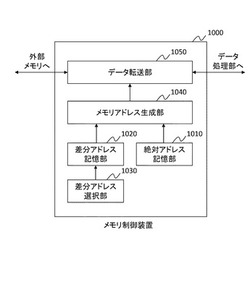

メモリ制御装置、メモリ制御方法、データ処理装置、画像処理システム

【課題】回路規模を抑えつつデータ整列が完了した状態で外部メモリから内部メモリにデータを転送する方法が求められていた。

【解決手段】本発明のメモリ制御装置は、外部メモリから複数の処理機構を備えるデータ処理手段にデータを転送するメモリ制御装置であって、所定のデータ転送期間において共通の基準値となる絶対アドレスを記憶する絶対アドレス記憶手段と、複数の差分アドレスを記憶する差分アドレス記憶手段と、複数の差分アドレスを所定の順序で選択する差分アドレス選択手段と、差分アドレス選択手段が選択した差分アドレスと絶対アドレスとを組み合わせてメモリアドレスを生成するメモリアドレス生成手段と、メモリアドレス生成手段で生成されるメモリアドレスを外部メモリに入力し、メモリアドレスからデータを読み出してデータ処理手段にデータを転送するデータ転送手段と、を具備する。

(もっと読む)

情報処理装置及びメモリ管理方法

【課題】 転送装置から転送されてくる画像データを効率的に処理できる情報処理装置およびメモリ管理方法を提供することを目的とする。

【解決手段】 実施形態によれば、情報処理装置は、メモリと、テーブルと、変更手段と、通知手段とを有する。メモリは、複数の画像データを保持する複数のバッファ領域を有する。テーブルは、複数のバッファ領域を画像データが書き込まれる受信バッファと画像データを保持する保持バッファとに割り当てる。変更手段は、前記受信バッファに書き込まれた画像データを保持する場合、前記保持すべき画像データが書き込まれた受信バッファと保持バッファとを入れ替える。通知手段は、変更手段により受信バッファと保持バッファとを入れ替えた場合、変更後の受信バッファを示す情報を画像転送元へ通知する。

(もっと読む)

データ転送制御装置及び方法

【課題】二次元DMACを用いたデータ転送制御装置において、従来技術に比較してデータバスの使用効率を高めることができるデータ転送制御装置及び方法を提供する。

【解決手段】ダイレクトメモリアクセスコントローラを用いたデータ転送制御装置であって、転送先のアドレス、リードもしくはライトを指定するコマンドを発行するコマンド制御部と、データ転送の際に記憶装置制御回路よりタグ情報を受け取ることでどのコマンドに対するデータ転送か判別するために、コマンド発行の際にタグ情報を生成するタグ生成部と、上記タグ情報にアドレスオフセットの情報を含め、データ転送の際に当該データに対応するアドレスオフセットの情報を受けとり、上記記憶装置制御回路から受けとったデータから上記アドレスオフセットの情報に基づいて有効データの選択を行って出力する有効データ選択部とを備える。

(もっと読む)

DMA制御装置

【課題】DMAを行う複数のパイプラインを、簡単な設定により任意に接続できるようにし、またデータ交換の単位も、点・線・面・立体など柔軟に対応でき、さらに時分割制御により見かけ上同時実行可能なDMA装置を提供すること。

【解決手段】複数のDMA設定に対し、設定単位ごとに時分割スケジューリングを行う。自らのDMAの指標と接続するDMAの指標との比較結果を用いた起動制御を行い、さらに処理の順序関係を保証する。

(もっと読む)

データ転送装置及びデータ転送方法

【課題】データ転送をより柔軟に行えるデータ転送装置及びデータ転送方法を提供する。

【解決手段】転送データサイズの上限値を設定可能なレジスタと、この上限値と外部から送られた転送サイズとを比較し、この転送サイズがレジスタ設定値より大きい場合、この転送サイズを減少させる機構とを備えるデータ転送装置。また、レジスタに設定値を設定し、転送データサイズの上限値を設定し、この上限値と外部から送られた転送サイズとを比較し、この転送サイズが前記設定値より大きい場合、この転送サイズを減少させるデータ転送方法。

(もっと読む)

オーディオ再生装置及びオーディオ再生方法

【課題】DMA転送を用いるオーディオ再生装置に対して、消費電力を抑制すると共に、通常再生と特殊再生の切換えを効率良く行う。

【解決手段】プロセッサAにより電源のオン・オフが制御されるプロセッサBは、圧縮された音声データをデコードして、デコード後データをメモリ102に格納する。DMA転送部110は、通常再生時においてメモリ102に格納されたデコード後データを格納順に転送する。通常再生時のDMA転送中に、通常再生と異なる特殊再生が要求されたときに、DMA転送部110は、特殊再生の種類に応じた方向と連続フレーム数とスキップフレーム数で、メモリ102に格納されたデコード後データに対して、スキップフレーム数の分のフレームのデコード後データのスキップと、連続フレーム数の分のフレームのデコード後データの連続転送とを交互にする特殊再生転送を行う。

(もっと読む)

情報処理装置、その装置を用いた記録装置、及び、情報処理方法

【課題】複数の異なるプロトコルを持つバス間で共有メモリを使用するシステムにおいて、メモリアクセスの順序保障を行うことを目的とする。

【解決手段】CPUが接続されるバスとは異なるプロトコルによって動作し、ライトDMAを行うバスマスタが接続されるのと同じバスに接続される順序保障回路を備える。その順序保障回路は、ライトDMAを行うバスマスタからのライトDMA終了通知割り込み信号を検出し、リードDMAを行うバスマスタによるメモリからのリードDMA動作の後、ライトDMA完了通知割り込み信号を発行する。これにより、メモリアクセスの順序保障を実現する。

(もっと読む)

DMA制御装置、画像形成装置、および、DMA制御方法

【課題】大きなオーバーヘッドを生じさせることなく、データのDMA転送を効率的に行うこと。

【解決手段】データ転送検出部27aが、外部デバイス40からメモリ30の所定のメモリ領域へのデータ転送を検出し、データ転送検出部27aにより該メモリ領域へのデータ転送が検出された場合に、DMA実行指示部27bが、画像処理DMAコントローラ23aに対して、上記メモリ領域から画像処理専用メモリ23bへのデータのダイレクトメモリアクセス転送の実行開始を指示する。

(もっと読む)

半導体装置及び制御方法

【課題】DMA機能を搭載した半導体装置において、CPUの処理速度とDMA転送の速度をバランス良く制御する。

【解決手段】マイクロコンピュータ100は、CPU(Central Processing Uint)110と、DMA(Direct Memory Access)処理部120と、制御部130を備える。制御部130は、DMA処理部120に保留されたDMA転送の数である保留数に応じて、該保留数が多いほど、処理速度が速くなるようにCPU110の処理速度を制御する。

(もっと読む)

情報処理装置および画像形成装置

【課題】転送元情報処理回路からメモリに転送されたデータを制御部が読み込んだときに、情報処理データの一部が足りない無効データを取得する回数を低減する。

【解決手段】情報処理装置1は、転送元情報処理回路12から転送先情報処理回路13まで情報処理データを引き渡す場合に、データを取得順に出力するFIFO処理部67を介して情報処理データをメモリ70に一旦記憶させる装置であって、転送元情報処理回路が出力した情報処理データがFIFO処理部に到達した後、FIFO処理部にステータスデータを出力し、さらに割込信号を発生する割込処理部11と、FIFO処理部とメモリとの間でデータのDMA転送を行うDMA機能部202と、割込信号を受信してからステータスデータがメモリに記憶されているかを否かを判定し、記憶されているときにDMA機能部に、メモリからFIFO処理部まで情報処理データをDMA転送させる制御部201とを備える。

(もっと読む)

オーディオ再生装置及びオーディオ再生方法

【課題】DMA転送を用いるオーディオ再生装置に対して、消費電力を抑制すると共に、通常再生と特殊再生の切り替え時に誤再生を回避する。

【解決手段】DMA転送部104は、DMA転送フレーム番号レジスタ115、DMA転送フレームサイズレジスタ114、DMA転送中アドレスレジスタ111、DMA転送停止アドレスレジスタ112を備える。プロセッサAにより電源のオン/オフが制御されるプロセッサBは、DMA転送中に、通常再生とは異なる特殊再生が要求されたときに、メモリ101に格納されたフレームのうちの、該フレームの転送が完了すると、メモリ101に格納されたデコード後データの転送を停止する停止フレームの終端アドレスをDMA転送停止アドレスレジスタ112に設定する。

(もっと読む)

半導体装置

【課題】プロセッサのシステムバスに接続するバスマスタデバイスからの、不正アドレスへのアクセスを遮断する機構を、少ない回路量で実現する。

【解決手段】システムバスの形式に合わせて、バスマスタデバイスとバスの間のアドレス線および制御線、または、バスの制御回路部に不正アドレスアクセス遮断機構を挿入する。不正アドレスアクセス遮断機構内に、アクセスを許可するアドレス範囲を設定するレジスタを設け、アドレス線に出力されているアドレスが、その範囲内であるかどうかを比較器によって判定し、範囲を逸脱した場合には、制御線の出力を抑止することによって不正アドレスアクセスを遮断する。

(もっと読む)

DMA装置、情報処理装置、及びデータ転送方法

【課題】比較的簡易な構成で、DMA転送の高速化を実現するDMA装置を提供する。

【解決手段】DMA装置は、ディスクリプタを読み出すディスクリプタ制御部と、読み出されたディスクリプタに対応するデータを転送するDMAコントローラと、ディスクリプタ制御部により読み出されたディスクリプタを蓄積するバッファと、バッファに蓄積されたディスクリプタに基づいて、ミスアライン計算を行うミスアライン計算手段とを有し、ディスクリプタ制御部は、あるディスクリプタに対応するDMA転送処理が完了する前に、このディスクリプタの後続のディスクリプタを読み出す。

(もっと読む)

拡張メモリ付きハイブリッドドライブ、及び拡張メモリ付きハイブリッドドライブを備えた記録再生装置

【課題】光ディスクドライブと不揮発性メモリを組み合わせた拡張メモリ付きハイブリッドドライブにおいて、不揮発性メモリへのデータ転送上の制限を緩和して、拡張メモリ付きハイブリッドドライブの利便性を高めること。

【解決手段】光ディスクドライブと不揮発性メモリを組み合わせた拡張メモリ付きハイブリッドドライブ100において、光ディスク制御部10に拡張バスI/F30を設けて拡張バス35により不揮発性メモリ装置40を接続すると共に、ホストI/F13との間を拡張バス35で接続する。ホスト機器50側からのデータを拡張バスI/F30経由で不揮発性メモリ42に転送可能として、バッファメモリ14側のデータ転送要件に左右されない利便性の高い拡張メモリ付きハイブリッドドライブを提供する。

(もっと読む)

マイクロコンピュータ

【課題】1つのDMAコントローラが複数の処理手段に共用されるようになっているマイクロコンピュータにおいて、異なる処理手段に割り当てられた記憶領域同士の間でDMA転送が行われてしまう誤アクセスを防止する。

【解決手段】1つのDMAコントローラ37が2つのプロセッサエレメント(PE)1,2に共用されるマイコン40には、記憶領域のうち、どの記憶領域がどのPEに割り当てられているかを示す割当テーブルを記憶するレジスタ41が設けられている。そして、DMAコントローラ37は、DMA要求を受けると、その要求が示すデータ転送元の記憶領域が割り当てられているPEと、その要求が示すデータ転送先の記憶領域が割り当てられているPEとを、上記割当テーブルから特定して、その特定した両方のPEが一致していないと判定した場合には、データの転送処理(DMA転送)を実施しないようになっている。

(もっと読む)

システムLSI

【課題】外部通信速度を向上できるとともに、インタフェース回路のFIFO領域の面積をも大幅に削減できるシステムLSIを提供する。

【解決手段】データ送信時にはワークRAM1から送信データをCPUを介さずに直接読み出してFIFO領域8に書き込み、データ受信時にはFIFO領域8から受信データをCPUを介さずに直接読み出してワークRAM1に直接書き込むメモリアクセス回路2と、データ送信時にはFIFO領域8に書き込まれた送信データを外部に送信し、データ受信時には外部から受信した受信データをFIFO領域8に書き込むインタフェースコントローラ3とを有するインタフェース回路9とを備え、インタフェースコントローラ3が外部と送受信中であっても、メモリアクセス回路2は、ワークRAM1とFIFO領域8との間のデータ転送を並行して実行する。

(もっと読む)

データ転送制御装置

【課題】データ転送量とメモリ使用量の削減、及び画像処理装置における負荷を軽減してシステム全体の処理スループットの向上を実現できるデータ転送制御装置を提供すること。

【解決手段】データ転送制御装置400は、転送制御部401で受信された画像データを記憶するデータ記憶部402と、設定部200によって設定されたデータ処理の内容に従って、データ記憶部402に記憶された前記画像データに対して演算を施すデータ演算部4032と、データ演算部4032で演算された画像データを転送制御部404に出力するように制御するか、データ記憶部402に帰還させるように制御する内部制御部4033とを備える。データ記憶部402に画像データが帰還された場合、データ演算部4032は、データ記憶部402に帰還された画像データに対してさらに演算を施す。

(もっと読む)

半導体装置

【課題】通信用のデータバッファに記憶容量の無駄を生じ難く、通信データのバストラフィックを低減可能とする。

【解決手段】、複数の通信チャネルを有する通信回路を内部バスにインタフェースするのに通信用ブリッジ回路を採用し、通信用ブリッジ回路には通信チャネルに一対一対応する通信チャネルバッファ領域が割り当てられるバッファメモリを採用し、バッファメモリは一方においてバスインタフェース回路を介して内部バスにインタフェースされ、他方において通信チャネルインタフェース回路を介して通信回路にインタフェースされる。通信チャネルインタフェース回路は、内部バス経由でレジスタ回路に設定された通信チャネルバッファ領域の定義情報に基づいて、通信チャネルバッファ領域から対応する通信チャネルに与える送信データを読み出し且つ通信チャネルから与えられる受信データを対応する通信チャネルバッファ領域に書き込む制御を行う。

(もっと読む)

データ受信装置

【課題】演算処理への影響を軽減させることができるデータ受信装置を提供する。

【解決手段】プリアンブルとユーザデータの長さ情報とユーザデータとを含む可変長データを非同期シリアルインターフェースにおいて、演算装置からの初期設定により、DMAコントローラを介して受信データをプリアンブルの終了まで受信して前記演算装置に割り込み信号を出力する受信データ判定装置を備え、前記演算装置は、前記割り込み信号を取得して前記初期設定を解除すると共に、前記非同期シリアルインターフェース及び前記DMAコントローラに対して前記ユーザデータの長さ情報の記憶装置へのDMA転送を設定して前記記憶装置に書き込ませた後に、前記記憶装置から読み出される前記ユーザデータの長さ情報より前記ユーザデータのDMA転送数を算定して前記DMAコントローラを介して前記記憶装置に書き込ませる。

(もっと読む)

データ転送装置、その制御方法、および制御プログラム

【課題】DRAMなどのメモリに複数種類のデータを転送して格納する際、プリチャージの回数を抑えてデータを効率よく転送する。

【解決手段】データ転送制御装置310は、互いに異なる複数種類のデータをDRAM320に転送する。DRAMには複数のページが規定されており、データ転送制御装置は複数種類のデータについて所定のデータ量を1つの単位として、当該1つの単位毎に前記複数種類のデータをページの1つに転送する。この際、CPU205は複数種類のデータについて所定のデータ量を設定する。

(もっと読む)

1 - 20 / 187

[ Back to top ]