Fターム[5B061BB01]の内容

バス制御 (3,799) | 調停のための制御方式(アービトレーション) (517) | 集中型調停 (434)

Fターム[5B061BB01]の下位に属するFターム

調停制御装置の回路構成 (150)

バス占有の継続 (23)

バス占有の中断、再開 (35)

相手装置の状況によりバスを一時開放 (12)

特定の装置にバス使用権を与えておくもの (7)

優先レベル指定手段を有するもの (84)

集中型走査カウンタ方式 (9)

Fターム[5B061BB01]に分類される特許

1 - 20 / 114

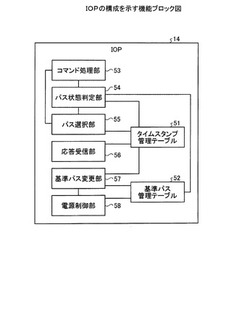

通信制御装置、情報処理装置及びパス選択方法

【課題】パスを効率的に使用すること。

【解決手段】IOP14は、パス状態判定部54とパス選択部55とを有する。パス状態判定部54は、自装置と通信先装置とを接続する複数のパスのうちデータの送信処理中ではなく、かつ、データ送信を終了した後にデータ送信を所定時間禁止する禁止期間内でもないパスが存在するか否かを判定する。パス選択部55は、パス状態判定部54によって、データの送信処理中ではなく、かつ、禁止期間内でもないパスが存在しないと判定された場合、データの送信処理を終了したが禁止期間を経過していないパスをデータ送信用に選択する。

(もっと読む)

バスモニタ装置、バスモニタ方法、およびプログラム

【課題】データバスの効率を向上するために有用な情報を取得することができるバスモニタ装置、バスモニタ方法、およびプログラムを提供する。

【解決手段】共通バスに接続された複数の処理ブロックが、複数のバンクを有するアドレス空間からなるメモリとの間で、共通バスを介してデータの受け渡しを行う際の、該データの受け渡しの状態を表す転送情報に基づいて、予め定められた一定の単位時間あたりの共通バス上のデータの帯域を測定する測定部、を備える。

(もっと読む)

バスブリッジ装置及びデータ処理システム

【課題】スプリットトランザクション方式のバスブリッジ装置において、複数の下位バス間の排他制御を実現する。

【解決手段】排他制御部015は、下位バスIF部による下位バスへのアクセス状況を監視し、下位バスIF部による下位バスへのアクセス状況が所定の排他条件に合致している間は、次の実行対象のコマンドに基づいて下位バスへのアクセスを行う下位バスIF部に下位バスへのアクセスを保留させ、アクセス状況が排他条件に合致しなくなった際に、アクセスを保留させていた下位バスIF部による下位バスへのアクセスを開始させることで、複数の下位バス間の排他制御を実現する。

(もっと読む)

拡張メモリ付きハイブリッドドライブ、及び拡張メモリ付きハイブリッドドライブを備えた記録再生装置

【課題】光ディスクドライブと不揮発性メモリを組み合わせた拡張メモリ付きハイブリッドドライブにおいて、不揮発性メモリへのデータ転送上の制限を緩和して、拡張メモリ付きハイブリッドドライブの利便性を高めること。

【解決手段】光ディスクドライブと不揮発性メモリを組み合わせた拡張メモリ付きハイブリッドドライブ100において、光ディスク制御部10に拡張バスI/F30を設けて拡張バス35により不揮発性メモリ装置40を接続すると共に、ホストI/F13との間を拡張バス35で接続する。ホスト機器50側からのデータを拡張バスI/F30経由で不揮発性メモリ42に転送可能として、バッファメモリ14側のデータ転送要件に左右されない利便性の高い拡張メモリ付きハイブリッドドライブを提供する。

(もっと読む)

マイクロコンピュータ

【課題】1つのDMAコントローラが複数の処理手段に共用されるようになっているマイクロコンピュータにおいて、異なる処理手段に割り当てられた記憶領域同士の間でDMA転送が行われてしまう誤アクセスを防止する。

【解決手段】1つのDMAコントローラ37が2つのプロセッサエレメント(PE)1,2に共用されるマイコン40には、記憶領域のうち、どの記憶領域がどのPEに割り当てられているかを示す割当テーブルを記憶するレジスタ41が設けられている。そして、DMAコントローラ37は、DMA要求を受けると、その要求が示すデータ転送元の記憶領域が割り当てられているPEと、その要求が示すデータ転送先の記憶領域が割り当てられているPEとを、上記割当テーブルから特定して、その特定した両方のPEが一致していないと判定した場合には、データの転送処理(DMA転送)を実施しないようになっている。

(もっと読む)

調停装置、画像形成装置、調停方法及びプログラム

【課題】優先順位の異なる複数のDMACからの転送要求を調停するときに、システム全体のパフォーマンスを向上させる。

【解決手段】第1のライトDMAC15は、1ライン単位で入力されるデータを1ライン期間内にメモリに転送させる必要がある。アービタ113内の必要転送時間計算部121は、バースト長と、バス幅と、必要転送レートRaとから、要求されたデータの転送に必要な時間T2を計算する。また、ラインスタート信号により起動されるタイマーにより、1ラインの開始からの経過時間T1を計測する。T1の方がT2より長ければ、T1とT2が等しくなるまで、第1のライトDMAC15からの転送要求に対して、ウェイト要求信号をアサートする。

(もっと読む)

バスシステムおよびそのデッドロック回避回路

【課題】スプリットトランザクションにより複数のスレーブへの同時アクセスを許容したシステムにおいて、デッドロックの発生を防止する。

【解決手段】先行トランザクション情報管理部410は、対応するマスタから複数のスレーブの何れかに先に発行された先行トランザクション情報を管理する。発行停止判定部420は、先行トランザクション情報に基づいて、対応するマスタから新たに発行されたトランザクションがデッドロックの要因になるか否かを判定する。レスポンス出力制御部430は、先行トランザクション情報に基づいて、対応するマスタへ返送すべきレスポンスを制御する。退避バッファ470は、先行トランザクションに対する複数のスレーブからのレスポンスが予め期待された順序とは異なる順序で戻ってきた場合に、そのレスポンスを退避する。

(もっと読む)

電子回路装置および動作方法

【課題】 各種機能を実現する複数の機能ユニットと複数のDMACとを備える電子回路装置および該電子回路装置の動作方法を提供すること。

【解決手段】 本発明の電子回路装置100は、複数の読込DMA制御部120および複数の書込DMA制御部122のそれぞれと外部インタフェース(140,150)との間に介在する調停部130と、複数の読込DMA制御部120にそれぞれ接続される複数の第1ポートと複数の機能処理部110にそれぞれ接続される複数の第2ポートと書込用選択部134にそれぞれ接続される1以上の第3ポートとを備える読込用選択部132と、複数の書込DMA制御部122にそれぞれ接続される複数の第4ポートと複数の機能処理部110にそれぞれ接続される複数の第5ポートと読込用選択部132にそれぞれ接続される1以上の第6ポートとを備える書込用選択部134と含む。

(もっと読む)

シリアル・アドバンスト・テクノロジ・アタッチメント通信における改善されたホスト/イニシエータ利用のための方法および機器

【課題】複数のSATA記憶デバイスに結合されるSATAホストの役割を果たすSASイニシエータを利用することに関し、SATA記憶システムの性能を改善すること。

【解決手段】SAS/STPイニシエータ・デバイスと、強化されたスイッチング・デバイスを介してそのイニシエータに結合される複数のSATA記憶デバイスとの間の改善された通信性能を得るための方法および機器。このスイッチング・デバイスは、SATA記憶デバイスからDMAセットアップFISを受信し、複数の修正されたDMAセットアップFISをイニシエータに伝送するよう、本明細書の諸特徴および諸態様に従って強化され、それぞれの修正されたDMAセットアップFISは、受信されるDMAセットアップFIS内の最大カウントよりも少ないサブカウントを含む。

(もっと読む)

バス転送システム

【課題】異なったデータ転送プロトコルを同一システムバス上で実行すること。

【解決手段】例えば、CPUモジュール21とCPUモジュール2mは、調停サイクルにおいて共通の調停プロトコルにてアクセス権を決定し、CPUモジュール21がアクセス権を獲得するとデータバス3を使ってメモリモジュール30、入出力モジュール41などとパラレルデータ転送を行う。一方、CPUモジュール2mがアクセス権を獲得すると、コントロールバス4Aのリード、ライト信号線をそれぞれ兼ねるシリアルデータ信号線S1、S2を使って入出力モジュール4nとシリアルデータ転送を行う。

(もっと読む)

電子機器及びその制御方法

【課題】全体処理のスループット低下を防止しつつも、リアルタイム性を必要とするバスマスタの動作を保証するための技術を提供する。

【解決手段】内部バスに複数のバスマスタが接続された電子機器であって、複数のバスマスタのうち、第1のバスマスタにデータを供給するデータバッファと、データバッファと接続され、データを生成してデータバッファに蓄積するデータ生成手段と、内部バスに接続され、バスマスタからの要求を受け付けるバススレーブと、複数のバスマスタからバススレーブに対する要求の調停を行うバスアービタとを備え、データ生成手段がリアルタイム処理を開始する場合に、バスアービタが第1のバスマスタとは異なる他のバスマスタに対してバースト長の切り替えを指示する。

(もっと読む)

半導体集積回路

【課題】DMA転送によるデータの上書き防止の設定/解除について、ソフトウェア処理による煩雑さを無くすとともに、ソフトウェアによって誤った制御をされたDMACが原因で発生する異常画像の発生防止と解析を容易に行うことができる半導体集積回路を提供する。

【解決手段】複数のメモリアクセス手段によるメモリへのアクセスの調停を行うアクセス調停手段は、所定のメモリアクセス手段によりメモリに書き込みが行われたアドレスの範囲を上書き禁止領域として設定し、書き込みを行ったメモリアクセス手段以外の他のメモリアクセス手段により上書き禁止領域への書き込みが要求された場合、上書きの発生を制御手段に通知するための割込みを発生させ、上書き禁止領域に対して所定のメモリアクセス手段により読み出しが行われた場合、当該読み出しが行われたアドレスの範囲に設定されている上書き禁止領域の設定を解除する。

(もっと読む)

リモート・ダイレクト・ストレージ・アクセス

【課題】半導体ストレージのリモート・ダイレクト・アクセスに関するシステム、装置、及び方法を提供する。

【解決手段】サーバのネットワーク・インターフェース・コンポーネント(NIC)は、サーバの中央処理ユニット(CPU)及びメインメモリを迂回するネットワーク・ストレージ・アクセス・リンクによって、半導体ストレージモジュールにアクセスする。NSAリンクは、半導体ストレージのリニアな「メモリビュー」にリモート・エンティティーを提供するために、リモート・ダイレクト・メモリ・アクセス(RDMA)をサポートする。NSAリンクは、NIC及びストレージ・コントローラと直接接続するアービターを含んでもよい。

(もっと読む)

データアクセス制御装置

【課題】 アクセス制御部からシリアルバスを介して被アクセス部が接続される構成において、アクセス期間を短縮化させる。

【解決手段】 アクセス制御部1は、 シーケンスデータと非シーケンスデータを特定しシリアルバス3からアクセス先を指定してデータ伝送する。被アクセス部5、7は、シリアルバス3に直列接続され非シーケンスデータおよびシーケンスデータがアクセスされる。被アクセス部5、7は第1、第2のメモリ空間11、13、調停部15およびアクセス空間17を有する。第1のメモリ空間11はシリアルバス3に接続され非シーケンスデータを記憶する。第2のメモリ空間13はシリアルバス3に接続されシーケンスデータを記憶する。調停部15は非シーケンスデータとシーケンスデータを調停する。アクセス空間17は調停部15からの非シーケンスデータとシーケンスデータのアクセスを受ける。

(もっと読む)

データ転送装置、データ転送方法、データ転送プログラム及び記録媒体

【課題】優先順位の異なる複数のDMACからのメモリへのアクセス要求を優先順を変更して適切に調停するデータ転送装置、データ転送方法、データ転送プログラム及び記録媒体を提供する。

【解決手段】ライン同期信号LSYNCと画像先端同期信号FSYNCに基づいて1ライン分の画像データをメモリから読み取って転送するRDMAC134を含む複数のDMAC123、124からのメモリへのリクエストを予め設定されている優先順位に基づいてリクエスト調停部112が調停する場合、画像処理部11の転送データ量監視部136が2つのラインバッファ132がフル状態か否か監視して、該監視結果に基づいて必要転送量計算部105が、上記優先順位の変更の要否を判定し、優先順位制御部111が該判定結果に基づいてリクエスト調停部112の優先順位を制御する。

(もっと読む)

情報処理装置および情報処理方法

【課題】モニタ装置からシステムバスを制御して各装置の動作を制御でき、各装置の動作状態を監視可能な情報処理装置を提供する。

【解決手段】システムバス4と、このシステムバス4にバス接続され、予め有する固有機能を実行し、動作の状態を示す情報を出力する装置2と、を備え、この装置2は、固有機能を実行する装置固有機能実行部9と、この装置固有機能実行部9の動作の状態をモニタするモニタ装置6にシリアル通信接続され、このモニタ装置6との間で信号を授受するシリアル通信部8と、このシリアル通信部8側、装置固有機能実行部9側およびシステムバス4側にそれぞれ内部バス11、12、10を介して接続され、シリアル通信部8からシステムバス4に対するアクセス要求と、装置固有機能実行部9からシステムバス4に対するアクセス要求との間でバス使用権を調停するバス調停部13とを備える。

(もっと読む)

バス調停装置

【課題】特定のマスタからの要求を低レイテンシでスレーブに伝送できると共に、他のマスタに必要な帯域を確保できるバス調停装置を提供すること。

【解決手段】調停回路108は、低レイテンシが求められるCPU等のマスタ101からのリードライト要求を一定間隔で受け付けることで、マスタ101が低レイテンシでメモリアクセスを行う。広帯域が求められるDMAコントローラ等のマスタ102,103には、マスタ101が使用しない残りの帯域を割り当てることで、必要な帯域が確保される。調停回路108は、スレーブ118内のバッファ119にリードライト要求が滞留している状況下では、優先度の低いマスタ102,103からのリードライト要求の受理を抑制する。

(もっと読む)

調停装置、画像処理装置、及び画像形成システム

【課題】書込要求信号が連続して調停手段に入力される場合に比べて、読み出しに必要な伝送路の帯域に応じて書込みに必要な伝送路の帯域を確保する、調停装置、画像処理装置、及び画像形成システムを提供する。

【解決手段】キューカウンタ62及び抑制装置64を備え、キューカウンタ62が書込要求信号wrreqが入力されたときに、読出データの読み出しが行われていない読出要求信号rdreqの数をカウントしてカウント値として抑制装置64に出力し、抑制装置64は、入力されたカウント値に応じて、チャネルCH1からのアクセス要求信号CH1_REQが調停回路52に入力される時間を遅延させることにより、チャネルCH1のアクセスを抑制する。

(もっと読む)

情報処理装置

【課題】最小限の回路規模により複数の暗号化処理を並列に行う。

【解決手段】メモリ上のデータを転送する複数の転送手段と、データに処理を施すデータ処理手段と、複数の転送手段から転送要求をアビトレーションするアビトレーション手段と、データ処理手段における処理に関するパラメータを複数の転送手段ごとに保持する手段と、アビトレーションの結果に基づき、パラメータをデータ処理手段に出力する手段と、処理されたデータの出力先を選択する出力先選択手段と、を有し、データ処理手段は、動作状況を示す動作中判別信号をアビトレーション手段に送信し、アビトレーション手段は、転送要求それぞれの優先度が記述されたアビトレーションポリシーを保持しており、当該アビトレーションポリシーと動作中判別信号とに基づき、転送要求をアビトレーションし、出力先選択手段は、アビトレーションの結果と動作中判別信号に基づき、データの出力先を選択する。

(もっと読む)

データフロー及びプロセッサのメモリ共有化ための装置、方法及びプログラム

【課題】情報装置のデータフローのためのバッファとプロセッサのためのメインメモリとを共有化させるためのメモリアクセス装置を提供する。

【解決手段】アービタ手段は、複数の機能ブロックからのメモリのアクセス要求を順にラウンドロビン方式で所定の転送長で割当て、(a)所定の転送長で部分転送に分割し、データ転送の帯域に応じて1回のラウンドロビン・サイクルの中で複数の部分転送をし、(b)複数の部分転送は異なる優先度を有し、異なる機能ブロックからの部分転送の交互の転送により全ての機能ブロックからのデータ転送の必要帯域を満たすように優先度をプログラマブルに設定し、(c)プロセッサからのメモリへのアクセス回数が、最優先で所定の転送長(CPU転送長)で部分転送間の所定の間隔において、機能ブロックからのデータフローの転送帯域への影響が小さくなるように、プロセッサ・アクセスを行う。

(もっと読む)

1 - 20 / 114

[ Back to top ]