Fターム[5B061BB08]の内容

バス制御 (3,799) | 調停のための制御方式(アービトレーション) (517) | 集中型調停 (434) | 調停制御装置の回路構成 (150) | 受付け順序の管理 (24)

Fターム[5B061BB08]に分類される特許

1 - 20 / 24

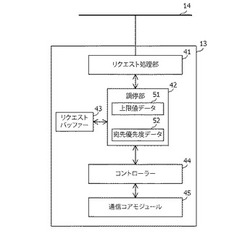

電子機器

【課題】 シリアルバスシステムにおけるリードレイテンシーの異なる複数の宛先に対する複数のリードリクエストが混在しても、各宛先に対するリードリクエストが円滑に処理されていくようにする。

【解決手段】 リクエストバッファー43は、所定の数のリクエストをキューイング可能であって、リクエストの宛先ごとに未処理リードリクエストの数の上限値を設定されている。調停部42は、新たなリードリクエストが受け付けられると、受け付けられたリードリクエストの宛先を特定し、特定した宛先についてのリクエストバッファー内の未処理リードリクエストの数が、特定した宛先についての上限値に到達している場合には、特定した宛先より優先度の低い宛先についての上限値を低くした上で、特定した宛先についての上限値を高くする。

(もっと読む)

相互結合網制御システム、相互結合網制御方法

【課題】情報間の順序を保証しつつ相互結合網の性能低下を抑制する相互結合網制御システム及び方法を提供すること。

【解決手段】本発明にかかる相互結合網制御システムは、相互結合網2と、順序保証バッファ3と、順序情報制御部4と、読出制御部5とを有する。相互結合網2は、複数の入力ポートと複数の出力ポートとを有し、入力ポートから入力された情報を、情報の出力先である出力ポートに出力する。順序情報制御部4は、入力ポートに入力される情報に対し、情報の出力先である出力ポート毎に、情報の読出順序を定める順序情報を付与する。順序保証バッファ3は、出力ポートから出力された情報を蓄積する。読出制御部5は、順序保証バッファ3に蓄積された情報を、順序情報により定められる順序にしたがって読出す。

(もっと読む)

データ処理装置及びバス調停装置

【課題】 データ転送のスループットの向上を図りながらも、各バスマスタがバス使用許可を取得するまでの待ち時間を極力短縮でき、かつ、バス使用効率の向上を図ることができるバス調停装置を提供する。

【解決手段】 バスマスタは、リード/ライトを行うデータのサイズを示すサイズ信号(例えばCDSZ)を与える。ステートマシン155は、サイズ信号に応じた数のバスサイクルを与えるので、バスマスタは、データを連続してリード/ライトできる。バスマスタが要求したサイズに応じた数のバスサイクルを単位として、必ず調停動作が行われる。サイズ信号はバスマスタが発行するので、データ転送に必要充分なサイズ情報の発行が可能であり、そうすると、ステートマシン155は、バスサイクルの最適な数を設定できる。

(もっと読む)

データバースト間の競合の解決

組込みシステムにおいて、複数のデータ要求装置と、複数のデータソースと、データ要求装置及びデータソースを相互接続するバスファブリックとがあり、バスファブリックが複数のバスコンポーネントを備える。バスコンポーネントと関連付けられたデータソース及び調停装置のうちのいくつか又は全ては、競合するデータバーストのうちの第1のデータバーストを選択すること、第1の選択されたデータバーストのクリティカル部分の長さを判定すること及び選択されたデータバーストのクリティカル部分を処理することによりデータバースト間の競合を解決する。次に、競合するデータバーストのうちの第2のデータバーストが選択され、第2の選択されたデータバーストのクリティカル部分の長さが判定され、第2の選択されたデータバーストのクリティカル部分が選択されたデータバーストの非クリティカル部分の前に処理される。  (もっと読む)

(もっと読む)

タイミング調整装置、タイミング調整方法、タイミング調整プログラム及び記録媒体

【課題】本発明は、複数のCPUからの複数のリソースに対する要求を要求順序に従ってその応答を調停するタイミング調整装置、タイミング調整方法、タイミング調整プログラム及び記録媒体に関する。

【解決手段】画像処理装置1は、アービタ回路21が、2つのCPU3a、3bが所定の実行順序で2つのブロック回路22a、22bに対して発行するリード要求の要求順を取得し、該アクセス要求に対する各ブロック回路22a、22bからCPU3a、3bへの応答を監視して、各ブロック回路22a、22bからの応答を、各CPU3a、3bから各ブロック回路22a、22bへのリード要求順と一致する順序にタイミング調整してCPU3a、3bに送る。したがって、ブロック回路22a、22bからの応答速度に差があって応答順序が入れ替わっても、CPU3a、3bに、予め設定されている実行順序で確実にライト要求を発行させることができる。

(もっと読む)

バスマスターシステム、コンピュータ装置、アクセス調停方法およびアクセス調停プログラム

【課題】複数のバスマスターが同一の資源にアクセスするコンピュータ装置において、いずれのバスマスターも該資源にアクセスしない無駄なタイミングの発生を抑制して、装置全体としての動作効率を向上させることができるバスマスターシステムを提供する。

【解決手段】本発明に係るバスマスターシステム1は、複数のバスマスター10〜15と、複数のバスマスターによって共有されるコンピュータ資源17と、複数のバスマスターの各々に対応し、コンピュータ資源にアクセスしようとするバスマスターがデータを記録するフラグ20〜25と、固定タイミングに該当するバスマスターに対応するフラグにデータが記録されていれば該バスマスターにコンピュータ資源へのアクセスを許可し、記録されていなければ該バスマスター以外のバスマスターにコンピュータ資源へのアクセスを許可する調停装置16とを有する。

(もっと読む)

割り込み処理装置及び割り込み処理方法

【課題】デバイスによるメモリへのデータ書き込みと、CPUによるメモリへのデータ読み出しの順序性を保証する。

【解決手段】割り込み処理装置1はPCIバス(L1〜L6)を介してデバイス3から出力される書き込みデータを格納し、デバイス3から出力される割り込み通知に基づいて前記書き込みデータをメモリ4に書き込み、書き込み終了後にCPU5へ割り込み通知を行う。

(もっと読む)

バスマスタ装置、情報処理システム、バスマスタ装置の制御方法並びにコンピュータプログラム

【課題】適切なデッドライン保証を行えるバスマスタ装置を提供する。

【解決手段】バススレーブ装置に対してバスを介してデータ転送を行うバスマスタ装置において、残り転送時間格納手段がデータ転送手段によりデータ転送を完了させるまでの残り時間を示す第1の残り時間を格納する。算出手段が、残り転送量、目標時間、及び、目標転送量に基づいて、第2の残り時間を算出手段で算出し、第2の残り時間が第1の残り時間より小さい場合に、残り転送時間格納手段における前記第1の残り時間を前記第2の残り時間により更新する。また、前記第1の残り時間と前記第2の残り時間との差分情報を、時間量削減量格納手段に格納する。データ転送手段による目標転送量のデータ転送が完了した直後に更なるデータ転送を行う場合は、残り転送時間格納手段の初期値として、更なる目標時間と差分情報との和が格納される。

(もっと読む)

データ転送方法,データ転送装置,電子機器および画像形成装置

【課題】 ROMからRAMにプログラムを書き込みRAMプログラムをCPUが実行するデータ転送装置の高速起動,高速実行。

【解決手段】 CPU1がROM4からプログラムの読み出しを行っている最中にROM4のプログラムをRAM3に転送するプログラム転送102を設け、CPU1からのRAM3への読み書きとプログラム転送102からのRAM3への書き込みを調停する第1調停103を設けた。第1調停103で、CPU1からのRAM3への読み書きを保留する。更に、CPU1がROM4からプログラムの読み出しを行っている最中に、プログラム転送102によるROM4のプログラムをRAM3に転送するためのROM4の読み出しを調停する第2調停104を設けた。

(もっと読む)

半導体回路

【課題】CPUの割り込み処理を早期に実行させることが可能な技術を提供する。

【解決手段】バスマスタ1〜4にはCPUが含まれている。バスマスタ1〜4のそれぞれは共通のバスBUSSを利用してバススレーブ5,6にアクセスする。バスアクセス調停回路7は、バスマスタ1〜4におけるバスBUSSに対するアクセス要求を調停する。割り込みコントローラ8は、割り込み要求が通知されると、CPUに対して割り込み処理の実行を通知するとともに、当該CPUのアクセス要求を優先して受け付けることを要求する優先処理要求信号PPRをバスアクセス調停回路7に出力する。バスアクセス調停回路7は、優先処理要求信号PPRが入力されると、CPUのアクセス要求を他のバスマスタ2〜4よりも優先して受け付ける。

(もっと読む)

バス制御装置、集積回路装置、バス制御方法、及びプログラム

【課題】マスタ装置に負荷をかけずに、アクセス要求の処理順序を保証するバス制御装置を提供する

【解決手段】前記複数のアクセス要求と、各アクセス要求の前記相異なるマスタ装置間で一意な順序を定める順序情報とを対応付けて保持するマスタキュー部11、及びスレーブキュー部12、前記複数のアクセス要求を、前記順序情報によって定められる順序で順次選択する順序制御手段13と、前記複数のアクセス要求を、前記選択された順序で前記スレーブ装置の一つへ発行するアクセス手段121X、121Y、121Zとを備える。

(もっと読む)

ネットワーク装置におけるローカルバスアクセス権付与方式

【課題】ネットワーク装置に、共有メモリに一定遅延時間でアクセスする必要があるローカルバスマスタが存在する場合であっても、当該ローカルバスマスタが確実に共有メモリに一定遅延時間でアクセスすることができる。

【解決手段】ローカルバス7とこのローカルバス上に設けられた共有メモリ4と前記ローカルバス上に設けられ各々ローカルバスアクセス権が与えられると前記共有メモリにアクセスでき少なくとも一が前記共有メモリに一定遅延時間でアクセスする必要がある複数のローカルバスマスタ1,2,3とを具備するネットワーク装置におけるローカルバスアクセス権付与方式において、スケジューリング手段5により、前記複数のローカルバスマスタに、一定の順番に、一定時間毎に、一定の時間だけローカルバスアクセス権を割り振る。

(もっと読む)

バス調停回路

【課題】 実時間性の要求される処理を実行するデバイスが複数存在する場合においても、それらの全てのデバイスについて、バス使用要求が発生してから制限時間内にバスを使用した処理を実行させる。

【解決手段】 第1カウンタ31および第2カウンタ32は、単位処理時間を繰り返し計時する。制御部50は、バス使用要求RQkの発生元のバスマスタにバスの使用許可GRkを与える手段であり、複数のバスマスタ#kのうち高優先度バスマスタについては、各単位処理時間において、各高優先度バスマスタのバス使用時間が各高優先度バスマスタについて予め定められたバス使用時間上限値を越えないことを限度として、優先的にバスの使用を許可する。

(もっと読む)

バスアービタ

【課題】複数のバスマスタからのバス獲得要求のうち、第1のバスマスタのデータ転送効率が確約されるように調停することができるバスアービタを得る。

【解決手段】第1のバスマスタに相当するデバイスのスキャナ3は、一定速度で原稿をスキャンし、次々とラスタ形式でシステムバス上のメモリ2に一定量の画像データを転送する。システム制御部4は、スキャナ3、通信系デバイスであるIEEE1394(5)と通信を行い動作状態に関する各コマンド、ステータスのやりとりを行う。本構成において、バスアービタが適用されている装置で特定の事象が発生することにより発生する第1のバスマスタからのバス獲得要求が存在する場合に、事象の発生を検出して事象発生信号として出力し、事象発生信号を受け、第1のバスマスタ以外のバスマスタからのバス獲得要求に対して、特定の事象が発生してない通常の場合より、バス使用権を与える頻度を制限する。

(もっと読む)

アクセス調停回路

【課題】複数の演算処理装置からのアクセス要求の実行が、際限なく待たされることを抑制することができるアクセス調停回路を提供する。

【解決手段】複数の演算処理装置からのアクセス要求を受信するアクセス順序制御部31と、複数のアクセス要求を記憶するアクセス要求記憶部32と、複数のアクセス要求にそれぞれ優先順位を付与してアクセス要求記憶部32に当該優先順位の順番に記憶させる優先順位付与部33と、アクセス要求記憶部32により、アクセス要求が新たに記憶される場合、当該新たに記憶されるアクセス要求の優先順位に基づいて既に記憶されているアクセス要求の優先順位を動的に変化させる優先順位変更部34とを備え、アクセス要求記憶部32は、複数のアクセス要求を記憶順にメモリコントローラ4を介してメモリ5へ送信するようにした。

(もっと読む)

ダイレクトメモリアクセスコントローラ

【課題】 1回のDMA転送要求で転送されるデータ列に、圧縮データと非圧縮データとを混在させることができるDMAコントローラを提供することである。

【解決手段】 DMAC4は、DMA転送要求ごとに、転送元データをDMA転送する。1回のDMA転送要求で転送される転送元データは、1または複数のブロックからなり、ブロック単位で圧縮データと非圧縮データとが混在可能である。DMAC4は、圧縮データを伸張する伸張回路48を含み、圧縮データについては、伸張回路48による伸張を行いつつ、転送先へ転送し、非圧縮データについては、伸張回路48による伸張を行うことなく、転送先へ転送する。

(もっと読む)

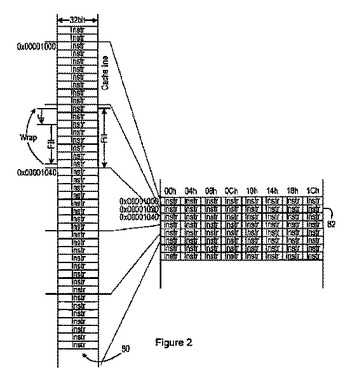

浅いエージェント毎のキューを伴うブロックしないアドレス・スイッチ

一実施形態では、スイッチは、相互接続に結合されるように構成される。スイッチは、複数の記憶域及び複数の記憶域に結合されたアービタ制御回路を備える。複数の記憶域は、複数のエージェントにより送信された複数の要求を格納するように構成される。アービタ制御回路は、複数の記憶域に格納されている複数の要求の間のアービトレーションを行うように構成される。選択された要求は、アービトレーションの勝者であり、スイッチは、選択された要求を複数の記憶域のうちの1つから相互接続上に送信するように構成される。他の実施形態では、システムは、複数のエージェント、相互接続、エージェントと相互接続とに結合されたスイッチを備える。他の実施形態では、方法が考察される。  (もっと読む)

(もっと読む)

DMA制御装置

【課題】 競合する複数のDMA要求の調停をするに際し、DMA実行順序を決定するための比較情報を減少させ、調停回路の回路規模を減らすとともに、制限時間内にDMA転送を行う。

【解決手段】 各DMA要求コア101,102,103からDMA要求を行う際に、DMA転送の内容(転送開始アドレス、転送長、DMA転送で格納又は読み出される対象資源、読み出し/書き込みの区別等)を表すDMA転送情報31,32,33とともに、DMA実行開始要求時刻情報21,22,23を転送する。DMA実行開始要求時刻は、DMA実行終了要求時刻からDMA転送の所要時間を差し引いて得られ、アービタ装置100に転送される。アービタ装置100では、DMA実行開始要求時刻を見ながらDMAの実行順序を決定し、この順序に従ってDMAが実行される。

(もっと読む)

データ転送処理装置

【課題】柔軟で適切なバスのアービトレーションの実現と、装置構成の複雑化や装置コストの上昇等の回避とを、それぞれ両立させる。

【解決手段】共通バス1と、前記共通バス1を使用してデータ転送を行う複数のバスマスタA1〜Zと、各複数のバスマスタA1〜Zからの共通バス使用要求に対する調停を予め設定されている優先順位に基づいて行うバスアービタ2と、前記複数のバスマスタA1〜Zの一部である二つのバスマスタA1,A2について、そのバスマスタA1,A2によるデータ転送方式に応じたタイミングで、当該二つのバスマスタA1,A2間の優先順位を入れ換える要求切換手段4とを備えて、データ転送処理装置を構成する。

(もっと読む)

バスシステム、スレーブ装置、バスシステム制御方法及びプログラム

【課題】 ライブロックが発生しないようにしたスレーブ装置と、ライブロックが発生する危険性はあるが、優先順位が高いマスタ装置が優先的に使用できるスレーブ装置とを混在させたバスシステムを提供する。

【解決手段】 バスアービタ3は、複数のマスタ装置がバス使用要求があった場合、固定的に定められている優先順位に従ってバス使用権を与えるマスタ装置を決定する。スレーブ装置2-1〜2-nの内、一部のスレーブ装置は、或るマスタ装置1-iから処理要求が送られてきたとき、他のマスタ装置1-jからの処理要求に従った処理を実行中であれば、そのマスタ装置1-iのマスタ番号を保持しておき、上記処理要求に従った処理が完了した後、保持しているマスタ番号に従って、次に優先的に処理要求を受け付ける優先マスタ装置を決定する。

(もっと読む)

1 - 20 / 24

[ Back to top ]