Fターム[5B061CC09]の内容

Fターム[5B061CC09]の下位に属するFターム

割込みマスクレジスタ (13)

Fターム[5B061CC09]に分類される特許

1 - 20 / 40

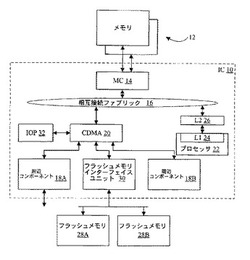

周辺コンポーネントのための高プライオリティコマンドキュー

【課題】集積回路の外部インターフェイスをコントロールする装置を提供する。

【解決手段】一実施形態において、周辺コンポーネントは、周辺インターフェイスを経て転送を行うためにコマンドのセットを記憶するように構成された低プライオリティコマンドキューと、そのインターフェイスを経て転送を行うためにコマンドの第2セットを記憶するように構成された高プライオリティコマンドキューとを備えている。低プライオリティキューにおけるコマンドは、コマンドの第2セットを実行するためにコマンドのセットに割り込むところのポイントを識別する指示を含む。コントロール回路が低プライオリティコマンドキューに結合され、指示に応答して低プライオリティキューからのコマンドの処理に割り込み、高プライオリティコマンドキューからのコマンドを処理する。

(もっと読む)

集積回路装置及びその制御方法

【課題】USBホストコントローラを有する集積回路装置において消費電力を削減する。

【解決手段】集積回路装置は、USBを介してUSBデバイスとの間で通信を行うUSBホストコントローラと、通常動作状態において、前記USBホストコントローラを制御して、前記USBホストコントローラと前記USBデバイスとの間の通信が可能になるようにするための処理を行い、スタンバイ状態において動作を停止する第1プロセッサと、前記スタンバイ状態において、前記USBホストコントローラを制御して、前記通常動作状態に移行するための処理を行い、前記通常動作状態において動作を停止する第2プロセッサとを有する。前記USBホストコントローラと前記USBデバイスとの間で通信可能な状態を維持したまま、前記USBホストコントローラに対する制御が、前記第1プロセッサによる制御と前記第2プロセッサによる制御との間で切り替えられる。

(もっと読む)

マスタデバイスおよびバスシステム

【課題】CPUの負担を抑えながら、簡単な構成でスレーブデバイスの割り込み要求を監視することができるマスタデバイスを実現する。

【解決手段】本発明に係るマスタデバイス3は、I2Cバスを介してスレーブデバイス2a〜2eに接続され、各スレーブデバイス2a〜2eに割り当てられたデバイスアドレスを指定することで各スレーブデバイス2a〜2eとの通信を行い、スレーブデバイス2a〜2eのうち、割り込み機能を有するスレーブデバイス2a、2b、2d、2eから、マスタデバイス3およびスレーブデバイス2a〜2eを制御するCPU4への割り込み要求を周期的に監視する割り込み監視回路31を備える。

(もっと読む)

データ転送システム及びデータ転送方法

【課題】演算装置から周辺装置へのアクセス時間及びアクセス回数を削減し、消費電力を低減できるデータ転送システムを提供する。

【解決手段】周辺装置4は、演算装置1に割込要求信号を送信する前に、周辺装置4のレジスタセット4r内のデータを主記憶装置2にDMA(Direct Memory Access)転送する。演算装置1は、割込要求信号に応答して、周辺装置4にアクセスすることなく、主記憶装置2にDMA転送されたレジスタセット4r内のデータを読み出す。

(もっと読む)

割込み制御装置、割込み制御方法及び集積回路

【課題】プロセッサが省電力状態になってすぐに割込み要求が入力されることを防ぎ、プロセッサの通常状態から省電力状態への復帰回数を抑制する割込み制御装置を提供する。

【解決手段】プロセッサが省電力状態に遷移するときに、カウントを開始するカウンタタイマと、デバイス毎に設定されている割込み要求の保留許容時間を予め記憶している許容時間記憶手段と、前記プロセッサが省電力状態のときに発生した割込み要求の要求元のデバイスに対応して設定されている前記保留許容時間の中で、最も短い保留許容時間と前記カウンタタイマの値とを比較し、前記カウンタタイマの値が前記最も短い保留許容時間より小さい場合は、割込み要求の出力を保留し、前記カウンタタイマの値が前記最も短い保留許容時間以上の場合は、前記プロセッサに対して割込み要求を出力する出力手段とを備えることを特徴とする割込み制御装置。

(もっと読む)

ホスト装置、周辺装置、通信システム、および、通信方法

【課題】クロック信号に同期してデータ送受信を行う通信システムでは、ホスト装置がクロック信号の出力を停止すると、周辺装置からホスト装置へデータ転送ができず、周辺装置からホスト装置へ割込み要求を速やかに伝えることができない。

【解決手段】クロック信号の出力が停止している際に、周辺装置201からホスト装置200への割込み要求を、クロック信号用の信号線を用いることで、ホスト装置200へ伝える。ホスト装置200は、この割込み要求を受信するとクロック信号の出力を再開し、周辺装置201との間でデータの送受信を再開できるようにする。これにより、ホスト装置200からクロック信号の出力が停止している場合であっても速やかに周辺装置201からホスト装置へ割込み要求を伝えることが可能となる。

(もっと読む)

情報処理システム

【課題】 情報処理システムの性能を低下することなく、割り込み処理時間を短縮する。

【解決手段】 割り込み制御回路は、低速スレーブからプロセッサへの割り込み要求に応答して、リマップ信号をアサートし、低速スレーブの情報レジスタに格納されている情報を読み出す。割り込み制御回路は、読み出した情報を割り込み処理専用のバッファに書き込む。切替回路は、リマップ信号のネゲート中に、プロセッサから情報レジスタへの読み出しアクセス要求を低速スレーブに供給し、リマップ信号のアサート中に、バッファから情報を読み出すために読み出しアクセス要求を割り込み制御回路を介してバッファに供給する。プロセッサからの読み出しアクセス要求に応答して、情報レジスタの代わりに割り込み処理専用のバッファにアクセスすることで、プログラムの実行効率を低下させることなく、情報を読み出しできる。

(もっと読む)

中央演算処理装置、制御システム、及び、ポート設定方法

【課題】ウエイト動作が継続する状態になってもウエイト信号を出力する低速外部機器以外の外部機器の制御を行うことができる演算処理装置、当該演算処理装置を備えた制御システム及び中央演算処理装置によって実施されるポート設定方法を提供する。

【解決手段】立ち上がり時にウエイト端子T1に対してウエイト信号が入力されている場合、CPU2が、LCDコントローラIC7に接続されるポートP4及びウエイト端子T1の設定を行わずに複数のポートP1〜P6のうちLCDコントローラIC7に接続されるポートP4を除いて設定を行う。

(もっと読む)

コンピュータシステムおよび割込要求処理方法

【課題】中央処理装置の割込み処理にかかる負荷を低減させて、中央処理装置の処理効率の向上を図ること。

【解決手段】コンピュータシステム100において、割込要求処理装置Mは、デバイスDから出力される所定の処理の終了を通知する割込み要求を受け付ける。割込要求処理装置Mは、デバイスDから割込み要求を受け付けた回数が、所定回数Fと一致するか否かを判定する。割込要求処理装置Mは、デバイスDから割込み要求を受け付けた回数が所定回数Fに達するまで、デバイスDに対して所定の処理の実行要求を出力する。割込要求処理装置Mは、デバイスDから割込み要求を受け付けた回数が所定回数Fと一致する場合、CPU101に対して割込み要求を出力する。

(もっと読む)

コンピュータシステムにおける割り込み通信技術

コンピュータシステム内で効率的な割り込み通信を可能とする技術を提供する。一実施形態では、拡張プログラム制御割り込みコントローラ(APIC)が、メモリマップドI/O(MMIO)を利用することなく、様々なインタフェース命令または処理を利用してAPICインタフェースレジスタ内の一式のビットを介してインタフェースされる。 (もっと読む)

電子機器

【課題】ICの端子数を削減して、コストを抑えることが可能な電子機器を提供する。

【解決手段】基板50に実装されたメインIC80と、このメインIC80に制御される従属IC70とで通信を行う電子機器であって、メインIC80と従属IC70は、端子間をバス60を通じて接続され、メインIC80は、従属IC70からの割り込み要求を示す割り込み要求信号を受信する受信部85を有し、従属IC70は、割り込み要求信号を発生させる割り込み制御回路72と、割り込み要求信号をメインIC80による制御を介すことなくバス60を通じて受信部85に転送する転送回路72とを有する。

(もっと読む)

マルチプロセッサシステムおよびマルチプロセッサシステムの割込み制御方法

【課題】割込み優先度に従って適切な割込み応答性を確保しつつ、システム全体の処理効率を向上するマルチプロセッサシステムを提供する。

【解決手段】レジスタをそれぞれ有する複数のプロセッサと、複数のI/Oデバイスと、割込み生成器とを備えるマルチプロセッサシステムの割込み制御方法であって、対応するプロセッサが割込みを許容する許容度を示す割込み許容度を前記レジスタに設定する設定ステップと、各I/Oデバイスからの割込みに対しての優先度を示す割込み優先度を記憶部に記憶させた前記割込み生成器が、I/Oデバイスからの割込み要求を受信し、前記割込み要求を、前記I/Oデバイスの割込み優先度とともに前記複数のプロセッサに通知する通知ステップと、前記割込み優先度に比べて低い割込み許容度が記憶されるレジスタを有するプロセッサのいずれかに、前記割込み要求を受理させる割込み受理ステップとを含むことを特徴とする。

(もっと読む)

データ処理装置及びデータ処理装置におけるバスアクセス制御方法

【課題】従来のデータ処理装置では、例外処理時に内部バスの無効化を解除することができず、例外処理が十分に行えない問題があった。

【解決手段】本発明にかかるデータ処理装置は、内部バスを介して接続される周辺装置にアクセスを行う演算回路11と、演算回路11から内部バスへのアクセスの有効状態と無効状態とを切り替える内部バス接続回路12と、周辺装置において発生したエラーに基づき演算回路11に例外発生通知信号ERRNを出力する例外通知制御回路19と、例外発生通知信号ERRNの通知に応じて内部バス接続回路12に演算回路11から内部バスへのアクセスの無効化を指示し、演算回路11における例外発生通知信号ERRNに基づいた例外処理の開始に応じて内部バス接続回路12に演算回路11から内部バスへのアクセスの無効化解除を指示するバス無効化制御回路18と、を有する。

(もっと読む)

エッジ検出のみの割込み機能を有するCPUおよび電子機器

【課題】エッジ検出のみの割込み機能を有するCPUが搭載された電子機器において、割込み信号としてノイズが流入した場合の電子機器の誤動作を防ぐ。

【解決手段】CPU1のファームウェアは、割込みが発生すると、端子I/Oから入力された分周信号の値とトグルフラグを比較する。トグルフラグの値と2分周信号の値が合致した場合、ファームウェアは該割込み信号を真の割込み信号と認識し、トグルフラグを反転し、割込みによるカウンタを+1し、所定の割込み処理動作を行う。トグルフラグ値と分周信号の値が合致しない場合は、ファームウェアは該割込み信号をノイズによる偽の割込み信号と認識する。その際、トグルフラグをそのまま保持し、割込みによるカウンタの値もそのまま保持し、割込み待ちに戻る。

(もっと読む)

バス結合装置、ならびに割り込み制御ための方法およびプログラム

【課題】本発明により、演算処理装置の負荷軽減およびシステム全体の性能向上が可能とする。

【解決手段】第1のバスを介して結合された複数の入出力装置から、演算処理を行う演算処理装置に対して発行される割り込み処理要求を受信し、前記割り込み処理要求を行った前記入出力装置にアクセスして前記割り込み処理要求の要因を表す割り込み要因情報を取得し、第2のバスを介して結合された前記演算処理装置に対する割り込みを許可するか否かを、各前記入出力装置に対して各々の割り込み要因ごとに定めた割り込みマスク情報を保持し、前記割り込み処理要求を行った入出力装置と、取得された割り込み要因との組に対する割り込みが許可されているとき、前記割り込み処理要求を行った入出力装置が前記取得された割り込み要因に基づき前記割り込み処理要求を行っていることを表す割り込み情報を前記演算処理装置に対して通知する。

(もっと読む)

ホスト負荷調整機能付周辺回路

【課題】周辺回路による割込み、メモリバス帯域の利用や、データの処理スループットに制限をかける事により、周辺回路とホストCPUによるデータ処理量がバランスする様に容易に制御可能であるホスト負荷調整機能付周辺回路を提供する。

【解決手段】ホスト負荷調整機能付周辺回路105が発生する割込み要求113の間隔の最小値を設定するための調整制約設定部121と、割込み要求113の発生タイミングをカウントするための周期カウンタ124とを備え、周期カウンタ124の値と調整制約設定部121に設定された間隔とを比較することにより、設定間隔より短い間隔で発生する割込み要求113を抑制する。

(もっと読む)

情報処理装置、オーディオ装置および情報処理方法

【課題】割込みソフトウェアを削減しCPUの負荷を低減し動作効率を向上させる情報処理装置を提供する。

【解決手段】本発明の情報処理装置は、プログラムを実行するCPU4と、複数の周辺デバイス1a〜1cと、周辺デバイス1a〜1cからの割込み要求を受け付けてCPU4に通知する割込みコントローラ3とを備え、第1の周辺デバイス(例えば周辺デバイス1a)は、割込み要求の出力先を割込みコントローラ3とするか第2の周辺デバイス(例えば周辺デバイス1b)とするか切り替え可能な切り替え部2aを有する。

(もっと読む)

制御システム、送信側制御装置、受信側制御装置、制御方法およびプログラム

【課題】同期型サイクリック通信を行う制御装置間において、ホットライン通知(割り込み通知)を、連続的かつ順次的に発行および処理可能とする制御システム、送信側制御装置、受信側制御装置、制御方法およびプログラムを得る。

【解決手段】第1の制御装置が、自制御装置においてホットライン通知送信要求が生じた場合にホットライン通知の新旧を判別するためのホットライン通知毎に固有の識別情報を生成する識別情報生成手段と、識別情報を割り込み処理で利用する割り込み処理用データとともに第2の制御装置に送信する制御を行う送信制御手段と、を備え、第2の制御装置が、第1の制御装置から送信された識別情報および割り込み処理用データを受信して管理する受信制御手段と、識別情報が前回受信した識別情報から更新されている場合のみ、受信した識別情報および割り込み処理用データに基づいて割り込み処理を実行する割り込み処理実行手段と、を備える。

(もっと読む)

割り込み処理装置及び割り込み処理方法

【課題】デバイスによるメモリへのデータ書き込みと、CPUによるメモリへのデータ読み出しの順序性を保証する。

【解決手段】割り込み処理装置1はPCIバス(L1〜L6)を介してデバイス3から出力される書き込みデータを格納し、デバイス3から出力される割り込み通知に基づいて前記書き込みデータをメモリ4に書き込み、書き込み終了後にCPU5へ割り込み通知を行う。

(もっと読む)

割込み制御回路、回路基板、電気光学装置及び電子機器

【課題】非同期型のCPUに対する割込み制御が可能であり、高速化及び低消費電力化を実現することが可能な割込み制御回路を提供する。

【解決手段】1つ若しくは複数の外部回路からの割込み要因信号に応じて、割込み処理を要求するための割込み信号と、割込み要因信号に対応する割込み処理プログラムの格納先を示す割込みベクトル信号とを割込み処理実行回路に出力する割込み制御回路であって、前記割込み処理実行回路から入力される、割込み処理の受付可能状態を示す割込み受付信号に同期して前記割込み信号を出力する。

(もっと読む)

1 - 20 / 40

[ Back to top ]