Fターム[5B061GG12]の内容

バス制御 (3,799) | システム構成 (311) | マルチプロセッサシステム (131) | 密結合 (38)

Fターム[5B061GG12]の下位に属するFターム

Fターム[5B061GG12]に分類される特許

1 - 10 / 10

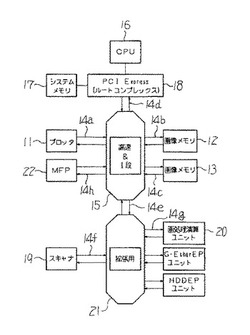

画像形成システム

【課題】PCI Express規格の高速シリアルバスを有効に活用することで、ライン同期転送のタイミング制約があっても、高速な画像データ出力や同時転送を可能にする。

【解決手段】画像出力部(Engine TX)のメモリリードトランザクション(読出し要求コマンドMemReadReq.)のトラフィッククラスTCのプライオリティを画像入力部(Engine RX)のメモリライトトランザクション(メモリ書込み要求コマンドMemWriteReq.)のトラフィッククラスTCのプライオリティより高くし、かつ、メモリリードトランザクションが全て発行されてからメモリライトトランザクションが発行されるようにストリクトプライオリティを設定することで、ライン同期転送のタイミング制約があっても高速で画像データの出力が可能となり、読出し要求コマンドMemReadReq.をライン有効期間XLGATE内に受信でき、複数の画像データ転送を同時に行うことができる。

(もっと読む)

マイコン、処理同期方法

【課題】一方のコアから他方のコアに割込みによりイベントを通知する際、イベントの誤通知を検知できるマイコンを提供すること。

【解決手段】第1のコア52と第2のコア53間で通信する通信手段43と、第1のコアと第2のコアが共有する共有メモリ51と、外部信号を取得して第1の処理を実行し、第1の処理毎に所定情報を共有メモリに書き込む第1の処理手段55と、通信手段を介して第2のコアに処理要求を出力する処理要求手段33と、処理要求をトリガーに第2の処理を実行する第2の処理手段56と、を有するマイコン100において、第2のコアは、処理要求を受け付けた場合、共有メモリから最新の所定情報と前回の所定情報を読み出し、最新の所定情報と前回の所定情報に規定された関係がある場合のみ、第2の処理手段に第2の処理の実行を許可する比較手段57、を有する。

(もっと読む)

半導体集積回路、データ処理装置

【課題】 回路規模を増大させることなく、アルゴリズムを効率よく実装することが可能な、プロセッサアレイ構成を提供する。

【解決手段】 プロセッサアレイにおける入出力制御手段間の経路の内少なくともひとつを、データ処理フローに合せて、所定の方向に多重に持たせることで、効率よく実装することが可能となる。また、上記所定の方向を多重化する代わりに、その方向とは反対方向の経路を省くことで、回路規模の増大を防ぐことを特徴とする。

(もっと読む)

データ処理装置、データ処理方法、及びプログラム

【課題】簡便なデータの優先度判定機構によりデータ処理装置のパケット転送効率を向上する。

【解決手段】他のモジュールからパケットを受信する受信部と、受信したパケットが保持するデータを自モジュールで処理すべきかを、パケットに含まれており、処理順序を示す情報である第1の情報により判定する判定部と、自モジュールで処理すべきと判定された場合にデータを処理する処理部と、処理されたデータ、及び、処理されるべきデータが処理されずに保留されたことを示す第2の情報、の何れか一方と、第1の情報とを含むパケットを生成する生成部と、パケットを第1の情報に従って次に処理すべきモジュールに送信する送信部と、を備え、第1及び第2の情報により、受信されたパケットが自モジュールの次の処理順序のモジュールにより処理すべきであった処理を保留されたデータを含む場合、送信部はパケットがリングバスを1周するのに要する時間よりも長い送信間隔で送信を行う。

(もっと読む)

ネットワークシステム、情報処理装置及びネットワークシステムの制御方法

【課題】ネットワークシステム、情報処理装置及びネットワークシステムの制御方法において、レイテンシ及びバンド幅の両方を向上可能とすることを目的とする。

【解決手段】クロスバスイッチと、前記クロスバスイッチに接続されたポートを有する複数のクロスバインタフェースと、前記複数のクロスバインタフェースのうち、使用頻度が所定値以上のポートの組を形成するクロスバインタフェース同士を直接接続するバイパスルートを備えるようにする。

(もっと読む)

コンピュータ装置及びそのデータ転送方法

【課題】 リクエストが圧縮された演算器の数や圧縮のパターン数が多い場合でも圧縮情報のビット数を小さくすることが可能なデータ転送方法を提供する。

【解決手段】 番号が連続する複数の演算器からのメモリリクエストが一のメモリポートに競合する場合には、これら複数のメモリリクエストを1つに圧縮する。この際、演算器番号情報とメモリアドレス特定用情報とを含む圧縮情報を生成する。演算器番号情報は、圧縮される複数のメモリリクエストの発行元である複数の演算器のうち特定の演算器の番号を示す情報である。メモリアドレス特定用情報は、前記一のメモリポートに含まれるメモリアドレスのうち何れのメモリアドレスに対するリクエストを圧縮したのかを示す情報である。リプライが前記一のメモリポートから戻ってくると、該リプライを圧縮情報に基づいてリクエスト発行元の演算器に分配する。

(もっと読む)

半導体装置、回路基板及びチャネル型バスの相互接続方法

【課題】複数の機能ブロックを有する半導体装置において、各ブロック間のバス配線数を減少させること。

【解決手段】 マスタ機能ブロックとスレーブ機能ブロックとを有する複合機能ブロックを複数配置し、各複合機能ブロックにそれぞれI/F部をバス接続すると共に、I/F部間を接続するための複数の相互接続部を設けた半導体装置において、I/F部は、複合機能ブロックに設けられたマスタ機能ブロック及びスレーブ機能ブロックとの間でそれぞれ入力バス及び出力バスにより接続される一方、一つの入力バス及び出力バスで相互接続部と接続され、しかも、相互接続部間が少なくとも一つの入力バス及び出力バスで接続される。

(もっと読む)

集積回路装置、通信制御装置、マイクロコンピュータ及び電子機器

【課題】ホストスレーブ間でポインターの共有の必要がなくボトルネックの発生させないプロセッサ間通信が可能な集積回路装置、マイクロコンピュータ及び電子機器の提供。

【解決手段】本集積回路装置10は、外部CPU200に接続されるスレーブ側の集積回路装置であって、内部CPU20と、内部CPUと外部のCPUとのプロセッサ間通信処理を行うプロセッサ間通信処理部40とを含み、前記プロセッサ間通信処理部40は、外部CPUがコマンドを設定可能な第1のレジスタ50と、第1のレジスタ50にコマンドが書き込まれると、内部CPU20に対し第1の割り込み信号61を出力する第1の割り込み信号生成回路60と、内部CPU20がコマンドを設定可能な第2のレジスタと、第2のレジスタにコマンドが書き込まれると、外部CPU200に対し第2の割り込み信号を出力する第2の割り込み信号生成回路60とを含む。

(もっと読む)

データ専用バスを有する無線機

【課題】無線通信の高度化に対応可能な無線通信装置のハードウェア構成を提供する。

【解決手段】メインプロセッサと各構成要素の間で主に制御信号を転送する制御バスと、サブプロセッサを含むプロセッサユニットと外部インタフェースの間で主に送受信データを転送するデータバスを分離する。また、サブプロセッサはプロセッサユニットを構成し、本発明のソフトウェア無線機は複数のプロセッサユニットを備えることを可能とする。プロセッサユニット間は専用のユニット間インタフェースで接続される。プロセッサユニットは複数のサブプロセッサを備えることが可能であり、複数のサブプロセッサはプロセッサ間インタフェースを介してシリアルに接続される。

(もっと読む)

中央処理装置用通信制御回路

【課題】一のCPUが通信処理中であっても、他のCPUが一のCPUからは独立して通信を行うことができるとともに、マルチポートメモリのポート数によって制限されることなく、CPUの数を拡張することが可能なCPU用の通信制御回路を提供する。

【解決手段】通信制御回路10は、中央処理装置11、14の各々に接続された入力用先入れ先出しメモリ12、15と、中央処理装置11、14の各々に接続された出力用先入れ先出しメモリ13、16と、入力用先入れ先出しメモリ12、15及び出力用先入れ先出しメモリ13、16に接続され、入力用先入れ先出しメモリ12、15を介しての中央処理装置11、14への信号の入力及び出力用先入れ先出しメモリ13、16を介しての中央処理装置11、14からの信号の出力を制御する調停回路17と、からなる。

(もっと読む)

1 - 10 / 10

[ Back to top ]