Fターム[5B062CC05]の内容

マイクロコンピュータ (2,258) | 種類 (331) | シングルチップマイクロコンピュータ (204) | 特定用途向け (31)

Fターム[5B062CC05]の下位に属するFターム

DSP (9)

Fターム[5B062CC05]に分類される特許

1 - 20 / 22

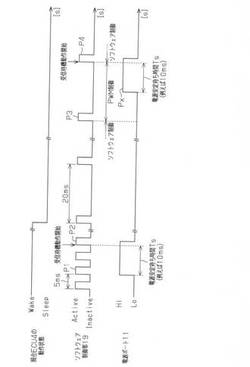

IC出力ポート切換制御装置

【課題】電源を省電力化することができるIC出力ポート制御装置を提供する。

【解決手段】ワイヤレスキーシステムの照合ECU4は、自身のメモリに記憶されたプログラムにて所定周期で動作するソフトウェア制御部19と、自身に元から備わるPWMリソースとを有する。照合ECU4のスリープ中、車両受信機が受信待機動作をとるパルスP4の1周期前のパルスP3で電源ポート11をソフトウェア制御からPWM制御に変更することにより、電源ポート11をPWM制御に切り換える。このため、PWM制御のパルスPxがHiレベルに立ち上がってからの時間が電源安定待ち時間Tsとして車両受信機に供給される。

(もっと読む)

マイクロコンピュータ及び画像表示装置

【課題】LCDダイレクトドライブのための制御にハードウェアを用いることで、ユーザプログラム作成の負担軽減を図る。

【解決手段】クロック信号を形成可能なタイマパルスユニット(103)と、表示用データを液晶ディスプレイへDMA転送可能なDMAコントローラ(110)と、上記DMA転送に用いられる第1クロック信号と、上記液晶ディスプレイへの表示に用いられる第2クロック信号とを選択的に上記液晶ディスプレイのクロック入力端子へ伝達可能なセレクタ(105)とを設ける。また上記セレクタの選択状態を設定可能なレジスタ(106)と、上記レジスタの設定情報に基づいて、上記セレクタの選択状態を上記DMA転送に同期して制御するための制御論理(107)とを設ける。ユーザプログラムにおいては、LCDダイレクトドライブのための制御に関して上記レジスタへの設定を行うだけで良いので、ユーザプログラム作成の負担を軽減できる。

(もっと読む)

マイクロコンピュータ

【課題】大きなコストや製造工数を要することなく使用できる周辺機能の組合せに対して融通性を有するマイクロコンピュータを提供する。

【解決手段】中央処理装置(2)、動作モードの制御を行うシステムコントローラ(5)、不揮発性メモリ(4)、及び複数の周辺回路(6〜17)を備えたマイクロコンピュータにおいて、システムコントローラは、これに入力されるモード信号(SCMD0,SCMD1)に応じて不揮発性メモリから初期化データ(SYSCONFIG)を読み出して夫々の周辺回路の活性又は非活性を決定し、決定する活性及び非活性の組合せの態様を、モード信号の値によって決める。マイクロコンピュータの設計段階で予め想定し得る周辺機能をチップに搭載し、活性化する周辺機能の組合せを規定する数通りの初期化データを不揮発性メモリの初期的に書き込み、その中からモード信号に応じた初期化データを選択できるように対応付けておく。

(もっと読む)

映像処理用集積回路および音声処理用集積回路

【課題】映像音声機器の開発で得られた設計資産が他の種類の映像音声機器にも流用することが可能な映像処理用集積回路および音声処理用集積回路を提供する。

【解決手段】CPUを含むマイコンブロック2と、外部装置と映像及び音声ストリームの入出力を行うストリームI/Oブロック4と、ストリームI/Oブロック4に入力された映像及び音声ストリーム等の圧縮及び伸張の少なくとも1つを含むメディア処理を実行するメディア処理ブロック3と、メディア処理ブロック3でメディア処理された映像及び音声ストリームを映像及び音声信号に変換して外部機器に出力等するAVIOブロック5と、マイコンブロック2、ストリームI/Oブロック4、メディア処理ブロック3及びAVIOブロック5と外部メモリ9との間のデータ転送を制御するメモリIFブロック6とを備える。

(もっと読む)

処理アーキテクチャ

ポータブル通信デバイスのための処理装置が提示される。装置は、中央処理装置、第1および第2のデジタル信号処理ユニット、中央処理装置と第1のデジタル信号処理ユニット間で共有されるデータを格納するように適合された第1のデュアル・ポート・メモリ・ユニット、および中央処理装置と第2のデジタル信号処理ユニット間で共有されるデータを格納するように適合された第2のデュアル・ポート・メモリ・ユニットを備える。第1のデュアル・ポート・メモリ・ユニットは、中央処理装置を使用することなく、第1と第2のデジタル信号処理ユニット間で共有されるデータを格納するように適合される。  (もっと読む)

(もっと読む)

大規模集積回路装置

【課題】大規模集積回路装置において、少ない回路規模の追加で既存回路との後方互換性を保ったまま新規機能を実現し、しかも既存回路との互換動作モードと新規動作モードとの切り替えに起因する動作不良を防止する。

【解決手段】大規模集積回路装置(LSI)100内に、それぞれ独立して信号処理動作を行う複数の回路ブロックA〜Cを構成するとともに、該回路ブロックAを、既存ゲーム機との互換性を持つ互換回路とし、該回路ブロックBおよびCを、該既存ゲーム機にはない新規機能を実現する新規回路とし、該回路ブロックA〜Cの何れかひとつを選択するためのブロック選択信号107〜109、および自己の動作停止のための信号を出力するシステム設定回路102を該LSI内に搭載し、該システム制御回路102を、CPU101などの制御回路により制御するようにした。

(もっと読む)

半導体集積回路及び半導体集積回路の制御方法

【課題】 マスタ回路が非活性状態のとき、そのマスタ回路に割り当てられたスレーブ回路が利用されず、システム資源の利用効率が低下してしまう。

【解決手段】 半導体集積回路50は、マスタ回路2の動作状態に応じて、マスタ回路2に割り当てられたスレーブ回路6のM2領域15をマスタ回路4に割り当てる。つまり、マスタ回路2の動作状態に応じて、マスタ回路2に割り当てられたスレーブ回路6のM2領域15は、マスタ回路4に割り当てられる。これによって、半導体集積回路50のシステム資源の利用効率が向上する。

(もっと読む)

半導体装置

【課題】クロックサイクルに同期する回路による電力消費状態の相違に起因する電源電圧の変動を容易に抑制する。

【解決手段】クロックサイクルに同期動作しアクセスを要求することができる第1回路(2)がアクセス要求に対する応答を待っているとき、電流消費動作を行う電流消費回路(20)を採用する。前記電流消費回路は第1回路に指示された動作の休止期間における消費電流量の低下を抑制するために前記クロックサイクル毎に電流消費動作を行い、電流消費動作を行う複数個の電流消費ユニット(21)を有する。前記第1回路の動作休止期間に、電流消費動作を行う前記電流消費ユニットの数は可変化能にされる。電流消費回路による消費電流量は動作選択される電流消費ユニットの数によって設定されるから、予めその電流量を見積もることは難しい場合にも容易に対応することができる。

(もっと読む)

エンジン制御用電子制御装置およびマイクロコンピュータ

【課題】 マルチコア構成及びキャッシュメモリ搭載構成の少なくとも一方が採用されたマイクロコンピュータを備えたエンジン制御用電子制御装置において、エンジン停止中に車載バッテリの電源により特定の制御処理を行う際の消費電力を効果的に低減する。

【解決手段】 2つのCPUコアとROMキャッシュメモリ及びRAMキャッシュメモリを備えたエンジン制御マイコンにおいて、エンジン制御中は、CPUコア及びキャッシュメモリをフルに使用して最高の処理能力を発揮できるエンジン制御モードが選択される(S140)。一方、IGSWのOFF時(エンジン停止中)、ACCSWがONされた場合はリプログモードが選択され(S160)、CAN通信パケットが受信された場合はCANウェイクアップモードが選択され(S180)、ソークタイマICにより所定時間経過が検知された場合はKEYOFFエバポモードが選択される(S200)。

(もっと読む)

マイクロコンピュータの制御回路及び制御方法

【課題】複数の入力信号の組み合わせとその入力タイミングとに基づいて制御を行うことは困難であるという問題があった。

【解決手段】マイクロコンピュータの制御回路は、複数の入力信号をラッチするとともに、所定のタイミングで前記ラッチした値をクリアする入力保持部(保持回路51−1〜51−n)と、前記ラッチした複数の値に基づいて、起動信号を生成する制御信号生成部(論理回路群52)と、を備える。入力保持部は、入力信号が変化するタイミングでラッチする。

(もっと読む)

半導体集積回路装置およびそれへのモード設定方法

【課題】 端子数を増加させることなく動作モードの設定を行える変換回路を備えた半導体集積回路装置を提供すること。

【解決手段】 シリアルデータとパラレルデータとの間の変換を行う変換回路12と、この変換回路に対して、シリアルデータからパラレルデータへ変換させる第1の変換モードとパラレルデータからシリアルデータへ変換させる第2の変換モードとのいずれか一方を設定するモード制御回路14とを有する半導体集積回路装置10は、モード制御回路に接続されて、変換の方向を指示する変換モード信号を入力する1つのモード入力端子MODE1と、変換回路による変換動作を行う前の初期化直後のデータ通信によって、パラレルデータ入出力端子の使用するビット数とシリアルデータ入出力端子の使用する端子数とを決定する動作モードを設定するための動作モード設定用レジスタ16とを有する。

(もっと読む)

電子制御装置

【課題】マイクロコンピュータの負荷を増加させることなく、A/D変換器の変換が実施されたか否かを判定することできる電子制御装置を提供する。また、DMAコントローラを備えている場合、さらに、DMAコントローラが異常か否かを判定することができる電子制御装置を提供する。

【解決手段】本発明の制御装置7は、CPU700と、RAM702と、DMAC704と、A/D変換器705とを備えている。A/D変換器705は、変換結果と変換実施回数の情報である識別子とを変換レジスタ705d〜705fに保存する。変換結果と識別子は、DMAC704によって、CPU700を介さずにRAM702に転送される。CPU700は、RAM702内に保存されている変換結果を読込む際に、識別子の値を識別子の期待値と比較することで、負荷を増加させることなく、DMAC704及びA/D変換器705の異常の有無を判定することができる。

(もっと読む)

電源ノイズ検出機能付き電子制御装置

【課題】正常な電圧印加をノイズとして検出しないようにしつつ、電源ラインにノイズが供給されたことを検出できるようにする。

【解決手段】マイコン8にて分圧回路10の電位V1と平滑化回路9の電位V2の大小を比較し、分圧回路10の電位V1が平滑化回路9の電位V2よりも大きいときには、モータ16の駆動を許可し、平滑化回路9の電位V2が分圧回路10の電位V1よりも大きくなると、モータ16の駆動を禁止する。これにより、万一バッテリ3が外れた場合に、モータ16の動作による電源電圧の低下を防止できる。また、パルス波とされる発電電圧がECU1に印加されたときに、平滑化回路9の電位V2が瞬間的に増加してしまうのではなく、徐々に増加する。このため、クランキング時のように、電源ライン4にパルス状の電圧が一定期間もしくは一定回数印加される状況になっても、それを排除して電源ノイズを検出できる。

(もっと読む)

演算処理装置

【課題】マイクロプロセッサにおいて、要求された処理速度を満たし、最大限の節電効果を達成する。

【解決手段】目標命令実行数の測定された命令実行数に対する偏差の比例・積分による制御値を演算する。制御値に応じて、選択されたパイプラインレジスタへのクロックの供給を停止し、信号はそのパイプラインレジスタをスルーさせるように制御することで、パイプラインの段数を減少させる統合処理をする。逆に、選択されたパイプラインレジスタへのクロックの供給を再開し、信号をクロックに同期して、そのパイプラインレジスタにラッチさせるようにパイプライン制御することで、パイプラインの段数を増加させる統合解除処理をする。変更される段数に応じて、パイプラインレジスタに供給するクロック周波数を変化させる。

(もっと読む)

半導体集積回路装置

【課題】回路の簡易化及びデータ入出力のタイミングの自由度を高くすることができる半導体集積回路装置を提供する。

【解決手段】IOコンフィグレーション・ブロック104は、入力グループPORT−Aを外部ピンの先頭にピン番号の正順に割り当て、出力グループPORT−Bを外部ピンの後尾にピン番号の逆順に割り当て、余った外部ピンにその他の機能グループOPTIONの信号を割り当て、その他の機能グループOPTIONの信号より入力グループPORT−Aの信号を優先して割り当てる。

(もっと読む)

IPコア及び複合IPコア

【課題】外部からの制御を全く必要としないで単体でも機能する完全自立形の基本モジュールを複数組み合わせて別の機能を発揮するIPコアを構成することができる基本モジュール及びIPコアを提供する。

【解決手段】本発明は、他のIPコアとの間で通信データを運ぶデータバス12に対してデータの入出力を司るI/Oインタフェース15と、所定の演算処理を実行するモジュール機能本体16と、同一IPコア内の他のIPコアモジュールとの間で所定のフォーマットのデータを運ぶシステム内バス14に対してデータの入出力を司るモジュール間インタフェース17と、I/Oインタフェース、モジュール機能本体、モジュール間インタフェースを統括制御するコントローラ18とを備えた基本モジュールを特徴とする。

(もっと読む)

回路内プログラミング構造を埋め込んだプロセッサ

【課題】回路内プログラミングを有する集積回路(10)が回路内プログラミングの命令セット自体を動的に変更させる。

【解決手段】構造は集積回路上のマイクロコントローラ(11)に基づいており、集積回路は命令を記憶する不揮発性メモリアレイの2以上のバンクを有し、回路内プログラミング命令セット(40)を含んでいる。デバイスは、そこに記憶された制御プログラムを使用して、相手との回路内プログラミング交換を確立し、必要な時に、回路内プログラミング命令セットを含むデータ及びソフトウェアを更新する。プロセッサとICPコードは回路内プログラミングの更新指令に応答し、第1メモリアレイ(17)からの回路内プログラミングセットのコピーを第2メモリアレイ(16)に書き込み、それを実行させ、外部ポートからのデータで第1メモリアレイの不揮発性メモリセルをプログラムする。

(もっと読む)

コンフィギュラブルロジックデバイスを有するマイクロコントローラ製品の高速作成およびコンフィギュレーション

マイクロコントローラまたはこれに類似の計算リソース、およびコンフィギュラブルロジックデバイスを含むマイクロコントローラ製品の高速作成およびコンフィギュレーションに適している方法および装置につき説明する。本発明の種々の実施形態は、新規なマイクロコントローラベースの製品および製品のファミリーを、高速かつコスト効率の良いやり方で開発し、これにより、このような製品を早期に市場に出すことを可能にする。本発明は、既存のマイクロコントローラブロックおよび既存のコンフィギュラブルロジックデバイスを組み合わせて、マイクロコントローラブロックがコンフィギュラブルロジックデバイスのコンフィギュレーションを行って、マイクロコントローラベースの製品に所望されるユニークなハードウェア特性を形成するように動作可能なユニークな製品を生成する。マイクロコントローラブロックは、製品がリセットされるとき、および/または電源投入の状態が認識されるときに、コンフィギュラブルロジックデバイスのコンフィギュレーションを行う。  (もっと読む)

(もっと読む)

半導体演算処理装置

【課題】メモリセルマットが複数のエントリに分割され、各エントリ毎に演算器が設けられる半導体演算処理装置において、エントリ間データ転送を配線レイアウト面積を増大させることなく効率的に行なう。

【解決手段】各エントリ(ERY)に対応するデータ出力部(305)を有する転送配線(300)を設ける。この転送配線(300)において、最遠端の転送部と転送データ出力部(305)の間に、それぞれ所定数のエントリ離れたエントリにデータ転送を行なうデータ送出部(XP1,XP2,XN1,XN2)を設ける。これらの転送配線(300)は、第1方向において整列して、第2方向において1エントリずつずらせて配置することにより、配線レイアウト面積を低減する。演算時にデータ転送を任意のエントリ間で行なうことができる。

(もっと読む)

シングルチップデータ処理装置

【課題】高性能と高機能化を実現したシングルチップデータ処理装置を提供する。

【解決手段】CPUとキャッシュメモリとが接続される第1バスと、DMACと外部バスインターフェイス回路とが接続される第2バスと、上記第1と第2バス接続され、上記第1バス上のアドレス信号を選択的に上記第2バスへ転送するアドレス転送回路を含む第1制御回路とを備える。上記第1制御回路は、上記キャッシュメモリに格納されている情報に対応したアドレス情報のセットが可能にされたアドレスレジスタのアドレス情報と、上記第1と第2バスのアドレス情報とを第1と第2コンパレータでそれぞれ比較する。上記第2コンパレータの一致結果と第1レジスタの設定条件により上記ダイレクトメモリアクセス制御ユニットによる上記第2バスのアドレス情報を用いた書込動作みを検知して上記データ処理ユニットに伝える。

(もっと読む)

1 - 20 / 22

[ Back to top ]