Fターム[5B062JJ08]の内容

マイクロコンピュータ (2,258) | 処理一般、その他 (274) | デバッグ、プログラム開発 (65)

Fターム[5B062JJ08]に分類される特許

1 - 20 / 65

マルチプロセッサ装置及びマルチプロセッサ装置の制御方法

入出力ポート制御装置及びそれを含む集積回路装置

【課題】 各ポートに割り当てられる各機能の特性に応じた割り当てを実現出来る装置を提供する。

【解決手段】 同一の機能を有する複数の1次機能処理部と、それぞれが異なる機能を有する複数の2次機能処理部と、1次機能処理部或いは2次機能処理部の出力データ、或いは前記各処理部に対する入力データが選択的に接続されるポートを備え、前記ポートに出力端子が接続される複数の第1のセレクタ群の一方の入力部には、1次処機能部の各出力処理部接続され、前記複数の第1のセレクタ群の他方の入力部には、2次機能処理部の出力処理部が接続され、前記ポートに入力端子が接続される複数の第2セレクタ群の各入力端子には前記ポートの出力が1対1に接続され、前記第2セレクタ群の各出力が、それぞれ前記2次処理機能部の入力処理部に接続される。

(もっと読む)

マイクロコンピュータ及びマルチマイクロコンピュータシステム

【課題】、一のマイクロコンピュータを介する他のマイクロコンピュータのオンボード書込みを行うためのソフトウェア開発の負担軽減とシステムコストの低減とに寄与する。

【解決手段】外部インタフェースユニットに接続する外部端子を、別の外部インタフェースユニットに接続する外部端子に選択的にスルーさせるとともに、当該外部インタフェースユニットのインタフェース機能を抑止する、バイパス生成部(23)をマイクロコンピュータ(1)に採用する。マルチマイクロコンピュータシステムにそのマイクロコンピュータを第1のマイクロコンピュータとして採用し、第1のマイクロコンピュータにおける一の外部インタフェースユニットに書き込みホスト装置に接続するインタフェースコネクタを結合し、当該第1のマイクロコンピュータにおける他の外部インタフェースユニットを別の第2のマイクロコンピュータに接続する。

(もっと読む)

マイクロコンピュータ

【課題】アプリケーションプログラムの完成前に、システム全体の電源回路の最適化が可能なマイクロコンピュータを提供すること。

【解決手段】本発明に係るマイクロコンピュータ100は、CPU101と、CPU101に接続されたバス107と、バス107に接続される通常動作モードと、バス107と遮断される擬似動作モードと、を備える機能ブロック103A〜103Cと、通常動作モードと前記擬似動作モードとのいずれかを選択するための制御信号を出力する選択回路102と、を備え、機能ブロック103A〜103Cが、擬似動作モードにおいて消費電流を生成する擬似動作回路105A〜105Cと、を備えるものである。

(もっと読む)

マイクロプロセッサ

【課題】セキュリティビットをオンにしてフラッシュROMを書き換え禁止にする手法はフラッシュROMの再書き込みができず、解除キーが入力されたときに書き換えを許可する手法は、解除キー入力の専用端子が必要になり、端子数が増加する。本発明は端子数が増加せず、かつ再書き込みができるマイクロプロセッサを提供することを目的とする。

【解決手段】リセット信号がアクティブになったときに解除キーを入力する端子を入力端子に設定し、この端子に印加されるデータと解除キーを比較し、リセット信号がインアクティブに変化したときにこの比較結果を保存して、この保存した信号でデバッグ部の動作の許可、禁止を制御した。解除キー入力端子をユーザが使用する汎用端子と兼用できる。

(もっと読む)

半導体処理装置

【課題】デバッグツール2から直接に内蔵フラッシュメモリ5の書き換え制御を行うことができ、デバッグの作業効率を高くすることが可能なマイクロコンピュータを得る。

【解決手段】CPU3によって、内蔵フラッシュメモリ5に格納された内蔵フラッシュ情報をJTAGインタフェース11を介してデバッグツール2から読み出し可能にし、デバッグツール2からその内蔵フラッシュ情報に基づいた書き換みデータをJTAGインタフェース11を介して入力して、さらに、CPU3によって、内蔵フラッシュメモリ5に格納された書き換えプログラムに基づいて書き換みデータを内蔵フラッシュメモリ5に書き換える。

(もっと読む)

マイクロコンピュータ

【課題】ユーザーが容易に変更できないように管理されている保護領域へのアクセスを、修理店等において簡易に行うことが可能なマイクロコンピュータを提供すること。

【解決手段】外部とのデータ通信を行う通信手段を備え、エントリーレベルに応じて、前記通信手段を用いた外部から所定の保護領域へのアクセスが制限されているマイクロコンピュータであって、外部から所定のデバッグモード開始信号を入力可能な入力受付手段と、前記入力受付手段に所定のデバッグモード開始信号が入力されたときに、前記所定の保護領域へのアクセス制限を緩和するように制御するデバッグモード制御手段と、を備えるマイクロコンピュータ。

(もっと読む)

マイクロコントローラ及びマイクロコントローラの試験方法

【課題】デバッグ機能等の複雑な機能を搭載することなく、自動的に短時間で異常原因を検出可能なMPUを提供する。

【解決手段】マイクロコントローラは、処理ユニットによるプログラムの実行開始を起点として、レジスタの格納情報が指定する期間が経過すると、処理ユニットにプログラムの実行を停止させるとともに、バッファにバス上の情報を格納させる制御ユニットと、バッファに格納した情報を外部に送信可能であると共に外部からの情報を受信可能である通信ユニットとを含み、処理ユニットは、通信ユニットにより外部から受信した情報とバッファに格納した情報とを比較し、該比較の結果に応じて、レジスタの格納情報を異なる期間を指定する情報に書き換えてプログラムの先頭からの実行を再度開始する動作、或いは、少なくともレジスタの格納情報を外部に出力する動作、の何れかを選択し実行する。

(もっと読む)

マイクロプロセッサ及びマイクロプロセッサのデバッグ方法

【課題】マイクロプロセッサの内部の論理不正動作の調査を容易化できるようにする。

【解決手段】論理動作不正が発生する命令列を、比較命令格納バッファ40に記憶し、プログラムを動作させ、命令比較部41で、実際に実行している命令と比較命令格納バッファ40に記憶されている命令とを比較し、コピー指示のある命令を検出すると、偶数個のコピー命令を生成する。後続のコピーされた偶数個の命令は、前方に存在する命令が完了するまで実行しない命令間隔に設定しており、タイミングや競合による論理動作不正を発生しない。命令列中の最後の命令から1命令ずつコピー指示を前の命令に移動させながらプログラムを実行し、多数決処理チェックの結果を確認することで、論理動作不正の発生する命令を特定する。

(もっと読む)

マイクロコンピュータチップ

【課題】サブチップが接続されない形態で完成状態のECUに搭載される場合には、制御用ソフトの不正書換を防止でき、サブチップが接続された形態で開発段階のECUに搭載される場合には、制御用ソフトの書き換えを効率的に実施可能なマイコンチップの提供。

【解決手段】ECUに搭載されるマイコンの本体チップ1には、ECUの開発段階において、キャリブレーション用チップ2が端子22を介して接続される。そして、本体チップ1は、チップ2が接続されている場合に所定電圧になる端子23を備える。更に本体チップ1では、ECU外部のプログラム書換ツールからの書換要求を受けると、CPU12が、I/Oポート16による端子23の電圧判定レベルからチップ2の接続/非接続を判別し、接続と判別した場合は、ECUの種類に固有の認証用データが上記ツールから送信されてきたか否かを判定する認証処理を行わずに、制御用ソフトの書換処理を行う。

(もっと読む)

マイクロコンピュータの模擬装置

【課題】ターゲットとなるマイクロコンピュータに応じて迅速に対応でき、スピーディなソフトウェア開発が可能となるマイクロコンピュータの模擬装置を提供する。

【解決手段】模擬対象となるCPUにより実行されるアプリケーションソフトウェアを実行する二つのマイクロコンピュータ模擬ブロック10,20と、各マイクロコンピュータ模擬ブロック間で遣り取りするデータを中継する中継処理部42と、一方のマイクロコンピュータ模擬ブロック20が、所定の模擬周期内で処理すべきアプリケーションソフトウェアの一部の実行を、前記中継処理部24を介して他方のマイクロコンピュータ模擬ブロック10に要求し、前記模擬周期内で他方のマイクロコンピュータ模擬ブロック10が実行した結果を前記中継処理部24を介して獲得して、当該所定周期内での処理を完結するマイクロコンピュータの模擬装置。

(もっと読む)

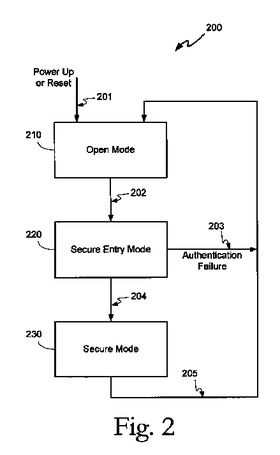

保護された動作モードの間にシステムアクセスを制御するための方法および装置

秘密および/または極秘の情報のためのセキュリティーを提供しながら、ソフトウェア開発のデバッグ能力を提供するマイクロプロセッサに関する。プロセッサは、オープン、セキュアエントリー、およびセキュアモードの内の1つで動作する。オープンモードにおいて、セキュリティー対策は、特定のレジストリビットへのアクセスおよびプライベートメモリ領域へのアクセスを防止する。セキュアコードの実行および/またはプライベートメモリ領域へのアクセス要求があると、セキュアエントリーモードに入る。セキュアコードは、セキュアエントリーモードにおいて認証される。認証は、デジタル署名を利用して実行される。認証が成功すると、セキュアモードに入る。認証コードは、セキュアモード環境において実行される。プライベートメモリ領域は、セキュアモードにおいてアクセス可能である。  (もっと読む)

(もっと読む)

マイクロコンピュータ及び機能評価用チップ

【課題】動作モード設定用の端子を最小限にした上で、より多くの動作モードを設定することができるマイクロコンピュータを提供する。

【解決手段】モードデコーダ8は、MD端子に入力されるモード設定信号レベルの変化回数をカウントするモードカウンタ7の出力データをデコードしてモード信号を出力することで、上記信号レベルの変化回数に応じてマイコン1の動作モードを設定する。そして、モード信号がテストモードを示す場合、アドレスデコーダ4は、CPU2による入力バッファ14へのアクセスが可能となるように切り替え、外部より入力されたシリアルデータがシリアル入出力回路6を介して入力バッファ14に格納される。

(もっと読む)

リセット信号記録監視装置

【課題】ハードウェアによるリセット信号の発生を記録することができると共に、回路構成を大型化させないようにした。

【解決手段】リセット生成回路2へのハードウェアによるリセット要求信号を監視するため、不揮発性メモリ11とメモリ書込み回路12、不揮発性メモリ11に書き込むデータを生成するリアルタイムクロック13を設ける。不揮発性メモリ11は、電源を切ってもデータ保持ができるメモリ素子であり、リアルタイムクロック13が出力する時間データfを書き込みデータとして使用し、マイコン3からは、読み出しデータgとしてデータを読み出すことができる。リアルタイムクロック13は、不揮発性メモリ11に書き込むデータとして時間データfを出力する。メモリ書込み回路12は、マイコン3で動作するソフトウェアにより生成される書き込み開始要求信号dで動作を開始し、一定周期で不揮発性メモリ11に書き込み動作を行なう。

(もっと読む)

模擬マイクロコンピュータ装置

【課題】CPUに暴走等の異常が発生しても、制御対象が安全に作動可能な模擬マイクロコンピュータ装置を提供する。

【解決手段】模擬マイクロコンピュータ装置は、制御対象の動作を制御するためのプログラムである第一のプログラムを実行する第一のCPUと、第一のCPUの周辺リソースとして機能し、前記第一のCPUからの前記制御対象を制御するための信号の出力を制御する第二のプログラムを実行する第二のCPUと、第一のCPUと第二のCPUの異常を監視し、第一のCPUと第二のCPUの少なくとも一方の異常を検出すると、第二のCPUにリセット信号を出力する異常監視部とを備え、前記リセット信号が入力されると、第二のCPUは前記制御対象が安全な動作を行なうように制御するプログラムである第三のプログラムを実行するように構成される。

(もっと読む)

半導体集積回路装置及びその信号処理方法

【課題】情報の秘匿性を確保しつつ開発効率を向上出来る半導体集積回路装置及びその信号処理方法を提供すること。

【解決手段】暗号化データを保持する第1メモリ3と、前記暗号化データの平文を保持する第2メモリ4と、第1動作モードにおいてデバッグ制御回路12から独立し第2動作モードにおいて前記デバッグ制御回路12の支配下に置かれるプロセッサ11と、前記第2動作モードにおいて前記プロセッサ11を制御する前記デバッグ制御回路12と、前記暗号化データの正統性を認証するデータ認証部6と、前記第2動作モードにおいてフラグを保持するレジスタ13と、前記第2メモリ4へのアクセスを制御する第2メモリ制御回路5とを具備し、前記第2メモリ制御回路5は前記レジスタ13に前記フラグが保持されておらず且つ前記データの正統性が認証された場合に前記第2メモリ4へのアクセスを許可する。

(もっと読む)

構成可能なプロセッサを設計するための自動プロセッサ生成システム及び生成方法

【課題】構成可能なプロセッサを設計するための自動プロセッサ生成システム及び生成方法

【解決手段】構成可能なRISCプロセッサは、高性能固定及び可変長符号化を有するユーザ定義の命令を実行する。新しい命令セットを規定する処理は、ユーザが新しい命令を付加し、敏速に評価し、複数の命令セットを保有し、容易に切換えることができるツールによってサポートされる。標準化言語は、ターゲット命令セットの構成可能な定義、命令セットを実行するのに必要なハードウェアのHDL記述、及び検証及びアプリケーション開発のための開発ツールを開発するために使用されるので、設計処理の高度の自動化を可能にする。

(もっと読む)

マイクロコントローラおよびプログラム書き換え方法

【課題】簡単な構造で差分プログラムの転送を行うことが可能なマイクロコントローラ等を提供する。

【解決手段】プログラムを格納するプログラムメモリ15と、プログラムを実行するCPU13とを備えたマイクロコントローラ10において、プログラムメモリ15に格納されたプログラムの差し替え対象部分のアドレスB,Eの範囲を保持するアドレスレジスタ11,12と、アドレスレジスタ11,12に保持された範囲のアドレスを生成し、外部から受け取る差分プログラムを書き込むアドレスとしてプログラムメモリ15に供給するアドレス生成回路14とを備え、外部から差分プログラムを受け取り、差分プログラムをプログラムメモリ15の、アドレス生成回路14によって生成されたアドレスに書き込むことによってプログラムの書き換えを行う。

(もっと読む)

マイクロコンピュータ

【課題】CPUの動作状態をより簡単に確認できるマイクロコンピュータを提供する。

【解決手段】マイクロコンピュータ1のCPU10は、制御プログラムを実行すると、自身に内蔵されているプログラムカウンタ10aのデータを、命令を1ステップ実行するごとにスタックメモリ15に記憶させ、外部機器18よりスタックメモリ15に対するデータ転送要求があると、DMAコントローラ16を起動して入出力回路13へのデータ転送を実行させる。

(もっと読む)

マイクロコンピュータ

【課題】外部ポートを介して行われようとする内部資源の一部に対するアクセスを、効率的に禁止することができるマイクロコンピュータを提供する。

【解決手段】簡易デバッガモニタ10がマイコン1と通信を行い、CPU2に対して外部割込み信号が与えられた場合、アクセスの禁止対象となる内部資源がRAM4であれば、発生した割込み信号を、RAM4に対するアクセスを制御するアクセスブリッジ3に対して与え、外部からのアクセスを禁止する。

(もっと読む)

1 - 20 / 65

[ Back to top ]