Fターム[5B077FF11]の内容

Fターム[5B077FF11]に分類される特許

1 - 20 / 102

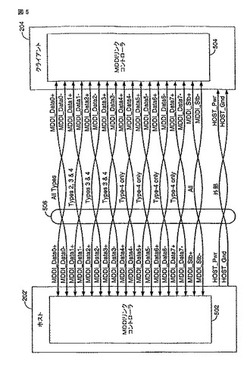

改善されたリンク制御を有する高速データレートインタフェース

【課題】高速データレートインタフェース。

【解決手段】デジタル制御データとデジタルプレゼンテーションデータの事前に選択されたセットを通信するための通信プロトコルを形成するために、共にリンクされるパケット構造を使用して、通信経路上、ホストとクライアントの間でデジタルデータを転送するためのデータインタフェース。前記信号プロトコルは、通信プロトコルを形成するパケットを生成、送信、及び受信し、デジタルデータを1つ又は複数のタイプのデータパケットに形成するように構成され、少なくとも1台が該ホストデバイスに常駐し、該通信経路を通して該クライアントに結合される、リンクコントローラによって使用される。インタフェースは、短距離「シリアル」タイプデータリンクでの、費用効果が高い、低電力の、双方向高速データ転送機構となる。

(もっと読む)

I/Oデバイス共有方法、および装置

【課題】 複数の物理計算機から1つのI/Oデバイスを共有する場合のタグの競合を回避する。

【解決手段】 複数の物理計算機150−1〜150−nと、I/Oデバイス160が、I/Oスイッチ100を経由して接続されたサーバ装置であって、複数の物理計算機が1つのI/Oデバイス160を共有する場合に、1つのI/Oスイッチ100内部で第1の物理計算機150−1からI/Oデバイス160への要求パケットに含まれるタグを、I/Oデバイスで未使用の値に変換した後に、I/Oデバイスに転送し、該要求パケットのI/Oデバイス160から第1の物理計算機150−1への応答パケットに含まれるタグを、元のタグに戻すことにより、複数の物理計算機から1つのI/Oデバイス160を共有する場合のタグの競合の回避を実現する。

(もっと読む)

通信システム及びそのデバイス

【課題】1本の信号線を用いて双方向のシリアル通信を行う通信システム及びそのデバイスを提供することを目的とする。

【解決手段】第1デバイス11と第2デバイス12間を1本の信号線で接続し、互いにレベルの異なる第1レベルと第2レベル、及び前記第1レベルと第2レベルの中間レベルを用いてシリアル通信を行う通信システムであって、第1デバイスは、第1レベルと中間レベルを繰り返すことで第2デバイスにクロックを送信し、第2デバイスは、受信したクロックの中間レベルの期間に第2レベルを出力するか否かで第1デバイスに情報を送信し、第1デバイスは、第2デバイスが情報を送信していない場合に、クロックの中間レベルの期間に第2レベルを出力するか否かで前記第2デバイス12に情報を送信する。

(もっと読む)

クロック同期式シリアル通信装置およびその通信制御方法

【課題】マスターデバイスと複数のスレーブデバイスとがシリアルデータ通信を行う場合に、通信対象とするスレーブデバイスの指定時に生じる通信オーバーヘッドを削減すること。

【解決手段】クロック同期式シリアル通信装置は、クロック信号の周波数を調整するとともに、周波数が調整されたクロック信号およびデータ信号を出力するマスターデバイスと、前記マスターデバイスから出力されたクロック信号およびデータ信号を受信するとともに、受信したクロック信号の周波数を計測する複数のスレーブデバイスとを備え、

前記複数のスレーブデバイスは、それぞれ、識別用の周波数を保持し、計測した周波数と該識別用の周波数とが一致したか否かに応じて、前記マスターデバイスから出力されたデータ信号を保持または破棄する。

(もっと読む)

I2Cバス通信制御システム、及びI2Cバス通信制御方法

【課題】I2Cバスフリーズの原因となったスレーブ装置を速やかに特定する。

【解決手段】プロセッサ100が主プロセッサ、プロセッサ110、1m0が従プロセッサの場合に、主プロセッサがI2C通信を開始し、通信相手を指定するスレーブアドレスを送出したとき、従プロセッサ110、1m0は、I2Cバスに流れているスレーブアドレスを取得しておく。従プロセッサ110、1m0のいずれかに切り替わったときにI2Cバスがフリーズしていた場合、取得済みスレーブアドレスに基づいてバスフリーズ原因のスレーブ装置を特定する。また、特定したスレーブ装置のみに対してリセットをかけることで、I2Cバスフリーズから復帰する。

(もっと読む)

通信制御システム、装置、方法及びプログラム

【課題】デバイスの組合せごとに必要な同期調整を行うことができる通信制御システムを提供する。

【解決手段】ネットワーク上に分散配置されたデバイス間の通信を制御する通信制御システムであって、CPU側ブリッジとIO側ブリッジとがネットワークを介して接続され、CPU側ブリッジは、所属するグループのグループIDと接続されたデバイスのデバイス情報とを通知するCPU側通知手段1を含み、IO側ブリッジは、所属するグループのグループIDと接続されたデバイスのデバイス情報とを通知するIO側通知手段2を含み、通知した情報を収集し、収集した情報に基づいてデバイスの組合せを決定し、決定したデバイスの組合せに応じた同期調整用の設定値を算出する同期設定値算出手段3と、算出した設定値に基づいて、デバイスの組合せにおける同期調整を行う同期調整手段4とを含む。

(もっと読む)

電子機器、電子機器の制御方法、送信装置および受信装置

【課題】HDMI等のデジタルインタフェースにおいて大容量のデータ通信を可能にする。

【解決手段】DDCラインを構成する2本の信号ライン、つまりSDAラインおよびSCLラインを、I2C通信ラインとして用いる他に、高速データ通信ラインとしても用いる。この2本の信号ラインをI2C通信ラインとして用いる場合、ソース機器110、シンク機器120は、I2C通信部を2本の信号ラインに接続した状態となり、I2Cの双方向通信を行う。一方、この2本の信号ラインを高速データ通信ラインとして用いる場合、ソース機器110、シンク機器120は、差動高速ドライバ/レシーバを2本の信号ラインに接続した状態となり、双方向差動通信を行う。双方向差動通信を行う場合、時分割双方向通信を行うことで、全体としての伝送速度は片方向の2倍強必要とされるが、エコーキャンセラを用いた双方向構造よりも安価に実現できる可能性がある。

(もっと読む)

情報処理装置

【課題】ウェイト数が異なる複数の記憶部に対してCPUがアクセスする場合に、無駄なウェイトの発生を抑えつつ、複数の記憶部のいずれに対してもデータを読み出すことができる。

【解決手段】CPU3がRAM29からデータを読み出す場合に、読出部(読出・書込選択回路21、アドレスデコーダ23)はCPU3からの1回目の命令を保持し、CPU3が2回目の命令をした場合に、読出部は保持している1回目の命令に基づいてRAM29のメモリセルからデータを読み出して、RAM用レジスタ27を経由してCPU3へ転送する。従って、CPU3がRAM29からデータを読み出す際に、RAM29のウェイト数より小さいレジスタ25のウェイト数に設定しても、RAM29からデータを読み出すことができる。

(もっと読む)

サンプリング位相を補正するホストコントローラ及び方法

【課題】 転送データの信頼性向上ならびにエラー対処性能の向上を実現する。

【解決手段】 一実施形態は、外部機器から受信した信号をサンプリングする際のサンプリングクロックの位相シフト補正を行うホストコントローラ10であって、前記サンプリングクロックの位相シフトが必要か判定し、位相シフトが必要な場合は、シフト方向に応じてカウンタ108をアップ/ダウンカウントする位相シフト判定部107と、前記位相シフトの変動範囲制限値を格納する制限値格納部109と、前記カウンタ値が前記位相シフトの制限値を超えているか判定し、超えている場合にエラーの通知を可能とし、超えていない場合に、前記カウンタ108のカウンタ値に応じて、前記サンプリングクロックの位相をシフトするシフト制限判定部110とを具備する。

(もっと読む)

マイクロコンピュータ

【課題】バスマスタとバススレーブとの周波数の大小関係に依存せずにバスアクセスを行なうことが可能なマイクロコンピュータを提供すること。

【解決手段】CPU1は、周波数が可変のクロック1で動作する。タイマ3は、クロック2で動作する。周波数変換論理回路11は、メインバスを介してCPU1と接続され、周辺IOバス12を介してタイマ3と接続される。周波数変換論理回路11は、クロック1の周波数がクロック2の周波数よりも高い場合は、周辺IOバス12側のバス制御信号の変化タイミングを示す同期信号1を用いてタイマ3へのバス制御信号を生成し、クロック1の周波数がクロック2の周波数よりも低い場合は、メインバス側のバス制御信号の変化タイミングを示す同期信号2を用いてCPU1へのバス制御信号を生成する。したがって、CPU1とタイマ3との周波数の大小関係に依存せずにバスアクセスを行なうことが可能となる。

(もっと読む)

データ通信装置及びそれを用いたコントローラ

【課題】複数のデバイスを接続したSPIバスを用いたデータ通信システムにおいて、それぞれのデバイスに最適な通信プロトコルを用いてデータ通信を可能にする。

【解決手段】データ通信装置は、マスターデバイスと、複数のスレーブデバイスと、その間を接続し、同期クロック信号に同期してマスターデバイスがスレーブデバイスへデータを送信するデータ送信バス又は同期クロック信号に同期してマスターデバイスがスレーブデバイスからデータを受信するデータ受信バスとの少なくともいずれか一方と、デバイス間を一対一に接続して通信実行を通知するチップセレクト線とを有する。スレーブデバイス毎の物理プロトコルを設定する通信ドライバと、マスターデバイスとスレーブデバイスとの間のシリアル通信を調停する通信マネージャを有する。チップセレクト信号線に対応させ、通信プロトコルを切り替えることで、最適な通信プロトコルを用いて通信することが出来る。

(もっと読む)

通信インタフェース装置及び通信方法

【課題】複雑な制御を要することなく2つの異なるインタフェース回路の一方のインタフェース回路での通信動作中に他方のインタフェース回路での通信動作が行われないようにする。

【解決手段】通信インタフェース装置は、第1の端子201に接続されたチップセレクト端子、第2の端子202に接続されたクロック端子、及び第3の端子203に接続されたデータ端子を有するSPIインタフェース回路101と、第1の端子201に接続されたクロック端子、及び第3の端子203に接続されたデータ端子を有するI2Cインタフェース回路102とを備え、SPIインタフェース回路101で通信する場合は、第1の端子201に固定信号を入力し、第2の端子202にクロック信号を入力し、第3の端子203にデータ信号を入力し、I2Cインタフェース回路102で通信する場合は、第1の端子201にクロック信号を入力し、第3の端子203にデータ信号を入力する。

(もっと読む)

装置インターフェースアーキテクチャおよびプロトコル

【課題】複数の装置間でメッセージを転送するためのインターフェースアーキテクチャおよびプロトコルを提供する。

【解決手段】アーキテクチャは、単一のメッセージフォーマットに従って複数のサービスメッセージを発生し、効率的な多重化プロトコルに従って複数の制御ポイントまたはサービスエンティティ間でサービスメッセージを転送するための能力を提供する。制御ポイントは端末装置上で動作するソフトウエアアプリケーションまたはデバイスドライバーであり得、サービスエンティティはモデムまたは携帯電話のような付属されたデータ通信装置上で動作するネットワークアクセスサービスまたはデバイスマネージメントサービスのような通信サービスであり得る。

(もっと読む)

情報処理装置又は情報処理方法

【課題】情報処理装置と外部装置の夫々が異なる周波数変動範囲を有する周期信号で動作する場合であっても、同期信号(基準クロック)の周波数偏差に起因するホスト間接続の不具合を抑制する方法を提供する。

【解決手段】第1同期信号を生成する生成手段と、前記生成手段の生成した第1同期信号と外部装置から受信する第2同期信号から1つを選択する制御手段と、前記制御手段の選択した同期信号に基づいて前記外部装置と通信する第1通信手段との構成で実現する。

(もっと読む)

データ同期化回路、通信インタフェース回路及び通信装置

【課題】データを同期化させるクロック信号の許容される周波数の範囲を広げる。

【解決手段】実施形態によれば、データ同期化回路SYNC0は、データホールド回路BLC0と、受信タイミング生成回路BLB0と、更新タイミング調整回路BLE0とを備えている。データホールド回路BLC0は、クロック信号CLK_A0に同期したデータDOUT0を受信して、当該データDOUT0がクロック信号CLK_Bに同期化されたデータSYNC_DATA0を出力する。更新タイミング調整回路BLE0は、受信タイミング生成回路BLB0内のDフリップフロップ230_0,230_1及び230_2の値の更新のタイミングを、クロック信号CLK_Bに同期した更新イネーブル信号UE0に基づいて制限する。

(もっと読む)

信号処理システム

【課題】第1の部分と、第1のドライバと補助コントローラとを有する第2の部分と、第1の部分、第1のドライバ及び補助コントローラに接続されたデータバスとを備えた信号処理システムを提供する。

【解決手段】システムの第1のモードにおいて、第1の部分に電源が投入され、第1の部分は第1のプロトコルを使用して第1のドライバと通信し、第1のプロトコルとは異なる第2のプロトコルを使用してデータバスを介して補助コントローラと通信し、第1のドライバは、第1の部分と補助コントローラとの間の通信に第2のプロトコルが使用されるときに第2のプロトコルを無視し、システムの第2のモードにおいて、第1の部分に電源が投入されず、ウェークアップコマンドを取得すると、第1の部分に電源が投入される。

(もっと読む)

I/O拡張回路

【課題】 汎用ロジックICのシフトレジスタを使ってI/Oポートを拡張すると共に、動作速度を向上させることができるI/O拡張回路を提供する。

【解決手段】 ワンチップマイコン1と汎用シフトレジスタIC2との間で連続出力モードを持つクロック同期方式を用いて、ワンチップマイコン1から汎用シフトレジスタIC2にシリアルデータ、同期クロック、ラッチタイミングの信号を送信し、汎用シフトレジスタIC2では、汎用ロジックICをカスケード接続した構成であり、受信した同期クロック、ラッチタイミングの信号に従って、シリアルデータを複数ビットのパラレルデータに変換するI/O拡張回路である。

(もっと読む)

シリアル通信のシステム及び方法

【課題】クロック信号線及びデータ信号線以外に信号線を増やすことなく、シリアル通信の同期を可能とする。

【解決手段】クロック(CLK)信号202及びコマンド(CMD)信号203を供給する装置本体100と、該装置本体にステータス(STS)信号204を供給する外部装置20bとの間で、CLK信号に同期してシリアル通信を行うときに、装置本体で、CMD信号のレベルを変化させて通信の開始を通知し、外部装置では、CMD信号から分岐したCMD割込み信号205のレベルの変化を検出して、通信の開始を判断する。

(もっと読む)

通信装置、通信システムおよび通信方法

【課題】通信装置のクロック信号を停止させた休止状態から復帰するまでの期間を短縮する。

【解決手段】復帰処理を開始する一方の通信装置5は、自身のクロック信号が不安定な状態で、休止状態から復帰させる起動信号を送信する。一方の通信装置5は、自身のクロック信号が安定すると、当該クロック信号に基づくデータ送信が可能になったことを通知する送信可能信号を生成して送信する。他方の通信装置6は、起動信号を受信して自身のクロック信号が安定すると、当該クロック信号に基づくデータ送信が可能になったことを通知する送信可能信号を生成して送信する。複数の通信装置5,6の各々は、自らのクロック信号が安定し、相手の送信可能信号を受信すると、休止状態からの復帰処理を完了する。

(もっと読む)

電子機器

【課題】ICの起動時において、SPI通信による誤動作を防止することが可能な電子機器の提供を目的とする。

【解決手段】マスターICとスレーブICとがSPI通信可能な電子機器であって、マスターICとスレーブICとは、別々の電源供給部により電源の供給を受け、スレーブICは、確認信号を正常に受信した場合に、所定の返り値をマスターICに返信する返り値返信手段を有し、マスターICは、スレーブICに対して確認信号を送信する確認信号送信手段と、確認信号によりスレーブICから返信される返り値を判断し、返り値が所定の値になるまで確認信号送信手段に確認信号の送信を繰返させる返り値判断手段と、返り値が所定の値となった場合に、スレーブICとの通信を許可する許可手段と、を有する。

(もっと読む)

1 - 20 / 102

[ Back to top ]