Fターム[5B125BA04]の内容

リードオンリーメモリ (43,397) | メモリ種別 (5,638) | EEPROM、フラッシュ (3,956) | 複数のFGを有する (27)

Fターム[5B125BA04]に分類される特許

1 - 20 / 27

半導体装置

【課題】メモリセルの動作を従来よりも高速化できる半導体装置を提供する。

【解決手段】フローティングゲートFGとコントロールゲートCG、第1導電型ソース13s及び第1導電型ドレイン13dを有する第1導電型MOSトランジスタ13と、前記フローティングゲートFGと前記コントロールゲートCG、第2導電型ソース14s及び第2導電型ドレイン14dを有する第2導電型MOSトランジスタ14と、前記第1導電型ドレイン13d及び前記第2導電型ドレイン14dに接続される第1のソース/ドレイン11bと、第2のソース/ドレイン11aと、ゲートを有する選択トランジスタ11と、前記第1導電型ソースに接続される第1電源線VpLと、前記第2導電型ソースに接続される第2電源線VnLと、前記選択トランジスタ11の第2のソース/ドレイン11aに接続されるビット線BLと、前記選択トランジスタ11のゲートに接続されるワード線WLと、を有する。

(もっと読む)

メモリ回路

【課題】電源投入時における誤書き込みが発生しにくいメモリ回路を提供する。

【解決手段】メモリ回路10は、書き込み時のみにソース・ドレイン間に電圧を印加されて書き込まれる、書き込み用のPチャネル型不揮発性メモリ素子15と、コントロールゲート及びフローティングゲートがPチャネル型不揮発性メモリ素子15のコントロールゲート及びフローティングゲートとそれぞれ共通にされ、読み出し時のみにソース・ドレイン間に電圧を印加されて読み出される、読み出し用のNチャネル型不揮発性メモリ素子16と、を備える。

(もっと読む)

記憶装置、半導体装置

【課題】データの書き込み不良を抑えつつ、面積を小さく抑えることができる不揮発性の記憶装置、または当該不揮発性の記憶装置を用いた半導体装置の提供を目的の一とする。

【解決手段】不揮発性の記憶素子を有する第1の記憶部と、上記第1の記憶部へのデータの書き込みが正確に行われたかどうかを検証するベリファイ動作において、上記データを一時的に保存するための第2の記憶部(データバッファ)とを有する。そして、第2の記憶部が、記憶素子と、当該記憶素子における電荷の保持を制御するための、オフ電流またはリーク電流が極めて小さい絶縁ゲート電界効果型トランジスタとを有する。

(もっと読む)

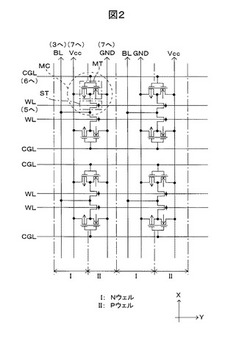

PMOS・NMOS・PMOS・NMOS構造を備えた4トランジスタ不揮発性メモリセル

不揮発性半導体メモリセル及び不揮発性半導体メモリ装置

【課題】従来に比べ信頼性を向上させることができる不揮発性半導体メモリセル及び不揮発性半導体メモリ装置を提供する。

【解決手段】本発明の不揮発性半導体メモリセルは、半導体基板上に形成される複数のMOSトランジスタからなり、当該メモリセルを選択するためのセレクトゲートと、記憶内容を制御するためのコントロールゲートとを有する不揮発性半導体メモリセルであって、 互いに並列接続されるとともに、独立の複数のコントロールゲートでそれぞれ制御される複数のフローティングゲート型トランジスタと、複数のフローティングゲート型トランジスタと直列に接続され、セレクトゲートに接続される選択トランジスタとを有し、複数のフローティングゲート型トランジスタと選択トランジスタとが半導体基板上で直線状に配列されたものであって、複数のフローティングゲート型トランジスタの各ドレインが直線状のメタル配線で接続されたものである

(もっと読む)

不揮発性半導体メモリセル及び不揮発性半導体メモリ装置

【課題】レイアウト面積の増大を抑えつつ信頼性を向上させることができる1層ポリシリコンプロセスで製造可能な不揮発性半導体メモリセルを提供する。

【解決手段】共通のコントロールゲートCGで制御されるとともに、互いに並列接続された複数のフローティングゲート型トランジスタT2、T3を有し、複数のフローティングゲート型トランジスタT2、T3と選択トランジスタT1とが半導体基板上で直線状に配列されたものであって、複数のフローティングゲート型トランジスタT2、T3の各ドレインが直線状のメタル配線22で接続される。

(もっと読む)

不揮発性半導体メモリセル及び不揮発性半導体メモリ装置

【課題】レイアウト面積を削減し、且つ、記憶保持の信頼性を向上する不揮発性半導体メモリ装置を提供する。

【解決手段】不揮発性半導体メモリセルは、第1の選択トランジスタ、2つのフローティングゲート型のメモリ素子及び第2の選択トランジスタの順に直列に接続し、レイアウトとしては、トランジスタ形成部220にそれぞれの素子のドレイン及びソースを直列に配置し、メモリ素子のコントロールゲート電極であるn+型拡散層219をトランジスタ形成部と平行に配置し、メモリ素子のフローティングゲートであるポリシリコン203a、203bをトランジスタ形成部220とn+型拡散層219とに垂直に交わる方向に配置し、第1の選択トランジスタ及び第2の選択トランジスタのゲート電極であるポリシリコン214a、214bをトランジスタ形成部220と垂直に交わる方向に配置する。

(もっと読む)

ツインMONOSメモリアレイ構造

【課題】選択されるメモリの制御ゲートに隣接するワードゲートへの負電圧の印加によってメモリの制御ゲート下の接合端部で生成される高エネルギーのホールの分布を変化させることによって、ツインMONOSセルの消去速度を向上させる。

【解決手段】Vword=0のとき、消去目標電圧Vtは1秒後に0.5Vに到達する。ワードゲートをVword=−0.5Vという僅かにマイナスの電位にバイアスすると、消去速度がほぼ1000倍に高められる。これは、右側の拡散領域42の接合端部でバンド間トンネル効果により発生するホールが負の電位によってワードゲートの方に引き寄せられ、目標制御ゲート62の下に更に蓄積されるからである。更に、−1Vの負電圧をワードゲートに印加することによって、消去速度は1000倍以上に高められる。

(もっと読む)

半導体記憶装置及びデータ転送方法

【課題】 不揮発性メモリ部から揮発性ラッチ回路へのデータ転送動作が不揮発性メモリ部の動作を制御する制御端子の電圧が高い領域でも正常に動作可能な半導体記憶装置を提供する。

【解決手段】 制御回路CNTが、ワード線WL1、Wl2に読み出し電圧Vwlを印加し、第1スイッチング素子Qn2、Qn3及び第2スイッチング素子Qn4を導通状態にした後、プリチャージ回路Qp1、Qp2によりデータノードSD、SDBをプリチャージした後、不揮発性メモリ部M1、M2の各電流量でデータノードを放電する第1プリセンス動作を行い、その後にワード線電圧を部分的或いは徐々に低下させ、揮発性ラッチ回路LCを活性化させて、データノード間の電圧差を予備的に増幅する第2プリセンス動作を行い、その後に、第1スイッチング素子をオフするか、ワード線への電圧印加を完全に停止するか何れか一方または両方の動作を行ってメインセンス動作を開始する。

(もっと読む)

メモリセル、電子システム、メモリセルの形成方法、およびメモリセルのプログラミング方法

いくつかの実施形態は、誘電体材料によって互いにスペーシングされる、垂直に積層される電荷捕獲領域を有するメモリセルを含む。誘電体材料は、高k材料を含み得る。電荷捕獲領域のうちの1つ以上は、金属材料を含み得る。かかる金属材料は、ナノドット等の複数の個別の絶縁されたアイランドとして存在し得る。いくつかの実施形態は、メモリセルの形成方法を含み、トンネル誘電体上に2つの電荷捕獲領域が形成され、当該領域は互いに対して垂直に配置され、トンネル誘電体に最も近い領域は、もう1つの当該領域よりも深いトラップを有する。いくつかの実施形態は、メモリセルを含む電子システムを含む。いくつかの実施形態は、垂直に積層される電荷捕獲領域を有するメモリセルのプログラミング方法を含む。  (もっと読む)

(もっと読む)

不揮発性半導体記憶素子及び不揮発性半導体記憶装置

【課題】ベリファイ操作が省略可能で2種類を超えるしきい値電圧の実現が可能な不揮発性半導体記憶素子及び不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板1と、半導体基板に設けられた第一の導電型の半導体領域2cと、離間して設けられた第二の導電型のソースおよびドレイン領域2a、2bと、ソースおよびドレイン領域の間に設けられた第一の絶縁層3と、第一の絶縁層上に設けられ、少なくとも三層の導電体膜4a、4c、4e、4gと、導電体膜間に設けられた導電体間絶縁膜4b、4d、4fとの積層構造を有し、半導体基板から遠く離れて位置している導電体間絶縁膜の誘電率は、半導体基板の近くに位置している導電体間絶縁膜の誘電率よりも高く且つ導電体間絶縁膜の誘電率は第一の絶縁層3の誘電率より低い電荷蓄積層4と、電荷蓄積層上に設けられ導電体間絶縁膜の何れよりも誘電率が高い第二の絶縁層5と、導電体層6と、を備えている。

(もっと読む)

不揮発性半導体記憶装置及びその動作方法

【課題】読み出しに使用される回路の規模を小さくし、更に、リファレンス信号の信号レベルを容易に微調整する。

【解決手段】フローティングゲートに電荷を蓄積するメモリセル21と、メモリセル21のドレイン側に接続されるビット線BLiと、ソース側に接続されるビット線/BLiと、フローティングゲートに電荷を蓄積するリファレンスセル22と、ビット線BLi、/BLiから電気的に独立して設けられた、リファレンスセル22のドレイン側に接続されるリファレンスビット線RBLと、ソース側に接続されるリファレンスビット線/RBLと、センスアンプ6と、ビット線電位制御回路7とを備える。ビット線電位制御回路7は、メモリセル21からデータを読み出す読み出し動作時に、リファレンスビット線/RBLをビット線/BLiの電圧レベルと異なる電圧レベルに制御する。

(もっと読む)

メモリ回路及びメモリ回路の動作制御方法

【課題】メモリセルを構成するPチャネル1層ポリシリコンを使用した1対のメモリトランジスタの両方に常時電流を流すことなく、メモリセルに書き込まれたデータの読み出しを行うことができるメモリ回路及びメモリ回路の動作制御方法を得る。

【解決手段】電源電圧VDDと、PMOSトランジスタ13及びメモリトランジスタ11の接続部との間にNMOSトランジスタ15を接続し、電源電圧VDDと、PMOSトランジスタ14及びメモリトランジスタ12の接続部との間にNMOSトランジスタ16を接続し、NMOSトランジスタ15及び16の各ゲートにリードイネーブル信号をそれぞれ入力するようにした。

(もっと読む)

NAND型不揮発性メモリのデータ消去方法

【課題】NAND型不揮発性メモリの消去動作として、PウェルやNウェルなどの基板端子を用いないで、不揮発性メモリ素子における電荷蓄積部に注入された電荷を放出する、すなわちNAND型不揮発性メモリのデータの消去動作する方法を提供することを課題とする。

【解決手段】NAND型不揮発性メモリにおけるデータの消去方法において、不揮発性メモリ素子における電荷蓄積層に格納された電荷の放出について、ビット線、ソース線、及び制御ゲートに電位を印加することにより行う。そして、不揮発性メモリ素子における電荷蓄積層に格納された電荷の放出を、電荷を放出する不揮発性メモリ素子のソース端子、ドレイン端子、及び制御ゲートに電位を印加することにより行う。

(もっと読む)

半導体記憶装置及びその読出方法、並びに電子機器

【課題】不揮発性メモリアレイにおいて信頼性の高い読み出し動作を行う。

【解決手段】各メモリセルは、互いに逆向きの第1及び第2の電流経路を使って読み出されるべき一対の記憶部を有する。各メモリセルを流れる電流は、各電流経路でそれぞれ、メモリセルの記憶状態「00」「01」「10」「11」に応じて図中に示す分布93〜96を示す。分布93と分布95との間に第1のリファレンス電流レベル91を定め、分布94と分布96との間に第2のリファレンス電流レベル92を定める。第1、第2の電流経路で、メモリセルに流れる電流とリファレンス電流レベル91,92とを比較するとともに、メモリセルに流れる電流に応じた電荷をそれぞれ第1、第2の蓄積部に蓄える。第1の蓄積部に蓄えた電荷量と第2の蓄積部に蓄えた電荷量とを比較する。

(もっと読む)

半導体装置とその駆動方法

【課題】 従来のEEPROMにおいては、データの書き込みや消去の際にデータリード用トランジスタを用いている為、ホットキャリア注入やFNトンネル電流がデータリード用トランジスタ部のゲート酸化膜に大きなストレスを与えてしまい、そのデータ保持信頼性に大きな悪影響を与える。

【課題を解決するための手段】 本発明は、データの書き込み及び消去をデータリード用トランジスタでは一切行わないことでセルのデータ保持信頼性向上を図る。更に、データリード時にゲート酸化膜に電界をかけないようにすることでセルのデータ保持信頼性向上を図る。

(もっと読む)

半導体記憶装置および電子機器

【課題】 セル電流値のデータ0とデータ1の分布の隙間が極端に狭かったり、あるいは、重なってしまうようなことがあっても、メモリセルの情報を高精度に判別することができる半導体記憶装置を提供すること。

【解決手段】 第1入出力端子から第2入出力端子に電流を流したときのメモリセルからの出力電流に相当する第1出力と、第2入出力端子から第1入出力端子に電流を流したときのメモリセルからの出力電流に相当する第2出力とに基づいて、メモリセルMC0,MC1,MC2,MC3・・が有する二つの記憶領域のうちの片側の記憶領域の情報の読み出しを行う。

(もっと読む)

不揮発性半導体記憶装置

【課題】 浮遊ゲート周辺の寄生容量を削減するとともに、制御ゲートと浮遊ゲート間の容量を増大することが困難であり、書き込み電圧を低減し、高集積化、高速化を図ることが困難であった。

【解決手段】 半導体基板11に溝が形成されている。溝の底部に第1のゲート絶縁膜GIを介して浮遊ゲートFGが形成されている。浮遊ゲートFGの両側に対応する半導体基板11内にソース又はドレイン領域としての拡散層S/Dが形成されている。両拡散層S/D上に位置し、浮遊ゲートFGの両側壁にゲート間絶縁膜IGIを介して浮遊ゲートFGを駆動する第1、第2の制御ゲートCGが形成されている。

(もっと読む)

不揮発性記憶素子の制御方法

【課題】 ソース・ドレインに挟まれた1つのメモリセルに4ビット以上のメモリ領域を有する不揮発性記憶素子へのデータ書込を精度よく行う。

【解決手段】 不揮発性記憶素子100は、シリコン基板102に離間して設けられた第1および第2の不純物拡散領域160aおよび160bの間に並行配置されたn個(nは4以上の偶数)のコントロールゲート114〜117、およびそれらのコントロールゲートとそれぞれ対を成すメモリ領域106a〜106dを含むメモリセルを含む。不揮発性記憶素子100の制御方法は、n個のコントロールゲート114〜117を左右2分割し、電子注入対象のメモリ領域から遠い方の不純物拡散領域に低電圧、近い方の不純物拡散領域に高電圧を印加するとともに、電子注入対象のメモリ領域と対を成すコントロールゲートに他のコントロールゲートよりも高電圧を印加する工程を含む。

(もっと読む)

不揮発性メモリとその製造方法

【課題】 低消費電力での高速書き込みが可能で、かつ構造の簡単な不揮発性のメモリセルとその製造方法を提供する。

【解決手段】 素子分離領域2で分離された横方向の素子形成領域にソース拡散層4とドレイン拡散層5を交互に形成し、このソース拡散層4の両側にゲートONO膜6L,6Rを介して制御ゲート電極7L,7Rを形成する。制御ゲート電極7L,7Rの側面には、ゲート電極間絶縁膜8L,8Rを介してゲート電極10L,10Rを形成し、制御ゲート電極7L,7R、及びゲート電極10L,10Rは、素子分離領域2上のソースラインSL及びワードラインWLL,WLRで、それぞれ縦方向に接続する。更に、メモリセルが形成されたシリコン基板1の表面に中間絶縁膜11を形成し、横方向の各ドレイン拡散層5はコンタクト12を介してビットラインBLに接続する。

(もっと読む)

1 - 20 / 27

[ Back to top ]