Fターム[5B125EA00]の内容

リードオンリーメモリ (43,397) | セル配置、アレイ構成 (3,643)

Fターム[5B125EA00]の下位に属するFターム

Fターム[5B125EA00]に分類される特許

1 - 8 / 8

デュアル機能を有する不揮発性半導体メモリセル

【課題】デュアル機能を有する不揮発性半導体メモリセルは、基板、第1ゲート、第2ゲート、第3ゲート、電荷蓄積層、第1拡散領域、第2拡散領域及び第3拡散領域を有する。

【解決手段】第2ゲート及び第3ゲートは、デュアル機能のワンタイムプログラミング機能に対応する第1電圧及びデュアル機能のマルチタイムプログラミング機能に対応する第2電圧を受けるために用いられる。第1拡散領域は、ワンタイムプログラミング機能に対応する第3電圧及びマルチタイムプログラミング機能に対応する第4電圧を受けるために用いられる。第2拡散領域は、マルチタイムプログラミング機能に対応する第5電圧を受けるために用いられる。

(もっと読む)

半導体記憶装置

【課題】電源電圧の供給の停止及び再開を行う構成において、揮発性の記憶装置と不揮発性の記憶装置との間のデータの退避及び復帰の必要のない半導体記憶装置を提供する。

【解決手段】不揮発性の半導体記憶装置とする際、揮発性の記憶装置と不揮発性の記憶装置を分離することなく構成する。具体的に半導体記憶装置には、酸化物半導体を半導体層に有するトランジスタ及び容量素子に接続されたデータ保持部にデータを保持する構成とする。そしてデータ保持部に保持される電位は、電荷をリークすることなくデータの出力が可能なデータ電位保持回路及び電荷をリークすることなくデータ保持部に保持した電位を容量素子を介した容量結合により制御可能なデータ電位制御回路で制御される。

(もっと読む)

不揮発性記憶装置、集積回路装置及び電子機器

【課題】第1、第2のモードを任意に切り替え可能にする不揮発性記憶装置等の提供。

【解決手段】第1、第2のメモリーセルMC1、MC2は第1のモードでは別個のデータを記憶し、第2のモードでは相補データを記憶する。読み出し回路RCは第1のモードでは、差動信号増幅部CM1から第1のメモリーセルMC1に流れる検出電流と第2のリファレンス電流源IS2に流れるリファレンス電流を比較して第1のメモリーセルMC1の記憶データを読み出し、差動信号増幅部CM1から第2のメモリーセルMD1に流れる検出電流と第1のリファレンス電流源IS1に流れるリファレンス電流を比較して第2のメモリーセルMD1の記憶データを読み出す。第2のモードでは、差動信号増幅部CM1から第1のメモリーセルMC1に流れる検出電流と第2のメモリーセルMD1に流れる検出電流を比較することで第1、第2のメモリーセルMC1、MD1の相補データを読み出す。

(もっと読む)

不揮発性のラッチ回路及び論理回路及びそれを用いた半導体装置

【課題】新規な不揮発性のラッチ回路及びそれを用いた半導体装置を提供する。

【解決手段】第1の素子の出力は第2の素子の入力に電気的に接続され、第2の素子の出力は第2のトランジスタを介して第1の素子の入力に電気的に接続されるループ構造を有するラッチ回路であって、チャネル形成領域を構成する半導体材料として酸化物半導体を用いたトランジスタをスイッチング素子として用い、またこのトランジスタのソース電極又はドレイン電極に電気的に接続された容量を有することで、ラッチ回路のデータを保持することができる。これにより不揮発性のラッチ回路を構成することができる。

(もっと読む)

半導体装置

【課題】無線チップのような、CPUとメモリを含む半導体装置の低消費電力化を図る。

【解決手段】メモリ回路は、複数のワード配線、複数のビット配線、および複数のメモリセルを有する。複数のメモリセルの構造はメモリセルに記憶されるデータ(”ハイ”か”ロー”)によって決定される。メモリ回路に記憶するプログラムなどのデータ配列を予め解析する。データが”ハイ”を多く含む場合、”ハイ”を記憶するメモリセルを、半導体素子を形成しない空セルで形成する。

(もっと読む)

プログラマブルセル

OTPメモリ(100)を有する装置が開示される。OTP装置(100)のプログラム状態が第1のノード(120)とラッチ(102)の間に直列に接続されたヒューズ(106)に記憶される。プログラムモード中に、第1のノード(120)はプログラム電圧に電気的に接続される。読取りモード中に、第1のノード(120)はグランドに電気的に接続され、それによって、第1の分圧電圧がラッチの第1のノードにおいて生成される。  (もっと読む)

(もっと読む)

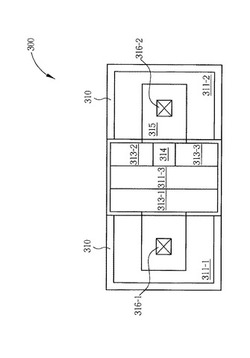

不揮発性半導体メモリ

不揮発性のメモリセルトランジスタは、ドレインからソースのみに電流が流れ、かつソース側のみで電荷を交換する指向性を有している。ワード線に接続される一対のメモリセルトランジスタのソースとドレインおよびドレインとソースとがそれぞれ接続されている。データの書き換え動作中に、一対のメモリセルトランジスタのソースおよびドレインには、逆の電圧が印加される。メモリセルトランジスタの指向性により、電荷蓄積層に対する電荷交換は、ソース領域のみで行われる。したがって、一方のメモリセルトランジスタのデータのみを書き換えできる。この結果、メモリセルサイズを増加させることなく、メモリセル毎にデータを書き換えできる。  (もっと読む)

(もっと読む)

フラッシュメモリ素子及びその動作方法

【課題】2ビットより多くのマルチビット動作を具現できるメモリセル構造を有するマルチビットフラッシュメモリ素子を提供する。

【解決手段】基板上にメサ状に形成された第1活性層110と、第1活性層100上に形成され、第1活性層100と反対の性質の導電型の第2活性層130と、第1、第2活性層110、130とを電気的に隔離するための活性層間分離層210と、スタックの互いに対向する二側面にそれぞれ形成されたソース及びドレイン550と、この側面と異なる、互いに対向する二側面にそれぞれ形成された第1、第2ゲート410、430と、トンネル誘電層230と、トンネル誘電層230と第1、第2ゲート410、430との間に形成され、トンネル誘電層230をトンネリングした電荷を保存する電荷捕獲層300と、を備える。

(もっと読む)

1 - 8 / 8

[ Back to top ]