Fターム[5B125EA01]の内容

リードオンリーメモリ (43,397) | セル配置、アレイ構成 (3,643) | NOR型 (639)

Fターム[5B125EA01]に分類される特許

1 - 20 / 639

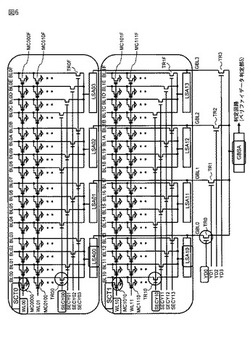

不揮発性半導体記憶装置およびそのベリファイ制御方法

【課題】ベリファイに要する時間の短縮を図る。

【解決手段】ワード線WLとローカルビット線BLに接続された電気的に書き換え可能な複数のメモリセルMCを含むメモリセルアレイと、前記ローカルビット線に接続され前記各メモリセルのデータを反転してグローバルビット線GBLに出力する複数のローカルセンスアンプLSAと、前記複数のローカルセンスアンプの出力の論理和を演算するグローバルセンスアンプGBSAと、前記複数のローカルセンスアンプを動作させて該複数のローカルセンスアンプに接続された複数のメモリセルのデータを同時にベリファイする第1ベリファイと,前記複数のローカルセンスアンプを停止させて,該各ローカルセンスアンプに接続された前記ローカルビット線と前記グローバルビット線を直結して該複数のローカルセンスアンプに接続された複数のメモリセルのデータを同時にベリファイする第2ベリファイとを切り替えるアドレスデコーダと、を有する。

(もっと読む)

不揮発性半導体メモリ素子、および不揮発性半導体メモリ装置

【課題】フローティングゲートへの電荷の蓄積と消去を容易に行え、またフローティングゲートの電荷を消去する場合にメモリセルの閾値を容易に制御できる、不揮発性半導体メモリ素子を提供する。

【解決手段】フローティングゲートへの電荷の蓄積時に、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットエレクトロンを半導体基板中に発生させ、フローティングゲートに電荷を注入する。また、フローティングゲートの電荷の消去時には、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットホールを発生させ、該ホットホールにより蓄積された電荷を消去する。また、フローティングゲートの電荷の消去時には、メモリセルのコントロールゲートとソース間の閾値が所望の値になるように制御しながら、電荷を消去する。

(もっと読む)

半導体記憶素子及び半導体記憶装置

【課題】LSI素子の性能劣化及びヒューズ素子の欠陥の増加を抑制できる半導体記憶素子及び半導体記憶装置を提供する。

【解決手段】半導体記憶素子100は、第1ヒューズ線111と、第1ヒューズ線111と並列接続された第2ヒューズ線112とを有し、切断されているか否かによって2値のデータを保持するヒューズ素子110と、一端がワード線130に接続されており、ヒューズ素子110に電流を流すか否かを選択する選択素子120と、を備える。

(もっと読む)

メモリのプログラミング方法及びメモリアレイ

【課題】クリティカル・ディメンションの変動に鈍感であり且つ高速なメモリプログラミング方法等を提供する。

【解決手段】メモリの複数のメモリセルの夫々は、ウェルと、ソース及びドレイン領域と、記憶レイヤと、ゲートとを有する。メモリセルはマトリクス状である。同じ列ドレイン領域は同じビットラインへ接続し、同じ行ゲートは同じワードラインへ接続し、同じ列ソース領域は同じソースラインへ接続する。メモリは、いずれかのメモリセルへ電気的に接続されたワードラインへ第1の電圧を印加し、そのメモリセルへ電気的に接続されたビットラインへ少なくともプログラミング閾値だけ第1の電圧と異なる第2の電圧を印加し、そのメモリセルへ電気的に接続されたソースラインへ少なくともプログラミング閾値だけ第1の電圧と異なる第3の電圧を印加し、複数のメモリセルへ基板電圧を印加することによって、プログラミングされる。

(もっと読む)

半導体メモリ

【課題】読み出しデータの精度を高めることが可能な半導体メモリを提供する。

【解決手段】メモリセルから第1ビット線BL0〜BLm及び第2ビット線BLV0〜BLVmを介して読み出された読出信号同士の差分に基づき読出データの値を判定するにあたり、上記第1及び第2ビット線に共に電流が流れている場合にはメモリセルがデータ消去状態にあると判断し、上記判定したデータの値に拘わらず固定のデータ値を読出データとして出力する。

(もっと読む)

半導体記憶装置及びデータ読み出し方法

【課題】レイアウト面積の増大を抑制することができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置1は、2つのメモリセルアレイ10U,10Dと、それら2つのメモリセルアレイ10U,10Dで共有されるセンスアンプ30と、メモリセルアレイ10U,10Dからのデータ読み出しを制御する制御回路50とを有している。メモリセルアレイ10Uは、m本のワード線WL0U〜WLmUと、n本のビット線BL0U〜BL15Uと、これらワード線WL0U〜WLmUとビット線BL0U〜BL15Uの交差点に設けられたメモリセルMCと、ビット線BL0U〜BL15Uとダミーワード線DWLUとの交差点に設けられたダミーセルDMCとを有している。制御回路50は、一方のメモリセルアレイからデータを読み出す場合に、他方のメモリセルアレイのダミーワード線を活性化してダミーセルによりセンスアンプ30のリファレンスレベルを生成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】選択メモリセルトランジスタに電荷を蓄積する際の電圧を従来よりも自由に設定し得る不揮発性半導体記憶装置を提案する。

【解決手段】不揮発性半導体記憶装置1では、選択メモリセルトランジスタ115に電荷を蓄積させる際、電圧の高い書き込み禁止電圧をP型MOSトランジスタ9bから印加し、電圧の低い書き込み電圧をN型MOSトランジスタ15aから印加して、選択メモリセルトランジスタ115又は非選択メモリセルトランジスタ116へ電圧を印加する役割分担を、P型MOSトランジスタ9b及びN型MOSトランジスタ15aに分けたことで、P型MOSトランジスタ9b及びN型MOSトランジスタ15aそれぞれのゲート電圧やソース電圧を個別に調整でき、最終的にゲート基板間電圧を例えば4[V]等に設定し得る。

(もっと読む)

OTPメモリ

【課題】より秘匿性の高いOTPメモリを提供する。

【解決手段】メモリセルは、第1ノードと第2ノードとの間に電流経路を形成するメモリトランジスタと、第3ノードと第4ノードとの間に電流経路を形成し、第3ノードがメモリトランジスタのゲートと配線により接続された選択トランジスタと、第1ノードに接続されたキャパシタとを備える。メモリトランジスタに対して、ゲート酸化膜が破壊されず劣化してゲートリーク電流が増大する程度の高電圧を印加することによりデータが書き込まれる。キャパシタの蓄積電荷のリークの有無によりデータを読み出すことが可能となる。ゲート酸化膜の劣化箇所は物理解析で識別できないため、秘匿性が高い。

(もっと読む)

半導体記憶装置、及び半導体記憶装置の動作方法

【課題】光学的に書き込み状態が解析されることがなく、安価に実現することのできる、半導体記憶装置及びその動作方法を提供すること。

【解決手段】半導体記憶装置は、書込み処理が行われていない第1半導体記憶素子と、書込み処理が行われた第2半導体記憶素子とを具備する。前記第1半導体記憶素子及び前記第2半導体記憶素子は、それぞれ、不純物が注入された半導体層を備える抵抗部と、前記抵抗部に接続される、第1コンタクトと、前記抵抗部に接続される、第2コンタクトとを具備する。前記第1半導体記憶素子における前記半導体層の不純物の活性化率は、前記第2半導体記憶素子のそれとは異なっている。

(もっと読む)

半導体装置

【課題】電荷捕獲型の場合であっても高速にプログラムすることが可能な不揮発性メモリを備えた半導体装置を提供する。

【解決手段】半導体装置において、メモリアレイは、行列状に配列され、各々が閾値電圧のレベル変化によってデータを記憶する複数のメモリセルMC0,MC1を含む。ベリファイ回路50は、プログラム対象のメモリセルに対して複数回実行されるプログラム動作ごとに、閾値電圧がプログラムベリファイ電圧に到達したか否かを判定する。電流調整回路52は、プログラム対象の複数のメモリセルのうち、ベリファイ回路50によって閾値電圧がプログラムベリファイ電圧に達していないと判定されたメモリセルには第1の電流値のプログラム電流を流し、閾値電圧がプログラムベリファイ電圧に達したと判定されたメモリセルには第1の電流値よりも小さい第2の電流値のプログラム電流を流す。

(もっと読む)

不揮発性半導体記憶装置

【課題】高速で動作し得る不揮発性半導体記憶装置を提供する。

【解決手段】選択トランジスタとメモリセルトランジスタMTとを有するメモリセルMCがマトリクス状に配列されて成るメモリセルアレイ10と、ビット線BLの電位を制御する列デコーダ12と、第1のワード線WL1の電位を制御する電圧印加回路14と、第2のワード線WL2の電位を制御する第1の行デコーダ16と、ソース線SLの電位を制御する第2の行デコーダ18とを有し、列デコーダは電圧印加回路及び第2の行デコーダより耐圧の低い回路により構成されており、第1の行デコーダは電圧印加回路及び第2の行デコーダより耐圧の低い回路により構成されている。ビット線と第2のワード線とが高速で制御され得るため、メモリセルトランジスタに書き込まれた情報を高速で読み出すことができる。

(もっと読む)

不揮発性半導体記憶装置

【課題】電源電圧の供給停止を検出せずに、かつメモリセルからデータを読み出すことなく、書き換え動作中の電源遮断が容易に検出できる不揮発性半導体記憶装置を提供する。

【解決手段】行列上にフラッシュメモリセルが配置されたメモリアレイ99は、メモリブロック8_0〜8_3に分割される。メモリブロック8_0〜8_3は、データを記憶するノーマルメモリセルNCと、消去動作の完了の有無表わすためのフラグメモリセルFCを含む。制御回路6は、メモリブロックの消去動作が終了後に、フラグメモリセルFCを書込状態に設定する。

(もっと読む)

フラッシュメモリ装置

【課題】低操作電圧および低電力消費量のフラッシュメモリを提供する。

【解決手段】フラッシュメモリ装置は、複数のメモリセルと、複数のプログラミング制御電圧生成器とを含む。各メモリセルは、制御エンドポイントを介してプログラミング制御電圧を受信し、プログラミング制御電圧に基づいてデータプログラミング操作を実行する。各プログラミング制御電圧生成器は、プリチャージ電圧送信機と、ポンピングキャパシタとを含む。プリチャージ電圧送信機は、第1期間中に、プリチャージイネーブル信号に基づいて、対応するメモリセルの制御エンドポイントにプリチャージ電圧を提供する。ポンプ電圧は、第2期間中にポンピングキャパシタに提供され、各メモリセルの制御エンドポイントでプログラミング制御電圧を生成する。

(もっと読む)

半導体装置

【課題】テスト時間の短縮化を図ることが可能な半導体装置を提供する。

【解決手段】このチャージポンプ回路12では、通常動作時は、ポンプキャパシタC0,C2の一方電極にポンプクロック信号φPを与えるとともにポンプキャパシタC1,C3の一方電極にポンプクロック信号φPの相補信号を与え、ポンプキャパシタC0〜C3の欠陥を検出するテストモード時は、ポンプキャパシタC0〜C3の各々の電極間に外部電源電圧VCCを静的に印加する。したがって、MOSトランジスタのオン耐圧を超える高電圧をポンプキャパシタC0〜C3に印加できるので、テスト時間を短縮化できる。

(もっと読む)

半導体記憶装置

【課題】データの読み出し速度を向上する。

【解決手段】半導体記憶装置1は、メモリセルアレー1aと、コラム線1bと、第1および第2のデータ線1d,1eと、データの読み出し時には、コラム線1bに第1および第2のデータ線1d,1eの一方を選択して接続し、データの書き込み時には、コラム線1bに第1および第2のデータ線1d,1eを接続するスイッチ1cと、第1および第2のデータ線1d,1eに接続された読み出し回路1fと、第1および第2のデータ線1d,1eに接続された書き込み回路1gと、を有する。

(もっと読む)

半導体記憶装置

【課題】メモリセルトランジスタからのデータの読み出しを高速化する。

【解決手段】メモリセルアレイ121は、メモリセルトランジスタ131及びローカルビット線LBLを含む第1回路部と、ローカルビット線LBLをグローバルビット線GBLに接続してメモリセルトランジスタ131に対する書き込み及び読み出しを行う第2回路部を含む。この第2回路部の、グローバルビット線GBLの電圧が印加されるnMOSトランジスタ151,152,154等に、耐圧を電源電圧としたものを用い、読み出しの高速化を図る。書き込みは、グローバルビット線GBLに電源電圧以下の電圧を印加し、ソース線SLに電源電圧よりも高い電圧を印加することで行う。

(もっと読む)

バイト、ページおよびブロックに書き込むことができ、セルアレイ中で干渉を受けず分割が良好な特性を備え、新規のデコーダ設計とレイアウトの整合ユニットと技術を使用する単体式複合型不揮発メモリ

【課題】

バイト、ページおよびブロックで書き込むことができる新単体式複合型不揮発メモリを提供する。

【解決手段】

不揮発メモリアレイは、シングルトランジスタフラッシュメモリセルおよびダブルトランジスタEEPROMメモリセルを備え、同じ基板上に整合することができ、該不揮発メモリセルは低いカップリング係数の浮遊ゲートを備えて、メモリセル体積を減少でき、該浮遊ゲートをトンネル絶縁層の上に配置し、該浮遊ゲートは該ソース領域の辺縁および該ドレイン領域の辺縁に揃って、且つ該ソース領域辺縁および該ドレイン領域辺縁の幅に画定される幅を備え、該浮遊ゲートと該制御ゲートは50%より小さい相対的に小さなカップリング係数を備えて、該不揮発メモリセルを縮小できるようにし、該不揮発メモリセルのプログラムはチャネル熱電子方式で達成し、消去は高電圧でFNトンネル方式で達成する。

(もっと読む)

多値ROMセル及び半導体装置

【課題】集積度が高く、製造ばらつきの影響が小さく、製造歩留まりの高い多値ROMセルを提供する。

【解決手段】多値ROMセルは、ROMセルトランジスタTrと、複数のビット線BT1〜BT3と、第1金属配線31〜44とを具備している。ROMセルトランジスタTrは、基板表面の領域に設けられている。複数のビット線BT1〜BT3は、基板表面の上方に設けられ、Y方向に伸び、Z方向に並んで配置されている。第1金属配線31〜44は、ROMセルトランジスタTrのソース・ドレイン22の一方に接続され、複数のビット線BT1〜BT3の各々の近傍にまで連なる。第1金属配線31〜44は、複数のビット線BT1〜BT3のうちのいずれかに接続されているか、又は、いずれにも接続されていない。

(もっと読む)

半導体記憶装置

【課題】リファレンスセルを有する半導体記憶装置でのデータ読み出しにおけるアクセス速度を向上することができる半導体記憶装置を提供することを課題とする。

【解決手段】リファレンスセル側において、リファレンスセルが接続されたビット線の一端をグローバルビット線に接続し、他端を負荷用ローカルビット線に接続することで、リファレンスセルが接続されたビット線及び負荷用ローカルビット線をグローバルビット線に対して直列に接続し、センスアンプからみたメモリセル側及びリファレンスセル側の負荷を揃え、データ読み出し動作のプリチャージにおける電位変化を過渡状態においても等しくなるようにする。所定のレベルに達したらプリチャージを終了しセンス動作を行えるので、プリチャージに要する時間を短縮でき、データ読み出しに係るアクセスタイムが短縮される。

(もっと読む)

不揮発性半導体記憶装置及びICカード

【課題】ピーク電流を低減する。

【解決手段】不揮発性半導体記憶装置10は、不揮発性メモリ11と、電圧発生回路24と、検知回路25とを含む。電圧発生回路24は、チャージポンプ30と、チャージポンプ30を動作させるクロックを生成するオシレータ32とを有し、かつ不揮発性メモリ11に電圧を供給する。検知回路25は、外部からの電源電圧を監視し、電源電圧が特定のレベルより低くなったことを検知する。電圧発生回路24は、電源電圧が特定のレベルより低くなった場合に、クロックの周波数を低くする。

(もっと読む)

1 - 20 / 639

[ Back to top ]