Fターム[5B125EG00]の内容

リードオンリーメモリ (43,397) | 電圧電流供給、設定構成 (1,974)

Fターム[5B125EG00]の下位に属するFターム

Fターム[5B125EG00]に分類される特許

1 - 8 / 8

複数のメモリブロックを備える不揮発性記憶装置

【課題】 読出し動作と書換え動作との間での干渉を防止することができ、メモリブロック間で読出し動作と書換え動作とを同時に行う場合に、誤動作を防止することが可能な不揮発性記憶装置を提供する。

【解決手段】 不揮発性記憶装置1は複数のバンクを備え、第1電源線VCC1及び第1接地線VSS1が接続され、バンクiに対する書換え動作を制御する書換え制御部2と、第2電源線VCC2及び第2接地線VSS2が接続され、バンクjに対する読出し動作を制御する読出し制御部5とを備え、書換え制御部2と読出し制御部5とは、互いに離間して配置される。

(もっと読む)

昇圧回路

【課題】電荷転送効率の低下を抑制し、各トランジスタの特性劣化を改善した上で、昇圧回路のセットアップ時間を短縮し、かつレイアウト面積を削減する。

【解決手段】複数段の昇圧セル101,102,103により構成される昇圧回路において、各昇圧セルに備えられている電荷転送トランジスタ933を当該昇圧セルより1段以上前段の昇圧セルの入力端子104,105の電圧によって制御することで、電荷転送トランジスタ933の端子間電圧を緩和する。

(もっと読む)

不揮発性メモリ・モジュール、半導体集積回路チップ、電子回路ユニット

【課題】 チップ/モジュールの面積を小さくして、製品単価を低くすること。

【解決手段】 不揮発性メモリ・モジュール(100A)は、メモリセル(102)と、外部クロック信号(SCLK)に同期して、外部のトリミングデータ書込み回路(500)で生成された昇圧回路(VPP)に基づいてトリミング情報をメモリセル(102)に書き込む書込制御回路(110A)とを有する。

(もっと読む)

高電圧回路のリセット回路

【課題】プログラム動作中又はプログラム消去動作中に電源遮断が起こったときに、リセット用トランジスタが劣化するのを防止する。

【解決手段】EEPROMのプログラム消去動作中に電源遮断が生じても、パワーオンリセット回路25の第1のリセット信号PORだけに基づいてシステムを一気にリセットするのではなく、第1のリセット信号POR及び低電圧検出回路24からの低電圧検知信号LDに基づいてリセットを行うことにより、高電圧HVが印加された状態で、高電圧スイッチ回路13のリセット用MOSトランジスタ133がオンすることがなく、リセット用MOSトランジスタ133や、これと同様に高電圧が印加される回路のトランジスタを保護することができる。

(もっと読む)

半導体集積回路

【課題】半導体集積回路上にメモリ、ロジック、アナログ等を混載し、他と異なる電源をメモリで使用する場合は電源配線を分けねばならず、それぞれの回路ブロックが半導体チップ上の任意の位置に分散して配置されているため、電源配線も分散して配置しなければならず、電源配線の低抵抗化が困難であった。

【解決手段】半導体集積回路上に、メモリマクロを群を成して配置したメモリブロックとして集中的に配置し、その近傍に外部からメモリ電源を供給するメモリ電源端子を配置し、メモリ電源端子からメモリブロックまでのメモリ電源配線を集中的にメモリブロック上に配置する。

これにより、メモリマクロに必要とされるメモリ電源配線領域を削減できるとともに、メモリ電源配線を低抵抗で配線することが可能となり、メモリマクロの安定動作を実現できる。

(もっと読む)

半導体記憶装置

【課題】 ワード線に温特をもたせることによる半導体記憶装置の回路規模が大きくなることを解消する半導体記憶装置を提供する。

【解決手段】 同一ウェル領域上に形成され、浮遊ゲートと制御ゲートが積層された複数のメモリセルが直列接続され、直列接続されたメモリセルの一端に第1の選択ゲートトランジスタが接続され、直列接続されたメモリセルの他端と共通ソース線の間に第2の選択ゲートトランジスタが接続されたメモリセルアレイと、第1の選択ゲートトランジスタの一端からビット線を介して接続され、メモリセルアレイのデータ読み出しを行うセンスアンプと、ウェル領域及びソース線に接続され、複数の抵抗を有し、抵抗の抵抗比を調整することにより、ウェル領域及びソース線に印加する電圧を変化させるバンドギャップ回路を備えることを特徴としている。

(もっと読む)

内部電圧発生器

【課題】工程の偏差により発生するトランジスタの電気的パラメータの変化に対しても相当な耐性があり、短いセットアップタイムで内部電圧を生成可能な内部電圧発生器を提供する。

【解決手段】内部電圧を生成させる比較器ブロックと出力駆動ブロックとを備え、比較器ブロックに供給する少なくとも二つの基準電圧を生成する基準電圧発生ブロック、及び基準電圧の電圧差であるオフセット区間を最適化させる制御信号を基準電圧発生ブロックに供給するオフセット区間制御ブロックが新たに考案されて追加され、電圧が印加される初期に内部電圧を短時間に生成させるためのセットアップタイムを短縮させると共に消費電力を低減させるために、メイン出力駆動ブロック以外に補助出力駆動ブロックが追加され、メイン出力駆動ブロックと補助出力駆動ブロックとの動作を制御する第1制御信号発生ブロック及び制御ブロックも新たに追加される内部電圧発生器である。

(もっと読む)

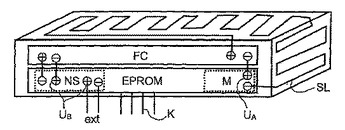

電源装置を装備したチップ

本発明は、機密データを記憶するためのメモリ(M)と、電圧および/または電流を印加するための電源装置(FC)と、他の装置からの、および/または他の装置へのデータの伝送のためのインタフェースとを装備したチップに関する。メモリ内のデータを安全にするため、電源装置(FC)はチップの、組み込まれた構成要素として形成されている。好ましくは電源装置(FC)は、限定されかつ再充填不可能である燃料貯蔵を有する燃料電池として装備されており、したがってメモリ内のデータは限定された寿命の間だけ保持されることができる。他の実施形態によれば電源装置(FC)から供給される電圧は、チップへの権限のないアクセスの場合にメモリ内のデータを能動的に消去するのにも使用することができる。  (もっと読む)

(もっと読む)

1 - 8 / 8

[ Back to top ]