Fターム[5B125EG01]の内容

リードオンリーメモリ (43,397) | 電圧電流供給、設定構成 (1,974) | 電圧供給回路 (1,008)

Fターム[5B125EG01]の下位に属するFターム

Fターム[5B125EG01]に分類される特許

1 - 20 / 27

不揮発性半導体記憶装置

【課題】低消費電流で正確なデータ読出を行なうことが可能な不揮発性半導体記憶装置を提供する。

【解決手段】このフラッシュメモリでは、4つのメモリマットMAT0〜MAT3の各々にセンスアンプSA0〜SAmを設け、通常の読出動作モードでは、全メモリマットMAT0〜MAT3のセンスアンプSA0〜SAmに参照電圧VRを供給し、低速読出モードでは、選択されたメモリマットMATのセンスアンプSA0〜SAmのみに参照電圧VRを供給する。したがって、低消費電力で正確なデータ読出を行なうことができる。

(もっと読む)

ディスク装置

【課題】電源遮断時に電源を供給できるキャパシタCsを備え、揮発性メモリ15を経由して不揮発性メモリ14にデータを格納し電源遮断時に揮発性メモリ15に格納されたデータを不揮発性メモリ14に格納できるディスク装置1において、キャパシタCsの容量を精度よく測定し、確実にキャパシタCsの寿命を判定できるようにする。

【解決手段】キャパシタCsの負荷となる測定用負荷21と、キャパシタCsへの電源入力側と電源出力側にそれぞれ備えるスイッチSW1とスイッチSW2と、キャパシタCsと測定用負荷21との間に備えスイッチSW1とSW2のオンオフと背反してオンオフするスイッチSW3とを備え、所定の時に、スイッチSW3をオンとしキャパシタCsが所定の電圧Va以下となるまでの放電時間Taを測定し、当該放電時間Taに基づいてキャパシタCsの容量を推定できるようにした。

(もっと読む)

不揮発性記憶装置、集積回路装置及び電子機器

【課題】書き込み動作時のディスターブ等を抑止できる不揮発性記憶装置、集積回路装置及び電子機器等の提供。

【解決手段】不揮発性記憶装置は、電気的にデータの書き込み及び消去が可能な複数の不揮発性メモリーセルが各メモリーブロックに設けられる第1〜第NのメモリーブロックMB1〜MB4と、第1〜第NのメモリーブロックMB1〜MB4に対応して設けられ、少なくとも書き込み動作に用いられる印加電圧VPPを第1〜第NのメモリーブロックMB1〜MB4に供給するスイッチ制御を行う第1〜第Nの電源スイッチ回路SC1〜SC4を含む。第1〜第Nの電源スイッチ回路SC1〜SC4のうちの第iの電源スイッチ回路は、第iのメモリーブロックへの入力データに基づいて、第iのメモリーブロックに印加電圧VPPを供給するか否かを切り替える。

(もっと読む)

半導体装置と、それを用いた可変インピーダンス回路および共振回路

【課題】電源電圧が遮断されている場合でも記憶データに基づいてスイッチ回路を導通状態または非導通状態にすることが可能な半導体装置を提供する。

【解決手段】この半導体集積回路装置では、浮遊ゲートおよび制御ゲートを有するメモリトランジスタMAと、ゲートが浮遊ゲートに接続され、メモリトランジスタMAの記憶データに応じてオンまたはオフするNチャネルMOSトランジスタQAとを含む。したがって、電源電圧VCCが遮断されている場合でも、メモリトランジスタMAの記憶データに基づいてトランジスタQAをオンまたはオフさせることができる。

(もっと読む)

半導体装置

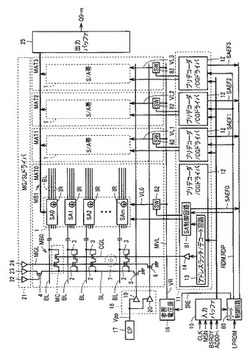

【課題】電源遮断時に不揮発性メモリへの誤書込の可能性を低減する。

【解決手段】不揮発性メモリ4は、外部から第1および第2の書換可能信号FHVED,FGVEIを受ける。第1の書換可能信号FHVEDは、ラッチ回路30Dを介してデータ領域10Dに設けられた第1の電圧供給制御部20Dに与えられる。第1の電圧供給制御部20Dは、第1の書換可能信号FHVEDが活性化状態の場合に、内部電源回路(昇圧回路)11で生成された高電圧をデータ領域10Dのメモリアレイ40Dに供給する。第2の書換可能信号FGVEIは、ラッチ回路30Iを介して第2の電圧供給制御部20Iに与えられる。第2の電圧供給制御部20Iは、第2の書換可能信号FHVEIが活性化状態の場合に、内部電源回路(昇圧回路)11で生成された高電圧をコード領域10Iのメモリアレイ40Iに供給する。

(もっと読む)

不揮発性半導体記憶装置

【課題】低消費電流で正確なデータ読出を行なうことが可能な不揮発性半導体記憶装置を提供する。

【解決手段】このフラッシュメモリでは、クロック信号CLKの立ち上がりエッジに応答して外部アドレス信号ADD0〜ADDiに従ってメモリセルMCを選択し、通常の読出モード時は、クロック信号CLKの立ち上がりエッジに応答してメモリセルMCからデータを読み出し、通常の読出モードよりも低消費電力で読出動作を行なう低速読出モード時は、クロック信号CLKの立下りエッジに応答してメモリセルMCからデータを読み出す。したがって、低速読出モードにおいてクロック信号CLKの立ち上がりエッジに応答してノイズが発生してもクロック信号CLKの立下りエッジではノイズレベルが低下しているので、正確にデータ読出を行なうことができる。

(もっと読む)

高電圧発生回路およびそれを備える不揮発性半導体記憶装置

【課題】1つの回路で正負高電圧を効率良く発生する高電圧発生回路を提供する。

【解決手段】チャージポンプ回路を構成するNMOSトランジスタが配置されるPウエル及び、本Pウエルの周辺及び底面を囲むNウエルで形成される寄生ダイオードが順バイアスにならないように各々のウエル電位を正確に制御することで、負高電圧出力時はSW2、SW3を導通状態とし、正高電圧出力時はSW1、SW4を導通状態とすることで、1つの回路で正負高電圧を効率良く発生可能なチャージポンプ回路を実現できる。

(もっと読む)

半導体メモリの内部電源制御回路

【課題】スタンバイモード時における消費電流を抑制すると共に、通常動作モードに移行した場合のアクセス速度の低下を抑制する。

【解決手段】内部電源制御回路26は、ROMの内部電源回路から内部回路に常時電源が供給される通常動作モードから消費電力を抑えるスタンバイモードに移行した場合に、内部電源回路から内部回路への電源供給を予め定めた周期で間欠的に許可するための内部電源イネーブル信号CEB_GENを生成するための周期信号TIM2を発生する周期信号発生回路34と、通常動作モード及びスタンバイモードの何れかのモードを示すチップイネーブル信号CEBと、周期信号TIM2と、が入力され、入力されたチップイネーブル信号CEBがスタンバイモードである場合に、周期信号TIM2に同期した内部電源イネーブル信号CEB_GENを内部電源回路に出力する間欠内部電源イネーブル信号発生回路36と、を含む。

(もっと読む)

半導体メモリの内部電源のスタートアップ回路

【課題】電源の遮断時に残留電位を速やかに放電することができる半導体メモリの内部電源のスタートアップ回路を提供する。

【解決手段】放電回路40が、放電用のNMOSトランジスタN4〜N6、電位補償用のNMOSトランジスタN7、及びカップリング容量により配線Gの電位を引き下げるDMOSトランジスタD2を含んで構成されている。電源電圧VCCの遮断時に、DMOSトランジスタD2及びNMOSトランジスタN7により配線Gの電位がマイナス電位に引き下げられ、NMOSトランジスタN4〜N6が動作して、配線D、E、Fの残留電荷を引き下げ、放電する。

(もっと読む)

不揮発性半導体記憶装置

【課題】消去動作を高速に実行可能にした不揮発性半導体記憶装置を提供する。

【解決手段】消去動作を行う場合において、選択ソース線SL0に消去電圧Vera1を印加する一方その他のソース線SL1〜3には接地電圧VSSを印加し、続いてソース側選択ゲート線SGS0に電圧Vera1よりも小さい電圧Vera2を所定時間遅れて印加する。一方、消去対象のメモリトランジスタMTrに接続されるワード線WL1に接地電圧VSSを印加する一方、それ以外のワード線WL0、2、3をフローティング状態とする。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置において、プログラム動作時においてメモリセルに接地電圧を印加するときに生じる、IR-DROPに起因した電圧上昇を抑制する。

【解決手段】メモリセルMCのソースおよびドレインと接続されたビット線MBL0,MBL1について、グランドとの間にディスチャージトランジスタD0,D1が設けられている。ディスチャージトランジスタD0,D1は、DSデコーダドライバ53によって生成出力された、互いに独立したディスチャージ制御信号DS0,DS1をゲートに受ける。メモリセルMCのプログラム動作時に、接地電圧を印加するビット線MBL0について、ディスチャージトランジスタD0を用いて接地電圧を設定することが可能になる。

(もっと読む)

メモリ装置、情報処理装置及び電力制御方法

【課題】不揮発性メモリにかかる電力制御をより効率的に行うことが可能な電力制御装置、情報処理装置及び電力制御方法を提供する。

【解決手段】複数のメモリ領域の各々に対応して設けられ、対応するメモリ領域の状態を活動状態とするか停止状態とするかを規定する第1設定情報を保持するモード設定手段と、前記複数のメモリ領域のうち、活動状態と規定された第1設定情報に対応するメモリ領域に電力を供給するとともに、停止状態と規定された第1設定情報に対応するメモリ領域への電力供給を停止する電源制御手段と、を備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】不揮発性メモリを搭載した半導体装置において、簡易な構成によって、外部からの電力供給の安定性が阻害された場合であっても書き込み動作等を確実に実行可能にする。

【解決手段】半導体装置1は、不揮発性メモリを含む不揮発性メモリコア10と、不揮発性メモリコア10への電力供給のモードを、外部電源から電力供給を行う第1モードと、バックアップ電源として用いられる蓄電デバイス31から電力供給を行う第2モードとで切り替えるスイッチ20とを備えている。不揮発性メモリコア10は、その動作状態を示すステータス信号を出力し、スイッチ20は、ステータス信号が示す不揮発性メモリコア10の動作状態に応じて、電力供給モードの切替を行う。

(もっと読む)

半導体記憶装置

【課題】基準電流の立ち上がりの高速化を図ることが可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、しきい値電圧に応じたデータを保持するメモリセルにデータを記憶し、読み出すことが可能な半導体記憶装置であって、基準電流生成部と、基準電流生成部の出力に応じて出力端子から配線に基準電流を出力するアンプ部と、を有する基準電流生成回路を備える。

(もっと読む)

双方向スイッチ回路

【課題】正電圧もしくは負電圧を印加しても、絶縁状態に設定されたスイッチ側は、絶縁状態を維持することが可能な双方向スイッチが望まれていた。

【解決手段】双方向スイッチ回路は、正電圧もしくは負電圧が印加される第1の端子と、

前記第1の端子に接続され、フローティング状態の第1のウェル内に形成される第1導電型の第1のトランジスタと、前記第1のトランジスタと第2の端子との間に接続される第1導電型の第2のトランジスタとを有し、前記第1及び第2のトランジスタは前記第1の端子と前記第2の端子との間の導通状態を制御する。

(もっと読む)

半導体記憶装置

【課題】不揮発性半導体記憶装置のデータ転送処理効率を改善する。

【解決手段】それぞれが複数の不揮発性メモリセルを有するメモリブロック(MB0−MB3)それぞれに対応してデータの書込/読出を行なうためのローカルバス(HB0−HB3)を設け、また各メモリブロックに対応してデータの書込/読出を行なうための回路(SA0−SA3,HSW0−HSW3)を設ける。さらに、これらのメモリブロックに共通に双方向でデータを転送するデータ転送線(BTX0,BTX1)と、メモリブロック間でデータ転送を行なうための転送スイッチゲート(TX0−TX3)を設ける。これらのメモリブロックをバンク(BNKA,BNKB)に分割し、メモリブロック個々にデータの書込/読出をバンク単位で行ない、書込/読出の並行実行および書込/読出と内部転送を行なう。

(もっと読む)

半導体記憶装置

【課題】動作速度を向上出来る半導体記憶装置を提供すること。

【解決手段】動作がプロセッサ2の制御によって自動で行われる半導体記憶装置1であって、不揮発性のメモリセルMCを備えたメモリセルアレイと、第1レジスタを保持し、電圧を発生する電源回路11と、第2レジスタを保持し、前記メモリセルからデータを読み出し増幅するセンスアンプ7と、第3レジスタ30を保持し、前記電源回路11と前記センスアンプ7の動作を制御する制御回路12と、前記第1乃至第3レジスタに命令を与えることにより、前記電源回路11、前記センスアンプ7、及び前記制御回路12の動作を制御する前記プロセッサ2とを具備し、前記制御回路12は、前記第3レジスタ30で受け取った前記命令をデコードして、デコード結果に基づいて前記電源回路11及び前記センスアンプ7を直接制御可能である。

(もっと読む)

半導体集積回路装置

【課題】消費電力を低減できる半導体集積回路装置を提供する。

【解決手段】半導体集積回路装置は、内部電源発生回路と、半導体メモリと、前記半導体メモリの不良情報を記録する記憶回路33と、前記不良情報が読み出された場合に、前記内部電源発生回路から発生する内部電源を停止するように構成された制御回路39とを具備する。

(もっと読む)

フラッシュメモリを備えた情報機器

【課題】

フラッシュメモリを用いて補助記憶装置を実現する際に、フラッシュメモリの欠点である消去回数の制限を補うハード構成とデータの扱い方に関する発明である。

【解決手段】

フラッシュメモリ1内部を、ファイルデータの書き込み消去単位であるセクタに分け、各セクタに書き込んだファイルに番号を付し、これを管理するテーブル5、6を備え、すでに書いたファイルの書換え時にも新たなデータとして別のセクタに書き込む。そして古いデータは消去して新たに書き込み可能領域としてテーブル5、6上で管理する。

(もっと読む)

半導体メモリ装置

【課題】低コストで大容量の半導体メモリ装置を実現する。

【解決手段】メモリカードは、メモリチップ100と、複数のメモリチップ200と、これらメモリチップを制御するメモリコントローラとから構成される。メモリチップ100は、メモリセルアレイ3、デコーダ4及びセンスアンプ5から構成されるNANDフラッシュメモリと、周辺回路6と、チャージポンプ部7と、ボンディングパッド領域2−1及び2−2から構成される。ボンディングパッド領域2−1にはチャージポンプ部7の出力電圧を外部に出力する端子パッド22が設けられ、メモリチップ200はメモリチップ100からの出力電圧を入力して動作する。メモリチップ200は電源回路を備える必要が無いため面積を削減することが可能である。このため、メモリカードの実装密度が向上し、低価格が実現できる。

(もっと読む)

1 - 20 / 27

[ Back to top ]