Fターム[5B125EK10]の内容

リードオンリーメモリ (43,397) | 外部接続構成、外部出力情報 (1,198) | メモリの状態情報の出力 (341) | エラー情報 (147)

Fターム[5B125EK10]に分類される特許

1 - 20 / 147

暗号化演算装置を搭載する不揮発性半導体記憶装置

ホスト装置、装置、システム

メモリシステム及びそれの動作方法

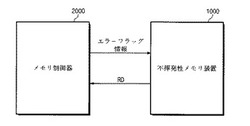

【課題】動作速度及び電力消耗を減らすことができるメモリシステム及びそれの動作方法が提供される。

【解決手段】本発明の実施形態によるメモリシステムは不揮発性メモリ装置と、前記不揮発性メモリ装置を制御するように構成されたメモリ制御器と、を含み、前記メモリ制御器は前記不揮発性メモリ装置から読み出されたデータのエラーの位置情報を含むエラーフラッグ情報を前記不揮発性メモリ装置へ提供する。

(もっと読む)

不揮発性メモリ装置のデータリード方法、及びそれを行う装置

【課題】新たなリードパラメータで不揮発性メモリ装置をリードするリードリトライを行う方法、該方法を行う装置を提供する。

【解決手段】リードリトライ動作及び/またはその部属的なリードリトライ動作は、リードリトライ動作が保証(warranted)されるか否かを判断する前に初期化されるか、完了することができる。例えば、NANDフラッシュメモリ装置のページは、新たなリード電圧レベルをページのワードラインに印加して、リードリトライ動作でリードされうる。例えば、リードリトライ動作は、エラー訂正動作でターゲットページのデータの以前リードページのエラーを訂正不能と判断される前に、ターゲットページで行われる。

(もっと読む)

不揮発性半導体記憶装置

【課題】不良ブロック情報を適切に管理することのできる不揮発性半導体記憶装置を提供する。

【解決手段】一の実施の形態に係る不揮発性半導体記憶装置は不揮発にデータを記憶する複数のメモリセルを配列してなる複数のブロック、並びにメモリセルと接続されるワード線、及びビット線を有するメモリセルアレイと、メモリセルアレイ内に設けられ、ブロックが不良ブロックであること示す不良ブロック情報を不揮発に記憶可能に構成された不良ブロック格納領域と、ワード線を選択するロウデコーダと、メモリセルに対するデータの書き込み、消去及び読み出しを制御する制御回路とを備える。制御回路は、不良ブロック格納領域に書き込まれた不良ブロック情報をビット線を介して外部へ出力する出力動作を実行可能に構成されるとともに、外部から入力された不良ブロック情報をビット線を介して不良ブロック格納領域に書き込む第1の書き込み動作を実行可能に構成される。

(もっと読む)

半導体装置

【課題】データ書き替えの繰り返しによってメモリセルの閾値電圧が下がりくくなることを防止する。

【解決手段】半導体装置1の各メモリセルMCは、共通の浮遊ゲートFGを有する第1のトランジスタ(読出用)TRAと第2のトランジスタ(書込用)とを含む。制御回路11は、一方のトランジスタに通電したときにメモリセルに流れる電流と、両方のトランジスタに通電したときにメモリセルに流れる電流とを比較することによって、第1および第2のトランジスタにそれぞれ接続されるサブビット線SBL_R,SBL_P間のショートを検出する。

(もっと読む)

不揮発性半導体メモリ

【課題】フェイルビット数を高速に検知する。

【解決手段】実施形態に係わる不揮発性半導体メモリは、第1の単位のデータをz個の第2の単位のデータに分け、各第2の単位のデータについてフェイルビットを累積するアキュムレータ12と、書き込み後にフェイルビットを検知する動作を制御する制御回路10とを備える。制御回路10は、各第2の単位のデータについて、そのうちの第3の単位のデータをセンスアンプSA0に記憶させ、センスアンプSA0から、各第2の単位のデータを1ビットずつ、合計zビットずつパラレルに読み出し、検知回路DTCT0を用いてzビットからフェイルビットを検知し、zビットをアキュムレータ12に転送することにより、各第2の単位のデータについてフェイルビットを累積する。

(もっと読む)

半導体記憶装置

【課題】ベリファイ・フェイル数を精度良くカウント可能な半導体記憶装置を提供すること。

【解決手段】実施形態の半導体記憶装置1は、複数のメモリセルMTと、論理ゲートチェーン52と、カウンタ30を備える。メモリセルMTは、いずれかのカラムに関連付けられ、データ保持可能である。論理ゲートチェーン52は、いずれかのカラムに対応付けられ、且つ対応付けられたカラムにおけるベリファイ・フェイルの有無を示す論理レベルを次段に出力するように直列接続された複数の論理ゲート51を含む。カウンタ30は、直列接続の最終段の論理ゲートによる、ベリファイ・フェイルがあることを示す論理レベルの出力回数をカウントする。論理ゲートチェーン52は、各々の論理ゲート51の出力する論理レベルの示す内容が、ベリファイ・フェイルのあるカラムに対応する論理ゲート51を境界にして反転するように構成される。

(もっと読む)

半導体メモリおよびシステム

【課題】 1つをメモリブロックの書き込み動作中に、別のメモリブロックの読み出し動作を実行することで、アクセス効率を向上する。

【解決手段】 半導体メモリは、複数ビットの書き込みデータおよび書き込みデータのパリティデータをビット毎に保持する複数のメモリ領域を有する複数のメモリブロックを有している。書き込みコマンドに応答して、メモリブロックの1つである書き込みメモリブロックのメモリ領域に、書き込みデータおよびパリティデータが順に書き込まれる。読み出しコマンドに応答して、書き込みメモリブロックを除くメモリブロックの1つにおいて、書き込みデータおよびパリティデータが供給されていないデータ線に対応するメモリ領域からデータが読み出され、書き込み動作により読み出させないデータが再生される。これにより、書き込み動作と並行して読み出し動作を実行できる。

(もっと読む)

不揮発性半導体メモリ

【課題】プログラム後の読み出し不良をプログラム動作の終了前に判定する。

【解決手段】実施形態に係わる不揮発性半導体メモリは、選択ワード線に対する書き込みパルスの印加とベリファイ読み出し動作とを繰り返す第1の手段(ステップST1〜ST5)と、ベリファイ回路によりプログラムデータの記録が完了と判断された後に選択メモリセルに対して読み出し動作を行う第2の手段(ステップST6)と、この読み出し動作により読み出されたデータとプログラムデータとが一致するときに外部コントローラにプログラム動作がパスしたことを示すステータス情報を出力し、両者が一致しないときに外部コントローラにプログラム動作がフェイルしたことを示すステータス情報を出力する第3の手段(ステップST7)とを備える。

(もっと読む)

半導体装置

【課題】メモリセルの劣化がある程度進行している状態と、要求仕様を満たさなくなるまで劣化が進行した状態とを外部で認識できるようにする。

【解決手段】半導体装置1において、メモリセルMCは、閾値電圧の相違を利用してデータを不揮発的に記憶する。制御回路11は、データ消去時、メモリセルの閾値電圧が第1ベリファイ電圧以下でない場合にはメモリセルに閾値電圧を小さくするための消去電圧を印加する。制御回路は、消去電圧の印加時間が第1の判定値を超えると第1の劣化状態を表わす信号を出力し、消去電圧の印加時間が第1の判定値より大きい第2の判定値を超えると第2の劣化状態を表わす信号を出力する。

(もっと読む)

半導体記憶装置及びその制御方法

【課題】半導体記憶装置に対する書き込み/読み出しに影響を与えることなく、読み出し時にエラー訂正されたデータを、メモリ本体に再書き込みする。

【解決手段】実施形態に係る半導体記憶装置1は、エラー訂正部9、第1の記憶部10、第2の記憶部11、制御部13を含む。エラー訂正部9は、メモリ本体8から読み出されたデータに対するエラー訂正を行う。第1の記憶部10は、エラー訂正部9によって訂正されたデータを記憶する。第2の記憶部は、エラー訂正部9によって訂正されたデータに対応するアドレスを記憶する。制御部13は、メモリ本体8に対する読み出し/書き込みが実行されていないタイミングにおいて、第1の記憶部10に記憶されているデータと第2の記憶部11に記憶されているアドレスに基づいて、メモリ本体8に対して再書き込みを行う。

(もっと読む)

複数の独立したシリアルリンクメモリ

【課題】半導体メモリにおけるシリアルデータリンクインターフェイスとメモリバンクとの間のデータ転送を制御する装置、システム、および方法が開示される。

【解決手段】一例では、リンクがバンクと独立している、複数のシリアルデータリンクおよび複数のメモリバンクを備えるフラッシュメモリ装置が開示される。エコー信号ラインを使用して、フラッシュメモリ装置をデイジーチェーン構成においてカスケードし、メモリ装置間で連続的に通信してもよい。さらに、単一リンクを使用して複数のリンクをエミュレートする仮想複数リンク構成が記載されている。

(もっと読む)

不揮発性記憶装置、電子機器

【課題】 センスアンプの故障とメモリーセルの故障とを区別できる信頼性の高い故障診断を行う不揮発性記憶装置等を提供する。

【解決手段】 不揮発性記憶装置1であって、テストデータを含む第1のデータ群を、1ビット毎に記憶する第1のメモリーセルで構成される第1のブロック10−1と、第1のデータ群の各データを相補するデータから成る第2のデータ群を1ビット毎に記憶する第2のメモリーセルで構成される第2のブロック10−2と、2つの入力信号の差に基づく出力値を生成する少なくとも1つの差動センスアンプ30−1〜30−Nと、差動センスアンプからの値を用いて故障診断を行う診断回路40と、制御回路90と、を含み、制御回路は、テストデータとその相補データに基づく信号を差動センスアンプの入力信号とし、診断回路が差動センスアンプの故障診断を実行するように制御する。

(もっと読む)

NANDフラッシュメモリの劣化早期検知

【課題】NANDフラッシュメモリの劣化早期検知を提供する。

【解決手段】読み込み動作中にNANDフラッシュメモリセルの組(例:ページ)の閾値電圧(VT)の分散を測定することによりNANDフラッシュメモリの低下を早期検知する技術を記述する。本発明の実施形態において、メモリセルの読み込み動作の完了時間(TTC)値を閾値電圧(VT)の分散の代替値として用いる。分散アナライザがTTC値の組の分散を判定する。一実施形態において、TTCの最大値と最小値の差分を分散測定値として用いる。測定されたTTCの分散が、選択された量より大きく基準分散値から異なる場合、メモリの当該ページが劣化したことを示す警告信号が出力される。警告信号を用いて、データを新規ページに移動させる等の適切な措置をとることができる。

(もっと読む)

障害の確率を利用したフラッシュメモリのデータ管理

【課題】障害の確率を利用したフラッシュメモリのデータ管理を提供する。

【解決手段】障害を誘発する動作に対するシステムの感度およびそのシステムによって実行される障害誘発動作の履歴を用いるフラッシュメモリシステムとデータ管理の方法が開示される。本発明のある実施形態において、障害誘発動作に対する感度は障害強度マトリクスに表され、このマトリクスには、選択された動作に、その動作がデータエラーの原因となる電荷の障害を引き起こす相対的な強度の推測である数値が関連付けられている。障害強度マトリクスにはまた、電荷の注入または消失のいずれかを示すエラーの方向も含むべきである。障害強度マトリクスは、デバイスがセルフテストを実行し、その中では、検出可能な変化が発生するまで選択された動作を実行することによって、測定された分散値の変化を起こすようにすることによっても決定できる。

(もっと読む)

NORフラッシュメモリの劣化早期検知

【課題】NORフラッシュメモリの劣化早期検知を提供する。

【解決手段】ここに開示する本発明の実施形態は、読み込み動作中にNORフラッシュメモリセルの組の閾値電圧(VT)の分散を推定することによりNORフラッシュメモリの劣化を早期警告する技術を記述する。発明の一実施形態において、メモリセルの読み込み動作の完了時間(TTC)値を閾値電圧(VT)の分散の代替値として用いる。測定されたTTCの分散が基準分散値と選択された量よりも大きく異なる場合、メモリの当該ページがかなり劣化したことを示す警告信号が出力される。システム内のより高次の要素が当該警告信号を用いて適切な措置をとることができる。理想的な分布における全てのセルのVT位置を推定することができるため、理想的な分布の平均からの発散に基づいて各セルからのデータに信頼レベルを割り当てることができる。

(もっと読む)

半導体記憶装置、及び記憶方法

【課題】半導体記憶装置において、読み出し精度を維持しつつ、書き込み及び読み出しを繰り返すプログラムベリファイに要する時間を短縮する。

【解決手段】メモリセルアレイ内のメモリストリングからデータのベリファイ読み出しを行う場合、フェイルビットカウンタがインヒビットセル数及びフェイルセル数をカウントし、制御回路がカウントしたインヒビットセル数及びフェイルセル数から共通ソース線CSLに流れる電流により生じる共通ソース線CSLの浮き上がり電圧を算出するとともに、算出した電圧に応じて、ビット線及びワード線に印加する電圧を補正する。

(もっと読む)

フラッシュメモリ装置及びそれの読み出す方法

【課題】エラー訂正に所要される性能損失は最少化しながら、エラー訂正の効率は増進させ得るフラッシュメモリ装置及びそれの読み出すための方法が提供される。

【解決手段】本発明のフラッシュメモリの読み出す方法は、ソフト判定読出しコマンドとアドレスとに応答して対応されるフラッシュメモリセルから複数の読出し動作を遂行する段階と、前記複数の読出し結果からハード判定データと、1つ又はその以上の信頼性データビットを決定する段階と、連続的に発生した複数のソフト判定出力コマンドに応答して、前記ハード判定データと、前記信頼性データの各ビットを最上位ビットから最下位ビット順に順次的に出力する段階と、を含み、前記順次的に出力された前記ハード判定データと前記信頼性データの各ビットとはエラー訂正回路に提供されて前記ハード判定データを適用したエラー訂正動作と、前記信頼性データの各ビットを利用する複数のエラー訂正動作に段階的に適用され、前記ソフト判定出力コマンドは前記複数のエラー訂正動作結果にしたがって選択的に発生し得る。

(もっと読む)

不揮発性メモリ装置の読み出し方法及びメモリコントローラの動作方法並びにメモリシステムの動作方法

【課題】リードリトライを行うアルゴリズムの実行回数を減らして、読み出し性能を向上させうる不揮発性メモリ装置の読み出し方法及びメモリコントローラの動作方法並びにメモリシステムの動作方法を提供する。

【解決手段】本発明による不揮発性メモリ装置の読み出し方法は、リード電圧を用いてメモリセルアレイに保存された第1データを読み出す段階と、前記第1データに含まれた“1”と“0”とのうちの何れか一つの個数をカウントしたカウント値と基準カウント値とを比較し、該比較結果に従って、前記メモリセルアレイの第1領域に保存された第2データを読み出すために、前記リード電圧を変更する段階とを有する。

(もっと読む)

1 - 20 / 147

[ Back to top ]