Fターム[5B176EB01]の内容

ストアードプログラム (10,932) | ROM修正 (612) | ROMプログラミング (546)

Fターム[5B176EB01]の下位に属するFターム

ROMライタ (208)

CPUによる再プログラミング (280)

Fターム[5B176EB01]に分類される特許

1 - 20 / 58

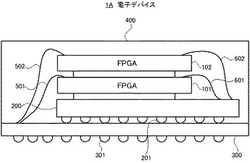

電子デバイス、電子デバイスの故障検出方法および電子デバイスの故障回復方法

【課題】SRAM型FPGAを用いて構成された電子デバイスが動作している状態で、SRAM型FPGAに生じたソフトエラーを検出し、ソフトエラーによる故障を回復する。

【解決手段】SRAM型FPGA101とSRAM型FPGA102は、同一のコンフィグレーションデータを記憶しており、同一の回路として動作する。SRAM型FPGA101とSRAM型FPGA102には、SiP基板300を介して同一の信号(データ)が入力される。選択チップ200には、SRAM型FPGA101とSRAM型FPGA102の出力する信号が入力される。選択チップ200は、SRAM型FPGA101とSRAM型FPGA102の出力する各信号を個々に比較している。選択チップ200は、出力された信号の中に異なるものがあることを検出すると、SRAM型FPGA101とSRAM型FPGA102のいずれかまたは両方を再コンフィグレーションする。

(もっと読む)

操作部制御ユニット、バージョン制御方法及び画像形成装置

【課題】ユーザにとってインストール作業が容易で、複雑でないインストール手順によって、バージョンアップが可能な操作部制御ユニット、バージョン制御方法及び画像形成装置を提供する。

【解決手段】画像形成装置101を構成する他のサブユニットと接続され、ユーザに画像形成装置101の操作インターフェースを提供し、可搬型記憶媒体を装着可能な操作部制御ユニット107であって、操作部制御ユニット107の制御プログラムを格納するためのROM202と、可搬型記憶媒体ROM211を装着する可搬型記憶媒体装着部213と、ROM211から、制御プログラムを読み出し、ROM202へ転送することによって操作部制御ユニット107に制御プログラムをインストールするDMAコントローラ212と、を有することを特徴とする。

(もっと読む)

論理制御装置およびプログラム書き込み方法

【課題】PLDを複数搭載したボードの不具合に対する原因究明の時間短縮のため、プログラムの誤書き込みを検出すること。

【解決手段】コンフィグレーション制御部20は、各デバイス30に本来のプログラムを書き込む前に、ナンバリング用のプログラムを書き込み、通知データの受信順にデバイス30に対して番号を付与する。番号付与後、各デバイス30に本来のプログラムを書き込む。本来のプログラムには、予め固有の番号(以下、機能番号)が格納されており、デバイス30にプログラムを書き込むことで当該機能番号を取得する。そして、コンフィグレーション制御部20は、各デバイス30から通知された機能番号と、先にデバイス30に対して付与した付与番号とを比較し、その整合性を判断する。両者の整合性がとれていなければ、プログラム保持部40へプログラムを書き込む際に、順序を誤って書き込んだものと判断することができる。

(もっと読む)

ファームウェア更新装置およびファームウェア更新システム

【課題】

装置内の各モジュールに設定されていた設定情報が削除されてしまうことなくファームウェアの更新が行われるファームウェア更新装置およびファームウェア更新システムを提供する。

【解決手段】

PC10において、プリンタ30より各モジュールのファームウェアのバージョン番号が取得され、サーバ20より最新版のファームウェアのバージョン番号が取得され、更新が必要なファームウェアが特定され、ファームウェアの更新に際して各モジュールに設定される設定情報のうち保存が必要な設定情報がストレージ13に記憶され、サーバ20から取得された最新版のファームウェアを各モジュールに更新した後、ストレージ13に記憶された設定情報が各モジュールに再設定される。

(もっと読む)

宅内設備機器用のネットワークシステム

【課題】複数の宅内設備機器が接続されたネットワークシステムにおいて、ソフトウェアの更新が必要な設備機器があることをユーザが容易に認識でき、更新が適時に実行されることを低コストで可能とする。

【解決手段】宅内設備機器用のネットワークシステム10に接続された宅内サーバ11は、宅外のセンターサーバ15から取得した最新バージョン情報115と、設備機器12から取得したバージョン情報112とを比較してソフトウェアの更新が可能な設備機器12を判断する。ソフトウェアの更新が可能な設備機器12があることを通知するための更新通知画面が宅内表示器121に表示される。ユーザに選択された設備機器12は、センターサーバ15から更新データを取得してソフトウェアの更新を実行する。これにより、ソフトウェアの更新を適時に実行することが低コストで可能になる。

(もっと読む)

リコンフィギュアラブル回路、コンフィギュレーション方法およびプログラム

【課題】本発明は、チップ面積の増加を招くことなく、コンフィギュレーション時間を大幅に短縮することができるリコンフィギュアラブル回路、コンフィギュレーション方法、およびプログラムを提供すること。

【解決手段】本発明は、複数のシリアル接続レジスタを有するコンフィギュレーションチェーンを具備するリコンフィギュアラブル回路において、第1のシリアル接続レジスタ内のレジスタおよび第2のシリアル接続レジスタ内のレジスタを直列に接続する第1の接続手段と、第1のシリアル接続レジスタ内のレジスタと第2のシリアル接続レジスタ内のレジスタとを並列に接続する第2の接続手段とを具備して、第2の接続手段をバイパスとして複製可能に構成されている。

(もっと読む)

画像処理装置及び起動方法

【課題】適切な組み合わせで制御プログラムが動作するよう制御すると共に、制御プログラムのバージョンアップに伴うダウンタイムを削減することを目的とする。

【解決手段】新規の本体制御ソフトウェアと組み合わせて動作可能な後処理装置の制御に関する後処理装置制御ソフトウェアのバージョン情報と後処理装置で動作中の後処理装置制御ソフトウェアのバージョン情報、に基づいて、新規の本体制御ソフトウェアと後処理装置で動作中の後処理装置制御ソフトウェアとの組み合わせが適切か否かの判定を行う組み合わせ判定手段と、組み合わせ判定手段における判定結果を不揮発性の記憶装置に記憶する判定結果記憶手段と、起動要求を受け取った後、不揮発性の記憶装置に記憶されている判定結果に応じて、本体制御ソフトウェアを起動する起動手段と、を有することによって課題を解決する。

(もっと読む)

動的再構成可能演算装置および半導体装置

【課題】面積効率の高い動的再構成可能演算装置を得る。

【解決手段】乗算器100〜107は、それぞれ2入力の乗算を行う。加算器200〜203は、乗算器100〜107の乗算結果出力100c〜107cを入力として加算を行う。加算器204,205は、加算結果出力200a〜203aか乗算結果出力100c,101c,106c,107cかを入力として加算を行う。加算器206,207は、加算結果出力204a,205aか乗算結果出力102c〜105cかを入力として加算を行う。

(もっと読む)

デジタル放送受信機

【課題】受信機ソフトウェアの更新を、受信機ハード個体を限定して実施したり、ユーザーの利用状態に応じて実施したりすることのできる受信機を提供する。

【解決手段】受信機の情報格納用メモリー107上に個体識別を表す数字や文字・記号を出荷までに記憶させる。ソフトウェア更新を行う事が決定したら、告知情報中の「メーカーが自由に利用できる情報エリア=private_data_byte」に更新対象となる受信機個体を特定する数字や文字・記号を記載し、放送波での送出を開始する。受信機は告知情報をチューナー部101、デモジュレータ部102、DeMUX部103を経てCPU部106との間で「メーカーID」「モデルID」を取得し、自己機が対象と判断できれば告知情報の「private_data_byte」と情報格納用メモリー107の個体識別を表す情報と比較処理し、一致した場合「ソフトウェア送出チャンネルと日時の情報」を基に予約起動用サブCPU108へ受信予約登録を行う。

(もっと読む)

信号処理装置

【課題】信号処理の内容変更を柔軟且つ簡単に行うことが可能な信号処理装置を提供する。

【解決手段】命令ROM11に所定の一連の処理として実行されるプログラムモジュールが複数格納されており、その実行順序を、データRAM13にプログラムモジュールの格納アドレスを指定する制御情報を書き込むことで制御する。制御情報は、プログラムモジュールを実行すべき順番に格納アドレスを配列してなり、その順番に従ってプログラムモジュールが読み出されて、演算処理が行われる。

(もっと読む)

投影装置、投影装置用光源ランプユニット、投影装置の投影制御方法及びプログラム

【課題】ユーザ自身は意識せずにプログラムのバージョンアップを実施する。

【解決手段】装置に対して着脱自在に装着され、光源ランプ18、装置のプログラムを記憶したメモリ29を備えたランプユニットLUと、光源ランプ18からの光を用い、入力される画像信号に応じた光像を形成して出射する投影系(11〜16,19〜27)と、プログラムを記憶するプログラムメモリ32と、プログラムメモリ32に記憶したプログラムに従い、投影系(11〜16,19〜27)での画像投影を含む装置の動作を制御すると共に、メモリ29,32に記憶される各プログラムのバージョン情報に基づき、メモリ29に記憶されるプログラムをプログラムメモリ32に転送して更新記憶させるCPU31及びメインメモリ33とを備える。

(もっと読む)

車両制御装置及びそのデータ書換システム

【課題】許可の無い者による車両制御装置のデータ書き換えの無断実行をより確実に回避することのできる車両制御装置及びそのデータ書換システムを提供する。

【解決手段】無線通信ネットワーク11を通じて配信された書換用データに基づく車両制御装置のデータ書き換えの実行に際して、ユーザーが手動入力したIDコードと車両20に予め記憶されたIDコードとの照合に基くユーザー識別検査を実施する。そしてそのユーザー識別検査の結果、データ書き換えの実行を許可された特権ユーザーであることが確認されることを条件に、上記配信された書換用データに基くデータ書き換えの実行を許可することとした。

(もっと読む)

電子機器および電子機器制御プログラム

【課題】 垂直接続される複数の制御基板に対し、制御プログラムの不必要な書き換えを防止できるようにする。

【解決手段】 電子機器本体部1には制御基板3、5、7を接続する。制御基板3、5、7は通信部33、41、53、59、73、79、記憶部37、55、75、制御部43、61、81を有する。通信部33〜79は電子機器本体部1から制御基板3〜7を垂直的に接続する。記憶部37〜75は電子機器本体部1からの制御プログラムを記憶する。制御部43〜81は、記憶部37〜75の動作異常を検知して上位側に出力制御し、直近の下位制御基板5、7からの異常情報を保持制御する。制御部43〜81は、制御プログラムが当該制御基板3〜7宛先であれば記憶部37〜75に記憶制御し、宛先でなければ通信部41〜79を介して制御基板5、7に送信制御し、異常情報を受けた制御基板5、7に対するダウンロード指示の送信を停止制御する。

(もっと読む)

ソフトウェア修正装置

【課題】ROMコレクション機能を搭載したマイクロコンピュータと修正プログラムを格納した不揮発性メモリとを備えた家電製品等の応用システムにおいて、不揮発性メモリに格納されたデータの書き換えを安全に実施する。

【解決手段】ROM5と、ROMの修正プログラムを格納する不揮発性メモリ1と、ROMの修正プログラムを読み出すプログラム読み出し手段3と、読み出された修正プログラムを格納するRAM4と、修正プログラムに基づいてROMのプログラムを修正した動作を行うROM修正制御手段2と、不揮発性メモリ1のデータ書き換えを行うデータ書き換え手段6と、不揮発性メモリ1のデータ書き換えモードに切り替えるモード切り替え部7と、RAM4のデータを一定周期でリフレッシュを行うデータリフレッシュ手段8と、データ書き換えモード中はRAM4のリフレッシュ動作を禁止するリフレッシュ判定手段9とを備える。

(もっと読む)

データ通信装置、設定情報更新方法および設定情報更新プログラム

【課題】エンドユーザに対するサービスを停止させることなく、プログラマブル論理回路のコンフィグレーションデータをアップグレードすることを課題とする。

【解決手段】ルータ30のコンフィグレーションコントロール部は、プログラマブル論理回路(FPGA)のコンフィグレーションデータをアップグレードする場合、ルータ20からのデータの送信を一時的に停止させるためバックプレッシャ要求信号を生成して論理ゲート部に送出する。ルータ20からのデータの送信が停止している間、コンフィグレーションコントロール部は、プログラマブル論理回路(FPGA)のバッファに蓄えられている全てのデータを送出させた後、フラッシュメモリからアップグレードされたコンフィグレーションデータを読み出して、プログラマブル論理回路(FPGA)に転送する。

(もっと読む)

マイクロコンピュータ

【課題】不揮発性メモリの書換えが失敗した場合に、外部端子を介してモード切替えを行わずとも書換えプログラムを再起動できるマイクロコンピュータを提供する。

【解決手段】マイコンのCPUが書換えプログラムを実行すると、最初にフラッシュメモリのFLASHステータス0をクリアしてから当該メモリの全領域の書換えを行ない、最後にFLASHステータス0に書換え完了コードを書込む。そして、CPUが判定プログラムを実行すると、最初にフラッシュメモリのFLASHステータス0を読出し(ステップS1)、そのデータが書換え完了コードに一致しない場合(「NO」)、CPUはIDステータス2_1,2_2の読出しデータが共にIDコードに一致することを確認すると(ステップS5,「YES」)、書換えプログラムを再度実行する。

(もっと読む)

中性子計測用のデータ収集装置

【課題】複数の子基板で個別に測定される測定データの同期を正確で且つ容易にとることができるようにすること。

【解決手段】親基板11と複数の子基板12a〜12dとを備えた中性子計測用のデータ収集装置において、子基板12a〜12dの入力端子となる子基板側ピン配列27を共通接続し、親基板11からは子基板側ピン配列27の一つに中性子飛行時間測定のための時間信号、子基板を選択する選択信号を与える。子基板12a〜12dには、時間信号が第1段目に入力するシフトレジスタ41と、シフトレジスタ41の第1段目から第3段目の論理積を求めるAND回路42と、時間信号をカウントすると共にAND回路42の出力にてゼロクリアされる時刻カウンタ43とを具備する。

(もっと読む)

ASICシステム

【課題】ファームウェアの正当性の確認を高速に行うことが可能なASICシステムを提供する。

【解決手段】 制御装置5と、RAM4と、ファームウェアが格納されるフラッシュROM3と、フラッシュROM3に格納されているファームウェアを読み出し、システムバス2を介してRAM3に転送するデータ転送装置6と、システムバス2に読み出されたファームウェアを取得して前記ファームウェアの正当性を判別する正当性確認装置7とを具備し、正当性確認装置7によってファームウェアの正当性に問題があると判別した場合、制御装置5はRAM3に転送されたファームウェアを実行しないようにする。

(もっと読む)

情報処理装置及び情報処理装置の制御方法、情報処理システム

【課題】 プリンタなどの情報処理装置が電子証明書データを確実に取得して更新することができるとともに、従来の装置構成に対する大幅な機能追加をすることなく、電子証明書データの取得機能を備えた情報処理装置及び情報処理装置の制御方法、情報処理システムを提供する。

【解決手段】 更新版ファームウェアは1つのバイナリファイル形式となっており、このファイル内にはコントローラ部31を動作する上で必要なファームウェアデータと、プリンタ3がコンテンツサーバ2とセキュアな通信を行う上で必要となるルート証明書データが含まれている。取得した更新版のファームウェアから、当該ファームウェアに含まれるルート証明書データの固有情報を抽出し、抽出した固有情報を用いてRAM313に設けられたルート証明書の管理テーブルを更新する処理を実行する。

(もっと読む)

情報処理装置

【課題】制御プログラムのバージョンアップにおいて誤ったバージョンアップをユーザに行わせないようにし、動作不良の発生を防止した情報処理装置を提供する。

【解決手段】BEマイコン12は、FE用F/W111の現在のバージョンが適正バージョンであるかどうかを、図2(A)に示す更新ファイル110の適正バージョン情報に基づいて判定する(S5)。例えばFE用F/W111の現在のバージョンが「3、0」である場合、図2(A)に示すようにFE用F/W111の適正バージョンは「3、0以上」であるため、BEマイコン12は、FE用F/W111の現在のバージョンが適正バージョンであると判定する。そして、FE用F/W111の現在のバージョンが適正バージョンであると判定すると、BEマイコン12は、フラッシュROM20に記憶されているBE用F/W112を更新ファイル110によってバージョンアップする。

(もっと読む)

1 - 20 / 58

[ Back to top ]