Fターム[5E032TA14]の内容

抵抗器の製造装置と方法 (2,161) | トリミング構造 (128) | 抵抗物質の除去 (92) | 直線状カット (54) | L字カット (13)

Fターム[5E032TA14]に分類される特許

1 - 13 / 13

チップ用抵抗体の抵抗値調整方法

【課題】チップ抵抗器の製造過程でトリミング不良の発生を迅速かつ的確に検出できるチップ用抵抗体の抵抗値調整方法を提供する。

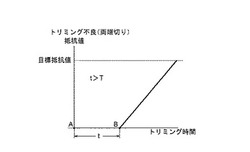

【解決手段】集合基板20に所定の配列で印刷形成された多数の抵抗体5に対して、順次、抵抗値を測定しながらレーザビームを照射してトリミング溝11を形成するというレーザトリミングを実施する際に、レーザビームの照射が開始された時点から、抵抗体5にレーザビームが到達してトリミング溝11が形成され始めるまでの経過時間(抵抗体到達時間t)を測定抵抗値の変化に基づいて計測し、この抵抗体到達時間tを予め設定された許容時間Tと比較する。そして、抵抗体到達時間tの計測値がゼロ(t=0)または許容時間Tよりも長い(t>T)ときだけ、トリミング不良が発生したものと判定する。

(もっと読む)

チップ抵抗器

【課題】小型で耐サージ特性に優れ、また放熱性に優れ、同じチップ面積でより大きな定格電力を持つチップ抵抗器を提供する。

【解決手段】絶縁基板30に形成した一対の電極36間を絶縁基板30の表面又は裏面に形成した蛇行する抵抗体35で接続したチップ抵抗器であって、絶縁基板30の表面又は裏面に形成された蛇行する溝状凹部に、絶縁基板30の表面又は裏面と略同じ高さまで前記抵抗体35を埋設する。

(もっと読む)

トリミング装置およびトリミング方法

【課題】チップ抵抗の歩留まりを向上させる。

【解決手段】トリミング装置11は、チップ抵抗基板12のチップ抵抗の電極間を横断するy方向にトリミングを行った後、一方の電極に向かうx方向にトリミングを行うことによりチップ抵抗の抵抗値を調整する。電気抵抗測定器27は、プローブ25により検出された信号に基づいて、各チップ抵抗の抵抗値を測定する。加工条件設定部51は、チップ抵抗の抵抗値と目標値との間の誤差に基づいて、y方向のトリミングによりチップ抵抗の抵抗値を調整する比率である調整比率を設定する。トリミング制御部52は、設定された調整比率に従ってy方向およびx方向のトリミングを行い、チップ抵抗の抵抗値を調整するように制御する。本発明は、例えば、レーザ光を用いたトリミング装置に適用できる。

(もっと読む)

チップ抵抗器およびその製造方法

【課題】熱放散性に優れ、現状工程への適合性が高く、且つ信頼性に優れたチップ抵抗器を提供する。

【解決手段】絶縁性基板11と、その表面両端部に配置された一対の第1表電極12と、該第1表電極に接続する抵抗体15と、該抵抗体を被覆する第1保護膜16と、該第1保護膜上に前記第1表電極と一部が接続するように配置された第2表電極18と、前記抵抗体15と前記第1保護膜16に設けられた切り込み溝Xと、前記第2表電極17の一部と、前記第1保護膜16および前記切り込み溝Xを被覆する第2保護膜18とを備え、前記第1保護膜16と前記第2保護膜18の間に形成される第2表電極17は、前記切り込み溝Xを被覆せず、該切り込み溝Xにより狭くなった狭小部Yを覆うように形成する。

(もっと読む)

回路保護素子の製造方法

【課題】本発明は、高精度の抵抗値が得られる回路保護素子の製造方法を提供することを目的とするものである。

【解決手段】本発明の回路保護素子の製造方法は、絶縁基板11の上面の両端部に形成された一対の上面電極12と電気的に接続されるエレメント部13を形成する工程と、前記エレメント部13にレーザによって溶断部形成用トリミング溝16a〜16fおよび抵抗値調整用トリミング溝17a,17bを形成する工程と、前記エレメント部13を覆うように絶縁層15を形成する工程とを備え、前記抵抗値調整用トリミング溝17a,17bのうち少なくとも最後に形成する抵抗値調整用トリミング溝17bの形成時のレーザ出射繰り返し周波数を、前記溶断部形成用トリミング溝16a〜16fの形成時のレーザ出射繰り返し周波数より低くなるように設定したものである。

(もっと読む)

レジスタのレーザトリミング

【課題】基板層上に印刷されたレジスタをレーザトリミングするための改善されたシステム及び方法が提供される。

【解決手段】例示的な実施形態は、各々の環状レジスタに対する抵抗値を測定し、測定された抵抗値及び各々のレジスタに関連する目標抵抗値に基づいて、該環状レジスタを1つ又はそれ以上のビンの中に区分する。次いで、予測的なトリム設定に基づいて、レーザトリムファイルを各々のビンに割り当てることができ、各々のレーザトリムファイルは、レーザドリルに対する一連の設定パラメータを定めて、各々のレジスタがそれぞれの目標値に合致するようにする。レーザドリルは、ビンに割り当てられたレーザトリムファイルにしたがって、該レーザトリムファイルを用いて、各々のビン内のレジスタをトリムする。

(もっと読む)

抵抗器およびその製造方法

【課題】本発明は、薄膜技術による端面電極の形成が容易に、かつ確実に行えるとともに、端面電極と上面電極との電気的接続信頼性も確実なものが得られる抵抗器を提供することを目的とするものである。

【解決手段】本発明の抵抗器は、基板11と、この基板11の一方の主面側に形成され、かつ互いに電気的に接続される上面電極12,13,18および抵抗体14と、前記基板11の端面に設けられ、かつ前記上面電極12,13,18と電気的に接続される端面電極20とを備え、前記端面電極20を、基板11の他方の主面側から形成される金属薄膜よりなる第1の端面電極21と、基板11の一方の主面側から形成され、かつ第1の端面電極21と電気的に接続される金属薄膜よりなる第2の端面電極22とにより構成したものである。

(もっと読む)

チップ抵抗器の製造方法

【課題】 絶縁基板2の複数個を並べて一体化し,且つ,表面に縦ブレイク溝A1及び横ブレイク溝A2を刻設した素材基板Aを用意し,そのうち各絶縁基板の箇所に,左右一対の上面電極2を前記縦ブレイク溝に跨がるように形成するとともに抵抗膜3を形成し,前記両上面電極に通電用プローブBを接触した状態で前記抵抗膜の抵抗値を測定しながら,その抵抗値が所定値になるようにトリミング調節し,前記縦ブレイク溝に沿ってブレイクしたのち,各絶縁基板の左右両端面に側面電極6を形成し,更に,前記横ブレイク溝A2に沿ってブレイクする工程を備えて成るチップ抵抗器の製造方法において,前記トリミング調節を高い精度で容易にできるようにする。

【解決手段】 前記上面電極2を形成するとき,当該上面電極のうち前記縦ブレイク溝A1に重なる部分に抜き孔2aを形成する。

(もっと読む)

チップ抵抗器とのその製造方法

【課題】 チップ型にした絶縁基板2と,この絶縁基板の両端に形成した半田付け用の端子電極3,4と,前記絶縁基板の表面のうち前記両端子電極間の部分に並列に形成した複数個の抵抗膜5と,前記絶縁基板の表面に前記各抵抗膜を覆うように形成したカバーコート6とから成るチップ抵抗器において,その各抵抗膜5を略等しい抵抗値にする。

【解決手段】 前記両端子電極3,4のうち一方の端子電極3を,前記各抵抗膜ごとに独立して接続するように形成した個別上面電極8と,前記絶縁基板の一方の側面2aに形成した側面電極8とで構成し,他方の端子電極4を,前記各抵抗膜に対して共に接続するように形成した共通上面電極10と,前記絶縁基板の他方の側面2bに前記共通上面電極に接続するように形成した側面電極11とで構成する。

(もっと読む)

抵抗器の製造方法

【課題】めっき不良発生率の少ない微細な抵抗器を生産性を損なうことなく得ることができる抵抗器の製造方法を提供することを目的とするものである。

【解決手段】シート状の絶縁基板21の上面に形成された共通電極41に通電してスリット状の第1の分割部27の内側面に形成された側面電極層に電気めっき工法でめっき層を形成するようにしたもので、めっき不良発生率の少ない微細な抵抗器が生産性を損なうことなく得られるものである。

(もっと読む)

抵抗素子、それを内蔵した多層配線基板および抵抗素子の抵抗値調整方法

【課題】配線基板に内蔵する抵抗素子を形成する際に抵抗体の形成時に形成不良が発生するとトリミングの範囲を超えてしまい、抵抗値を調整することができなかった。

【解決手段】本発明では、第一の電極と第二の電極と両電極間を接続する抵抗体とを備え、抵抗体をトリミングすることで抵抗値の調整が可能な抵抗素子において、前記第一の電極は前記第二の電極に対して突出した突出部を有することを特徴とする抵抗素子とすることで、同じ基本形状の抵抗素子から大きな幅を持って抵抗値を調整することが可能となった。また、精度の高い加工が行える抵抗素子を得ることができた。

(もっと読む)

抵抗器へのレーザートリミングの間の熱電気ポテンシャルの解析方法

抵抗器(20)のレーザートリミングの間に起こる熱電効果は、電圧測定を行うことによって解決される。低出力でシミュレートされたトリム(10)の間に抵抗器(20)に与えられるレーザー加熱に起因する電圧は、抵抗器(20)上の相対的な熱の中立位置(18)を決定するのに用いられる。値に対するトリミング操作は、その後の同様な抵抗器(20)のすべてで行うことができる。また、電圧測定は、抵抗器測定値が比較される所望のトリム値をその抵抗測定値と相殺すべく使用される偏差情報を定めるために、トリミング作業の各パルスの前後で測定することができる。また、行または列の空間的に遠いあるいは隣接しない抵抗器(20)が、隣接するあるいは近くの抵抗器(20)上の抵抗価値を歪ませるかもしれない加熱効果を最小化するために、逐次トリミングを受ける。 (もっと読む)

電子部品の製造方法

セラミック基板(1)面に回路素子(3)が形成され、導電性ボール(2)を電子部品端子とする電子部品の製造法において、セラミック基板(1)と導電性ボール(2)との固着部分に過大な応力を集中させないことを課題とする。そのためには、表面に縦横に設けられた分割用溝(4)を有する大型のセラミック基板(1)面に回路素子3を形成する第1の工程と、前記分割用溝(4)を開くように上記基板(1)に応力付与することで上記基板(1)を単位電子部品小片(10)に分割する第2の工程と、分割後の単位電子部品小片(10)の回路素子(3)端子部(7)に導電性ボール(2)を固着させる第3の工程とを有し、上記第1、第2及び第3の工程をこの順に実施する。このとき、複数の単位電子部品小片(10)を容器(11)を用いて並べる工程を第2の工程終了後、第3の工程開始前に実施することが好ましい。 (もっと読む)

1 - 13 / 13

[ Back to top ]