Fターム[5E034DC06]の内容

サーミスタ、バリスタ (5,260) | 電極端子(PTC、NTC、バリスタ) (667) | 電極材料 (51) | ガラスフリットを有するAg電極 (9)

Fターム[5E034DC06]の下位に属するFターム

BiO2−SiO2−B2O3系 (1)

BiO2−B2O3−Ag2O系

Fターム[5E034DC06]に分類される特許

1 - 8 / 8

チップ部品およびその製造方法

【課題】大型でも、高性能で高品質で、実装状態で高い信頼性を確保することのできるチップ部品を提供する。

【解決手段】誘電体素子11と、該誘電体素子の内部に設けた内部電極11aと、該内部電極と電気的に接続した外部電極層15とを備え、誘電体素子11と外部電極層15の間に誘電体素子11の全面を覆うガラス層12を有し、外部電極層15は、金属成分を含む下地電極13と、樹脂電極14とからなり、樹脂電極14は、下地電極13を覆い、かつ誘電体素子11にガラス層12を介して接合する。ガラス層12は、結晶化ガラスからなることが好ましい。

(もっと読む)

セラミック電子部品

【課題】内部電極と外部電極との接合強度を高めると共に、緻密な外部電極を得るセラミック電子部品を提供する。

【解決手段】本発明のセラミック電子部品は、セラミック素体と、前記セラミック素体の内部に設けられ、少なくともPdを含む内部電極と、前記セラミック素体の端面に設けられ、金属成分として少なくともCuとAgとを含むと共に、ガラス成分として結晶化ガラスを一種類以上含み、前記内部電極と導通する一対の外部電極とを有し、前記外部電極は、軟化点Tsが焼付温度よりも高い結晶化ガラスを50%以上含有する。

(もっと読む)

チップ型電子部品の製造方法

【課題】素子本体とメディアとを分離する作業が不要であり、素子本体の端面に形成してある下地電極層の表面にメッキ膜を確実に形成することが可能であり、しかも素子本体の表面にダメージを与えるおそれが少ないチップ型電子部品の製造方法を提供すること。

【解決手段】内部電極4,6が内部に形成された素子本体10と、内部電極4,6が露出する素子本体10の端面を覆う端子電極12,14とを有するチップ型電子部品2を製造する方法である。素子本体10の端面に下地電極層12p,14pを形成する。下地電極層12p,14pがそれぞれ形成された複数の素子本体10を、凹状容器20aの内部に収容する。凹状容器20aの内部に液体を入れた状態で、凹状容器20aを第1回転速度で回転させ、素子本体10を、凹状容器の底面20aで内側壁面近くに移動させる。凹状容器20aを第1回転速度よりも高速な第2回転速度で回転させ、素子本体10を内側壁面23aに沿って上方に移動させる。凹状容器20aの回転を停止させる。

(もっと読む)

バリスタ及びその製造方法

【課題】バリスタ電極の焼付け温度の変化によるバリスタ電圧の変化を抑制すること、バリスタ電極の接着性を向上させることが要求されている。

【解決手段】本発明のバリスタは、バリスタ特性を有する半導体磁器11と、該半導体磁器11の表面上に配置された電極15とから成る。電極15は、銀粉末と亜鉛粉末とアルミニウム粉末とガラスフリットとを含有する第1電極材料で形成された第1導電体層12’と、第1導電体層の上に配置され且つ銀粉末とガラスフリットとを含有する第2電極材料で形成された第2導電体層14とから成る。

(もっと読む)

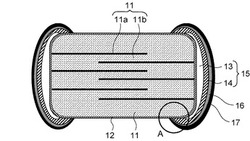

積層チップバリスタ

【課題】耐湿性・耐メッキ性を改善し、サージ耐量およびエネルギー耐量も向上させた積層チップバリスタを提供する。

【解決手段】酸化亜鉛を主成分とする積層チップバリスタにおいて、その外部電極材のガラス組成としてホウケイ酸亜鉛系ガラス(ZnO−SiO2−B2O3−BaO)と、0.5〜6.0μmの球状Ag粒子とを含んでなる。より具体的には、外部電極材は、ホウケイ酸亜鉛系ガラスを5〜20重量%、球状Ag粒子を80〜95重量%含んで構成される。

(もっと読む)

回路保護素子及びその製造方法

本発明は回路保護素子及びその製造方法に関する。本発明による回路保護素子は、コイルパターン、内部電極、導電性物質が埋め込まれた孔及び磁性体物質が埋め込まれた孔が選択的に形成された複数のシートを有する共通モードノイズフィルターと、内部電極及びESD保護物質が埋め込まれた孔が選択的に形成された複数のシートを有するESD保護素子と、を備える。本発明によれば、ソレノイド型の共通モードノイズフィルターとESD保護素子を単一の素子として積層形成し、これを用いて電子機器の共通モードノイズとESDを同時に抑制することができる。このため、共通モードノイズとESDを保護するために個別素子を使用していた従来に比べて構成が簡素化されることから、電子機器のサイズ増加を防止することができ、入出力信号の歪みを防止することができて電子機器の信頼性を向上させることができる。 (もっと読む)

積層バリスタ

【課題】小型化及び低電圧駆動に対応でき、特性のばらつきが少なく、安価に提供でき、しかもESD耐性及び高温負荷時の信頼性を効果的に高め得る積層バリスタを提供する。

【解決手段】半導体セラミック材料からなるセラミック層2間の所定の界面に沿って複数の内部電極3a,3bが配置されているセラミック素体4と、セラミック素体4の両端面に引き出された所定の内部電極と電気的に接続される外部電極とを備える積層バリスタ1であって、セラミック層2はZnOを主成分とし、副成分として、Prを全体の0.1〜5.0原子%、Coを1.0〜5.0原子%、Al、Ga、及びInの内少なくとも1種を総量で0.002〜0.2原子%、Ca、Sr及びBaの内少なくとも1種を総量で0.005〜0.5原子%、Zrを0.01〜0.2原子%含み、かつ、内部電極3a,3bがAg及びPdを含むことを特徴とする、積層バリスタ1。

(もっと読む)

サーミスタの製造方法

【課題】 チタン酸バリウム系半導体の焼成中にアルカリ金属が蒸発又は移動する現象を抑圧して、抵抗値や温度特性等を安定させることができるサーミスタの製造方法を提供する。

【解決手段】 このサーミスタの製造方法は、チタン酸バリウム系半導体を用いるサーミスタの製造方法であって、主原料として、バリウムとチタンと酸素とを含む材料、又は、バリウムと酸素とを含む材料及びチタンと酸素とを含む材料と、副原料として、少なくとも1価のアルカリ金属とチタンとが化学的に結びついている酸化物を含む少なくとも1つの材料とを、ドーパントとなる原料と共に混合する工程(a)と、工程(a)において混合された原料にバインダーを混合して成型する工程(b)と、成型された原料を焼成することにより、チタン酸バリウム系半導体を生成する工程(c)とを具備する。

(もっと読む)

1 - 8 / 8

[ Back to top ]