Fターム[5E082CC08]の内容

固定コンデンサ及びコンデンサ製造装置 (37,594) | 複合コンデンサ (1,118) | 固定コンデンサのみの組合せ (781) | 多連型貫通型コンデンサ (11)

Fターム[5E082CC08]の下位に属するFターム

2連型のもの (3)

Fターム[5E082CC08]に分類される特許

1 - 8 / 8

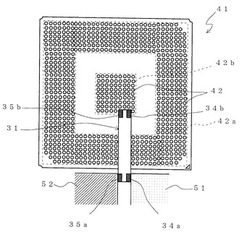

積層セラミックコンデンサおよびこれを用いたジャンパ実装構造

【課題】 従来の積層セラミックコンデンサを用いると、両面回路基板の表面に実装された、電源およびグランド接続端子が信号線接続端子よりも内側に配置された負荷ICへ、両面回路基板の裏面において電源配線をジャンパ接続することができない。

【解決手段】 積層セラミックコンデンサ31の胴体部分の長さが、負荷IC41の信号線接続端子群42aにつながる基板裏面に形成された信号線配線パターンの形成領域を跨ぐ長さに単に設定されることで、胴体部分が信号線配線パターンに電気接触することなく、長手方向両側の一方の外部電極34a,34bが、基板裏面の電源配線パターン51と、負荷IC41の電源接続端子42につながるビアホールとに接続される。また、長手方向両側の他方の外部電極35a,35bが、基板裏面のグランド配線パターン52と、負荷IC41のグランド接続端子42につながるビアホールとに接続される。

(もっと読む)

電子部品の実装構造

【課題】低周波帯域において低インピーダンスを保ちつつ、高周波帯域において高インピーダンスとすることができる電子部品の実装構造を提供する。

【解決手段】電源に電流を供給するための電源ライン1,2に接続される電子部品の実装構造であって、電子部品として、コンデンサ10,11とフェライトビーズインダクタ12,13とを備え、電源ライン1,2の間に各コンデンサ10,11と各フェライトビーズインダクタ12,13とが直列となるように接続されており、各フェライトビーズインダクタ12,13は、互いの磁界が相殺されるように実装されている。

(もっと読む)

積層型貫通コンデンサ及び積層型貫通コンデンサの実装構造

【課題】回路基板に搭載した場合における配線密度の低下を抑制でき、且つESLの十分な低下を図ることが可能な積層型貫通コンデンサ及び積層型貫通コンデンサの実装構造を提供すること。

【解決手段】第1信号用端子電極11と信号用内部電極20とは第1スルーホール導体22を介して接続され、第2信号用端子電極12と信号用内部電極20とは第2スルーホール導体23を介して接続されている。第1接地用端子電極13と接地用内部電極24とは、第3スルーホール導体25を介して接続されている。第1信号用端子電極11と第1接地用端子電極13とは、互いに近接して第1領域6a,7aに配置されている。第2信号用端子電極12は、第2領域6b,7bに配置されている。コンデンサ素体1の長手方向での第1領域6a,7aと第2領域6b,7bとの間の第3領域6c,7cには、いかなる導体も配置されていない。

(もっと読む)

蓄放電装置の低内部抵抗の接続構造

【課題】 大電流が流れても電極板の電流密度が不均一にならず、蓄放電装置の性能劣化をもたらす恐れのない蓄放電装置の低内部抵抗接続構造を得る。

【解決手段】 互いに極性の異なる同一形状の、異なる軸方向における異なるサイド幅を有する楕円形、或いは多角形の電極板を隔離体を挟んで、且つ互いに所定角度だけ回転させた状態で層状に順次配置するとともに、層方向視において同一極性の電極板はその全てが重なる一方、他極性の電極板に対しては重ならない共通の辺部または頂部を有するように前記層状に順次配置した蓄放電装置の低内部抵抗の接続構造において、前記同一極性の、他極性の電極板に対して重ならない辺部または頂部に導電端子を設け、同一極性の電極板同士を並列接続して、電流の出入力端子を形成する。

(もっと読む)

貫通型積層コンデンサ

【課題】複数の静電容量成分を並列接続する回路を実現することが可能な貫通型積層コンデンサを提供すること。

【解決手段】第1の信号用内部電極20は、第1の信号用端子電極及び信号用接続導体に接続されている。第2の信号用内部電極24は、第2の信号用端子電極及び信号用接続導体に接続されている。第1の接地用内部電極30は、第1の接地用端子電極及び接地用接続導体に接続されている。第2の接地用内部電極34は、第2の接地用端子電極及び接地用接続導体に接続されている。第1の信号用内部電極20と第1の接地用内部電極30とは互いに対向する領域を有し、第2の信号用内部電極34と第2の接地用内部電極34とは互いに対向する領域を有する。第1の信号用内部電極20と第2の接地用内部電極34とは互いに対向せず、第2の信号用内部電極24と第1の接地用内部電極30とは互いに対向しない。

(もっと読む)

多連チップ部品および多連チップ実装基板

【課題】本特性の変化やリークの原因となるようなクラックの発生を抑制し、また多連コンデンサに生じる応力を低減し、コンデンサの静電容量の変動を低減することのできる多連チップ部品を提供する。

【解決手段】複数のセラミック層と複数の内部電極とが積層された素子と該素子に電気的に接続された外部電極とからなるユニットがセラミック焼結体に複数併設され、前記外部電極で表面実装される多連チップ部品であって、前記ユニットの間に前記セラミック層のない空隙部が表面実装される面に略垂直に形成されていることを特徴とする多連チップ部品である。

(もっと読む)

キャパシタ部品

【課題】 広い範囲の高周波域(GHz帯)でインピーダンスが低減されて、半導体素子のさらなる高周波化に対応するデカップリングキャパシタに適用できるキャパシタ部品を提供する。

【解決手段】 基板10上に、下部電極12、誘電体層14及び上部電極16によりそれぞれ構成される複数のキャパシタ素子C1〜C3が並んで配置され、複数のキャパシタ素子C1〜C3の各下部電極12は、共通電極となる下部電極用再配線層22にそれぞれ接続され、各上部電極16は共通電極となる上部電極用再配線層26にそれぞれ接続されており、複数のキャパシタ素子C1〜C3がキャパシタ部品の状態で電気的に並列に接続されている。複数のキャパシタ素子C1〜C3の間でインピーダンスを変えることで、広い範囲の高周波域でインピーダンスが低減される。

(もっと読む)

インバーテッドマイクロストリップ伝送線路

【課題】 線路間の結合を小さくして回路の面積を小型化できるインバーテッドマイクロストリップ伝送線路を提供する。

【解決手段】 誘電体基板11上に帯状のストリップ電極12を形成し、ストリップ電極12の上および両側面を覆うように誘電体層13を形成し、この誘電体層13上および側面さらに誘電体層13の形成されていない誘電体基板11上を覆うようにグランド電極14を形成し、ストリップ電極12からの電磁界をグランド電極14によって閉じ込め、線路間の結合を小さくする。

(もっと読む)

1 - 8 / 8

[ Back to top ]