Fターム[5E082EE39]の内容

固定コンデンサ及びコンデンサ製造装置 (37,594) | 容量形成電極 (6,310) | 容量形成電極の製造・形成手段 (1,600) | メッキ (81)

Fターム[5E082EE39]に分類される特許

81 - 81 / 81

マイクロストリップ線路、その製造方法、インダクタ素子及び高周波半導体装置

【課題】 マイクロストリップ線路の線路幅の狭小化を行なったとしても、導体損失が増加しないようにする。

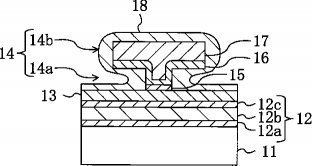

【解決手段】 半絶縁性GaAsからなる基板11上には、接地電極12と、厚さが約0.5μmのチタン酸ストロンチウムからなる誘電体層13と、線状導体層14とにより構成されるマイクロストリップ線路が形成されている。線状導体層14は、幅が約0.5μmの狭小部14aと、幅が約5μmの幅広部14bとにより構成されている。この線状導体層14は、異なる材料からなる積層体であって、基板11側から順次形成された、厚さが約0.1μmの窒化タングステンシリコンからなる第1層15と、厚さが約0.05μmのTiと厚さが約0.5μmのAuとの積層体からなる第2層16と、厚さが約3μmのAuからなる第3層17とから構成されている。

(もっと読む)

81 - 81 / 81

[ Back to top ]