Fターム[5E082JJ05]の内容

固定コンデンサ及びコンデンサ製造装置 (37,594) | 構成要素間の接続部 (1,230) | 接続部の形状、構造 (605) | 容量形成電極相互の接続部又は端子引出部 (431) | 多層・多重構造のもの (13)

Fターム[5E082JJ05]に分類される特許

1 - 13 / 13

チップ型電子部品

【課題】はんだ喰われを防止しつつ、応力緩和が可能な端子電極を有するチップ型電子部品を提供すること。

【解決手段】チップ型電子部品Cは、セラミック素体Lと、セラミック素体Lの内部に配置され、かつ、セラミック素体Lの表面に一部が露出した内部電極20と、セラミック素体の表面に配置された端子電極10とを含み、端子電極10は、第1の導電性材料12a、12bを含むとともに、内部電極の露出した部分および内部電極が露出しているセラミック素体の表面を覆う第1の電極層12と、第1の電極層12よりもセラミック素体の表面から離れた位置に配置される導電性めっき層14と、はんだ成分を含む第2の導電性材料16aと樹脂16cとを含むとともに、導電性めっき層14よりもセラミック素体の表面から離れた位置に配置される第2の電極層16と、を含む。

(もっと読む)

電子部品の製造方法及び電子部品

【課題】製品寸法の増大を抑制しつつ、電子部品の実装不良を防止できる電子部品の製造方法及び電子部品を提供する。

【解決手段】電子部品1の製造方法では、表面に凹凸形状を有する平板20を準備する平板準備工程S2と、第一導電性ペーストP1を平板20の表面の凹部21に入り込むように付与するペースト付与工程S3と、凹部21に付与された第一導電性ペーストP1に素体2の端面2a,2b側を押し当てて導電性ペーストPを付与して第一ペースト層16を形成する第一ペースト層形成工程S5と、素体2の主面2c,2dの端面2a,2b側にスクリーン印刷によって第二導電性ペーストP2を付与して第二ペースト層17を形成する第二ペースト層形成工程S7とを有する。

(もっと読む)

コンデンサ及びその製造方法

【課題】挿入損失の小さなコンデンサ及びその製造方法を提供する。

【解決手段】コンデンサ1は、誘電体からなるコンデンサ本体10と、第1の内部電極と、第2の内部電極12と、第1及び第2の信号端子15,16と、接地端子17,18とを備えている。第1及び第2の信号端子15,16は、第1の内部電極に接続されている。接地端子17,18は、コンデンサ本体10の外表面上に、第2の内部電極12に接続されるように形成されている。接地端子17,18は、グラウンド電位に接続される。接地端子17,18は、コンデンサ本体10上に、第2の内部電極12に接続されるように形成されているめっき膜17a,18aを有する。

(もっと読む)

配線基板内蔵用電子部品及び配線基板

【課題】外部電極の表面に形成される銅めっき層の表面粗化を適切に行うことができ、配線基板の樹脂絶縁層との密着性を十分に確保することができる配線基板内蔵用電子部品を提供する。

【解決手段】セラミックコンデンサのセラミック焼結体104は、コンデンサ主面102及びコンデンサ裏面を有する。セラミック焼結体104におけるコンデンサ主面102上及びコンデンサ裏面上には、メタライズ金属層151の表面に銅めっき層152を形成してなる複数のプレーン状電極111,112が配置されている。銅めっき層152を構成する銅粒子の最大粒径は1μm以下であり、かつメタライズ金属層151を構成するニッケル粒子の1つに対し、銅粒子が2つ以上接している。

(もっと読む)

セラミック多層デバイスとその製造方法

【課題】本発明は、セラミック多層デバイスの電子デバイスレベルにおける誘電率の温度特性向上と機械的強度向上とを同時に満たすことが課題であった。

【解決手段】セラミック誘電体層1の材料として希土類及び酸化チタンの少なくとも一方を用いることでセラミック誘電体層1の誘電率の温度特性を向上させ、またセラミック誘電体層の主表面部4に圧縮応力を導入することで機械的強度を向上させているので、機械的強度向上と誘電率の温度特性向上の2つを同時に満たすことが可能となる。

(もっと読む)

酸化物誘電体膜の形成方法

【課題】 密着性の高い酸化物誘電体膜を金属箔上に形成する。

【解決手段】 不純物を含む金属箔12を雰囲気中に配置する。この雰囲気の温度を所定の加熱温度まで上昇させ、次いで、雰囲気の温度を所定の時間にわたって当該加熱温度に維持する。これにより、金属箔12を酸化することなく不純物を酸化する。この後、金属箔12上に酸化物誘電体膜14を直接形成する。

(もっと読む)

積層型セラミック電子部品およびその製造方法

【課題】複数のセラミック層からなる積層構造を有する積層体と、特定のセラミック層を厚み方向に貫通するように設けられるビア導体とを備える積層型セラミック電子部品において、焼成時の寸法変化度合いの違いに起因する、ビア導体とセラミック層との間の隙間を生じにくくするため、ビア導体の形成に用いる導電性ペーストにセラミック粉末を含有させると、ビア導体の電気抵抗が増す。

【解決手段】セラミック粉末を含有する第1の導電性ペースト3と、第1の導電性ペースト3より少ないセラミック粉末を含有するかセラミック粉末を含有しない第2の導電性ペースト5とを用意し、内周面に沿って第1の導電性ペースト3を付着させたビアホール2に、第2の導電性ペースト5を充填する。焼結後のビア導体6では、セラミック粉末は外周部7から中心部8に向かって減少するような濃度勾配をもって存在するため、中心部8での電気抵抗を低くできる。

(もっと読む)

配線基板内蔵用コンデンサの製造方法、配線基板内蔵用コンデンサ、及び配線基板

【課題】配線基板に内蔵させた場合における導通不良を低減させることができる配線基板内蔵用コンデンサの製造方法、配線基板内蔵用コンデンサ、及びこれを備えた配線基板を提供する。

【解決手段】複数のセラミック層、及びセラミック層間に配置された複数の内部電極層とを有するコンデンサ本体部と、セラミック材料から構成されたコンデンサ端部とを備えるコンデンサの製造方法であって、セラミックグリーンシート25,28の表面にかつコンデンサ本体部となる領域に、内部電極パターン23,26を形成する工程と、セラミックグリーンシート22の表面にかつコンデンサ端部に、コンデンサ端部の一部となるセラミックパターン21を形成する工程とを備えるコンデンサの製造方法が提供される。

(もっと読む)

多層構造を持つ埋め込みキャパシタコア

【課題】ICと外部キャパシタとの間に長い配線経路を持つ。

【解決手段】

埋め込みキャパシタコアは、第1の組みのキャパシタ、第2の組みのキャパシタ、および第1の組みのキャパシタと第2の組みのキャパシタとの間の中間層誘電性フィルムを含む。第1の組みのキャパシタは、少なくとも2つの導電性電極を備える第1の導電性パターンと、第1の導電性パターンの2つの電極に対応する少なくとも2つの導電性電極を備える第2の導電性パターンと、および第1、第2の導電性パターンの間の第1の誘電性フィルムとを含む。第2の組みのキャパシタは、少なくとも2つの導電性電極を備える第3の導電性パターンと、第3の導電性パターンの2つの電極に対応する少なくとも2つの導電性電極を備える第4の導電性パターンと、および第3、第4の導電性パターンの間の第2の誘電性フィルムとを含む。

(もっと読む)

低ロスの薄膜コンデンサおよびその製造方法

【課題】コンデンサ構造の動作周波数帯域におけるロスを好適に改善するコンデンサを提供する。

【解決手段】本明細書に記載する教示に基づき、低ロスの薄膜コンデンサが提供される。低ロスの薄膜コンデンサ構造は、第1の電極および第2の電極(10)、ならびに第1の電極と第2の電極との間の極性誘電体(12)とを含み得る。極誘電体と第1の電極および第2の電極とは、共同で、動作周波数帯域を有するコンデンサを形成する。コンデンサ構造は、薄膜コンデンサ構造の音響特性に影響する1つ以上の層(14、30)をも含み得、その結果、動作周波数帯域外の周波数におけるRFエネルギーをコンデンサが吸収する。

(もっと読む)

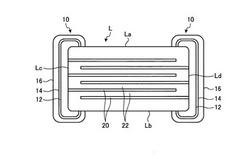

セラミック電子部品

【課題】 コストの低減を可能にするとともに、熱衝撃によるクラックの発生を防止しつつ、電気抵抗の増大を抑制することができるセラミック電子部品を提供することを目的とする。

【解決手段】 積層コンデンサC1は、セラミック焼結体10と、セラミック焼結体10内に形成された内部電極20と、外部電極30とを備える。外部電極30は、第1の電極層40と第2の電極層42と導電性樹脂層44と第3の電極層46と第4の電極層48とを有する。内部電極20及び第1の電極層40は、卑金属を主成分として含む。第2の電極層42は貴金属を主成分として含む。導電性樹脂電極層44は貴金属を含む。第3の電極層46はNiを主成分として含む。第4の電極層48はSn又はSn合金を主成分として含む。

(もっと読む)

積層コンデンサ、及び、積層コンデンサの等価直列抵抗調整方法

【課題】 等価直列抵抗の制御を容易に且つ精度良く行うことが可能な積層コンデンサ、及び、積層コンデンサの等価直列抵抗調整方法を提供すること。

【解決手段】 積層体1は、複数の誘電体層11〜35と、複数の第1及び第1の内部電極51〜62,71〜82とが交互に積層されることにより構成される。第1の内部電極51〜62は、スルーホール導体131a〜153a及び内部導体111〜122を介して互いに電気的に接続される。第1の内部電極51〜54は、引き出し導体171〜174を介して第1の端子電極に電気的に接続される。第2の内部電極71〜82は、スルーホール導体131b〜153b及び内部導体91〜102を介して互いに電気的に接続される。第2の内部電極71〜74は、引き出し導体181〜184を介して第2の端子電極に電気的に接続される。

(もっと読む)

プリント配線板及びプリント配線板の製造方法

【課題】 コンデンサを内蔵し、接続信頼性を高めたプリント配線板及びプリント配線板の製造方法を提供することにある。

【解決手段】 コア基板30にチップコンデンサ20を内蔵させ、チップコンデンサ20上に、チップコンデンサ20の端子21,22と接続する相対的に大きなビア52を形成し、コア基板30の上面の層間樹脂絶縁層60に、ビア52へ接続された複数個の相対的に小さなビア69を配設する。これにより、コンデンサ20の配設位置ずれに対応して、コンデンサ20の端子21、22とビア52とを確実に接続することが可能となる。

(もっと読む)

1 - 13 / 13

[ Back to top ]