Fターム[5F003BA23]の内容

バイポーラトランジスタ (11,930) | 素子構造 (1,262) | 集積回路用 (671) | 素子分離 (611)

Fターム[5F003BA23]の下位に属するFターム

Fターム[5F003BA23]に分類される特許

1 - 20 / 101

半導体装置

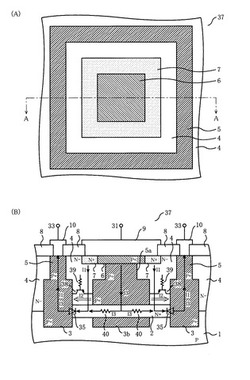

【課題】所望のブレークダウン電圧を確保し、大きな放電電流を流せるESD保護特性の良好なESD保護素子を実現する。

【解決手段】適切な不純物濃度のN+型埋め込み層2とP+型埋め込み層3で形成するPN接合ダイオード35と、P型拡散層6と接続するP+型埋め込み層3aをエミッタ、N−型エピタキシャル層4をベース、P+型埋め込み層3をコレクタとする寄生PNPバイポーラトランジスタ38とでESD保護素子を構築する。P+型埋め込み層3はアノード電極10に接続され、P+型拡散層6と、それを取り囲むN+型拡散層7はカソード電極9に接続される。カソード電極9に正の大きな静電気が印加されるとPN接合ダイオード35がブレークダウンし、その放電電流I1によりP+型埋め込み層3よりN−型エピタキシャル層4の電位が下がり寄生PNPバイポーラトランジスタ38がオンし大きな放電電流I2が流れる。

(もっと読む)

半導体装置

【課題】所望のブレークダウン電圧を確保し、大きな放電電流を流せるESD保護特性の良好なESD保護素子を実現する。

【解決手段】適切な不純物濃度のN+型埋め込み層2とP+型埋め込み層3からなるPN接合ダイオード35と、P+型拡散層6と繋がるP+型引き出し層5aをエミッタ、N−型エピタキシャル層4をベース、P型半導体基板1をコレクタとする寄生PNPバイポーラトランジスタ38とでESD保護素子を構成する。P+型埋め込み層3はアノード電極10に接続され、P+型拡散層6と、それと接続され、取り囲むN+型拡散層7とはカソード電極9に接続される。カソード電極9に正の大きな静電気が印加されるとPN接合ダイオード35がブレークダウンし、そのときの放電電流I1によりP+型引き出し層5aよりN−型エピタキシャル層4の電位が下がり寄生PNPバイポーラトランジスタ38がオンし、大きな放電電流I2が流れる。

(もっと読む)

半導体装置

【課題】所望のブレークダウン電圧が確保でき、大きな放電電流を流すことが可能なESD保護特性のすぐれたESD保護素子を実現する。

【解決手段】適切な不純物濃度のN+型埋め込み層2とP+型埋め込み層3でPN接合ダイオード35を形成する。P+型埋め込み層3はP+型引き出し層5と一体となりN−型エピタキシャル層4を貫通させアノード電極10と接続される。P+型埋め込み層3等で囲まれたN−型エピタキシャル層4にN+型拡散層7と該N+型拡散層7と接続され、これを取り囲むP+型拡散層6を形成する。N+型拡散層7、P+型拡散層6はカソード電極9に接続される。P+型拡散層6をエミッタ、N−型エピタキシャル層4をベース、P+型引き出し層5等をコレクタとする寄生PNPバイポーラトランジスタ38とPN接合ダイオード35でESD保護素子を構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】高周波帯域で動作する半導体装置の特性の低下を抑制しつつ、製造コストを低減できる半導体装置及びその製造方法を提供する。

【解決手段】本発明に係る半導体装置100は、電界効果型トランジスタと、ヘテロ接合バイポーラトランジスタと、ヘテロ接合バイポーラトランジスタのGaAsベース層7を用いて形成されたベースエピ抵抗素子28と、電界効果型トランジスタのInGaAsチャネル層4を用いて形成された配線部26と、配線部26とベースエピ抵抗素子28とを絶縁する高抵抗化領域27と、配線部26の水平方向の周囲を囲う絶縁性の素子分離領域24とを含む。また、ベースエピ抵抗素子28は、半絶縁性GaAs基板1の主面に垂直な方向から見て、配線部26と交差しているベースエピ抵抗素子領域29を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】電力増幅モジュールの放熱特性を向上させる。

【解決手段】電力増幅モジュールに用いられる電力増幅回路用のLDMOSFET素子が形成された半導体チップにおいて、LDMOSFET素子用の複数のソース領域、複数のドレイン領域および複数のゲート電極39が形成されたLDMOSFET形成領域上に、ソース用バンプ電極BPSを配置する。ソース用バンプ電極BPSは、アルミニウムを主体とするソース用パッドM3S上に、ソース用パッドM3Sよりも厚くかつ銅を主体とするソース用導体層CNDSを介して形成する。ソース用バンプ電極BPSとソース用導体層CNDSの間には樹脂膜は介在していない。

(もっと読む)

半導体装置およびその製造方法

【課題】線形性に優れた半導体抵抗素子を提供する。

【解決手段】本発明の半導体装置は、GaAs基板101上に形成され、3−5族化合物半導体から構成されるHBT130と、GaAs基板101上に形成され、HBT130を構成する半導体エピタキシャル層の少なくとも1層から構成される半導体抵抗素子120とを備え、半導体抵抗素子120は、ヘリウム不純物を含む。

(もっと読む)

ヘテロ接合バイポーラトランジスタ及びその製造方法

【課題】耐破壊性に優れたヘテロ接合バイポーラトランジスタを提供する。

【解決手段】サブコレクタ層と、第1コレクタ層、第2コレクタ層、第3コレクタ層及び第4コレクタ層を有しサブコレクタ層上に形成されたコレクタ層と、コレクタ層上に形成されたベース層と、ベース層上に形成され、ベース層を構成する半導体よりも大きなバンドギャップを有する半導体から構成されるエミッタ層とを備え、第1コレクタ層は、第2コレクタ層、第3コレクタ層及び第4コレクタ層を構成する半導体と異なる半導体から構成されてサブコレクタ層上に形成され、第4コレクタ層は、第2コレクタ層の不純物濃度よりも低い不純物濃度で第1コレクタ層上に形成され、第2コレクタ層は、サブコレクタ層の不純物濃度よりも低く第3コレクタ層の不純物濃度よりも高い不純物濃度で第4コレクタ層上に形成され、第3コレクタ層は、第2コレクタ層とベース層との間に形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の特性を向上できると共に、製造コストを低減できる。

【解決手段】本発明の例に関わる半導体装置は、半導体基板1上に順次積層されたコレクタ層2A、ベース層3A及びエミッタ層4Aと、コレクタ層2Aの側面上に設けられ、コレクタ層に対して歪み応力を与える第1ストレスソース膜15Aと、ベース層3Aの側面上に設けられ、ベース層3Aに対して歪み応力を与える第2ストレスソース膜17と、を具備し、第1ストレスソース膜15A上端及び前記ベース層上端は、半導体基板表面から同じ高さに位置し、第2ストレスソース膜17は、ベース層3Aの側面と第1ストレスソース膜15Aの側面との間に設けられる。

(もっと読む)

新構造半導体集積回路

【課題】現在、半導体集積回路で使用されているバイポーラトランジスタとMOSトランジスタは最初に発明された時よりその構造は変わっておりません。構造と原理を根本的に見直し、高速化・低消費電力化・微細化を進展させる。

【解決手段】サブミクロンスケールの微細加工技術を用い、新しい原理と構造のトランジスタによる半導体集積回路を形成する。

(もっと読む)

半導体装置

【課題】耐圧の異なるトランジスタを容易に形成することができる半導体装置を提供すること。

【解決手段】本発明にかかる半導体装置は、ボディシリコン層23、低耐圧のトランジスタ40、及び高耐圧のトランジスタ30を有する。トランジスタ40では、高濃度コレクタ領域42及びベース領域43が、半導体層23に設けられた低濃度コレクタ領域41に接する。また、トランジスタ30では、ボディシリコン層23に設けられた低濃度コレクタ領域31に接する、高濃度コレクタ領域32及びベース領域33において、ボディシリコン層23の主表面に対して平行方向の距離が、高濃度コレクタ領域32及びベース領域33よりも離れて設けられている。

(もっと読む)

n型ベースを有するバイポーラトランジスタ及びその製造方法

【解決手段】ベースコンタクト接続部(12)、エミッタ部(4、5)及びコレクタ部がn層(3)上に配置され、当該n層は、更なるnpnバイポーラトランジスタために用いることができる。当該コレクタ部はエミッタ部に対して側方に配置され、当該エミッタ部及びコレクタ部の少なくとも一方は、当該n層の表面領域上でショットキーコンタクト(14)を備える。 (もっと読む)

バイポーラトランジスタの製造方法及びバイポーラトランジスタ

【課題】バイポーラトランジスタの高周波特性を向上させる。

【解決手段】ヘテロバイポーラトランジスタ70は、ベースとエミッタ、ベースとコレクタがヘテロ接合を有し、双条ベース構造を有する。N型エピタキシャル層3上の内部ベース層(P型SiGe層)5と接する外部ベース層10、及び内部ベース層(P型SiGe層)5上には、絶縁膜7及びN型多結晶シリコン膜8が積層形成される。積層形成された絶縁膜7及びN型多結晶シリコン膜8の中央部にはエミッタ開口部19が設けられる。エミッタ開口部19にはN型エピタキシャル層11が設けられる。N型エピタキシャル層11及びN型多結晶シリコン膜8上には、エミッタ開口部19を覆うようにT型形状を有するN型多結晶シリコン膜12が設けられる。左右のN型多結晶シリコン膜8及びエミッタ開口領域は同時に形成され、左右のN型多結晶シリコン膜8の幅は同一に設定される。

(もっと読む)

ポリエミッタ型バイポーラトランジスタ、BCD素子、ポリエミッタ型バイポーラトランジスタの製造方法及びBCD素子の製造方法

【課題】複合高電圧素子工程を用いたポリエミッタ型バイポーラトランジスタ及びその製造方法、BCD(複合高圧)素子及びその製造方法を提供する。

【解決手段】実施の形態に係るポリエミッタ型バイポーラトランジスタは、半導体基板100の上側の一部に形成された埋込層110と、上記半導体基板の上に形成されたエピ層120と、上記エピ層に形成され、上記埋込層と連結されるコレクタ領域130と、上記エピ層の上側の一部に形成されたベース領域140と、上記ベース領域の基板の表面に形成され、ポリシリコン材質からなるポリエミッタ領域170と、を含む。実施の形態に係るBCD素子は、ポリシリコン材質からなるポリエミッタ領域を含むポリエミッタ型バイポーラトランジスタを含み、上記バイポーラトランジスタと同一な単一ウエハ上に形成されたCMOSとDMOSのうちの1つ以上のMOSを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】同一基板上に形成された縦型PNPトランジスタとNPNトランジスタの両方の特性向上が図られた半導体装置を提供する。

【解決手段】半導体装置はPNPトランジスタ50を備えている。PNPトランジスタ50は、第1のP型コレクタ領域3bと、第1のP型コレクタ領域3bの底面を覆い、第1のP型コレクタ領域3bの不純物濃度のピークよりも深い位置に不純物濃度のピークを有する第1のN型埋め込み領域2と、第1のP型コレクタ領域3b上に形成された第2のP型コレクタ領域5bとを備えている。第1のP型コレクタ領域3bの側面もN型領域に囲まれている。このため、PNPトランジスタ50におけるパンチスルーの発生が抑えられるとともに、コレクタ領域内のキャリア通過経路を短くしてコレクタ抵抗の低減を図ることができる。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】半導体集積回路装置の設計工数を低減する。

【解決手段】SOI基板1の半導体層において、互いに完全に電気的に分離された複数の単位バイポーラトランジスタQuを並列接続することにより、大電流容量を必要とするバイポーラトランジスタを構成する。また、所望の電流容量を与えるトランジスタは、幾何学的寸法が、実質的に同一サイズである複数の単位バイポーラトランジスタを、互いに電気的に並列接続することにより構成する。

(もっと読む)

半導体基板、半導体基板の製造方法および電子デバイス

【課題】安価な、また、放熱特性に優れたSi基板を用いて、良質なGaAs系の結晶薄膜を得る。

【解決手段】Siの基板と、基板上に結晶成長され、孤立した島状に形成されたGe層と、Ge層の上に結晶成長され、Pを含む3−5族化合物半導体層からなるバッファ層と、バッファ層の上に結晶成長された機能層と、を備える半導体基板を提供する。Ge層は、アニールした場合に、アニールの温度および時間において結晶欠陥が移動する距離の2倍を越えない大きさの島状に形成する。あるいはGe層は、アニールした場合に、アニールの温度において基板であるSiとの熱膨張係数の相違によるストレスが剥離を発生させない大きさの島状に形成する。

(もっと読む)

半導体基板、半導体基板の製造方法および電子デバイス

【課題】安価な、また、放熱特性に優れたSi基板を用いて、良質なGaAs系の結晶薄膜を得る。

【解決手段】Siの基板と、基板の上に形成され、結晶成長を阻害する阻害層とを備え、阻害層は、基板の一部を覆う被覆領域と、被覆領域の内部に基板を覆わない開口領域とを有し、さらに開口領域に結晶成長されたGe層と、Ge層上に結晶成長された機能層と、を備える半導体基板を提供する。当該半導体基板において、Ge層は、結晶欠陥が移動できる温度および時間でアニールされることにより形成されてよい。

(もっと読む)

半導体基板および半導体基板の製造方法

【課題】安価な、また、放熱特性に優れたSi基板を用いて、良質なGaAs系の結晶薄膜を得る。

【解決手段】単結晶Siの基板と、基板の上に形成され、開口領域を有する絶縁層と、開口領域の基板上にエピタキシャル成長されたGe層と、Ge層の上にエピタキシャル成長されたGaAs層と、を備え、Ge層は、超高真空の減圧状態にできるCVD反応室に基板を導入し、原料ガスを熱分解できる第1温度で第1のエピタキシャル成長を実施し、第1温度より高い第2温度で第2のエピタキシャル成長を実施し、第1および第2のエピタキシャル成長を実施したエピタキシャル層をGeの融点に達しない第3温度で第1のアニールを実施し、第3温度より低い第4温度で第2のアニールを実施して形成された半導体基板を提供する。

(もっと読む)

半導体装置

【課題】高耐圧で、かつ、オン抵抗を十分に小さくすることが可能な半導体装置を提供する。

【解決手段】この半導体装置1は、P型の半導体層6と、半導体層6の主表面上の所定領域にゲート絶縁膜4を介して配置されたゲート電極5とを備え、半導体層6は、ゲート電極5の下側を覆うように形成されたN-型ウェル領域11と、N-型ウェル領域11内の主表面側に形成されたP-型ボディ領域12と、P-型ボディ領域12内の主表面側で、かつ、ゲート電極5の一方(矢印A方向)側に形成されたN+型ソース領域13と、N-型ウェル領域11内の主表面側で、かつ、ゲート電極5の他方(矢印B方向)側に形成されたN+型ドレイン領域15と、P-型ボディ領域12の真下でない位置で、かつ、少なくともN+型ドレイン領域15の真下の位置に形成され、N+型ドレイン領域15に接続されたN+型埋め込み領域16とを含む。

(もっと読む)

半導体装置

【課題】バイポーラトランジスタ構造を有する静電破壊保護素子のホールド電圧を従来に比して高くするとともに、当該素子のサイズを抑える技術を提供することを目的とする。

【解決手段】エピタキシャル層2の表面にベース領域(P不純物層4)が形成され、P不純物層4の表面にエミッタ領域(N+不純物層5)が形成され、エピタキシャル層2とN+不純物層6とから成るコレクタ領域が構成されている。ベース電極8とベース領域(P不純物層4)の接続部が、ベース領域(P不純物層4)のコレクタ電極10側の端部とエミッタ領域(N+不純物層5)との間に位置する。つまり、コレクタ・ベース・エミッタの順で各電極が構成されている。ベース電極8とエミッタ電極9とは不図示の配線を介して接続されている。また、エピタキシャル層2を複数の島領域に分離するためのP+分離層11が形成されている。

(もっと読む)

1 - 20 / 101

[ Back to top ]