Fターム[5F003BA96]の内容

バイポーラトランジスタ (11,930) | 素子構造 (1,262) | 集積回路用 (671) | 素子分離 (611) | 酸化物分離 (258)

Fターム[5F003BA96]の下位に属するFターム

LOCOS (118)

Fターム[5F003BA96]に分類される特許

1 - 20 / 140

半導体装置

【課題】ホールド電圧が高いエミッタ・ベース短絡型の保護素子が設けられた半導体装置を提供する。

【解決手段】半導体装置1は、基板10と、前記基板上に形成された第1導電形の半導体層11と、前記基板と前記半導体層との間に形成された第1導電形の埋込層13と、前記半導体層上に形成された第2導電形のウェル14と、前記半導体層上であって、前記ウェルから離隔し、前記埋込層の直上域に形成された第1導電形の第1コンタクト層15と、前記ウェル上に形成された第2導電形の第2コンタクト層16と、前記ウェル上であって、前記第1コンタクト層と前記第2コンタクト層との間に形成された第1導電形の第3コンタクト層17と、前記埋込層と前記第1コンタクト層との間に形成され、前記第1コンタクト層に接した第1導電形のディープ層18と、を備える。

(もっと読む)

半導体装置

【課題】保護素子の異なるクランプ電圧を容易に設定して形成できる構造の保護素子を含む半導体装置を提供すること。

【解決手段】回路内部のMOS型半導体装置のゲート酸化膜を保護するための保護素子を含む半導体装置であって、該保護素子は、該MOS型半導体装置とその前段回路との間に接続される横型バイポーラトランジスタであり、該横型バイポーラトランジスタのパンチスルー耐圧をクランプ電圧として利用することを特徴とする、半導体装置。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ラテラル・バイポーラトランジスタを有する半導体装置であって、エミッタポリシリコンに対する良好なコンタクトを得ることができる半導体装置及びその半導体装置の製造方法を提供する。

【解決手段】ラテラル・バイポーラトランジスタを有する半導体装置であって、ラテラル・バイポーラトランジスタは、第1の導電層を構成する基板と、第1の導電層上に配置されたn−hill層312と、n−hill層312を囲む素子分離酸化膜320に開口されたオープン領域と、オープン領域上に形成されるポリシリコン膜910と、ポリシリコン膜910から固相拡散されたエミッタ領域と、素子分離酸化膜320に形成されたダミーゲートポリシリコン706と、を有し、ダミーゲートポリシリコン706によってポリシリコン膜910からの固相拡散されるエミッタ領域の形状が制御される。

(もっと読む)

トランジスタ素子

【課題】単体構造のHBTデバイスと同等の信頼性を得る。

【解決手段】化合物半導体からなる、高電子移動度トランジスタ(HEMT)とヘテロバイポーラトランジスタ(HBT)とを、同一基板上に重ねてエピタキシャル成長した多層構造のトランジスタ素子において、エピ層として内在するインジウムガリウムリン層(InGaP)のバンドギャップエネルギを1.91eV以上にすることを特徴とする。

(もっと読む)

半導体装置

【課題】バイポーラトランジスタのエミッタ窓における絶縁膜厚の変動をなくし、素子特性が安定した半導体装置を提供する。

【解決手段】バイポーラトランジスタを、コレクタ領域を含む基板1、基板1上にエピタキシャル成長で形成されたSiGe層126、SiGe層126上にポリシリコンによって形成されたエミッタ108を備え、エミッタ108とSiGe層126との界面において、ポリシリコン膜106とSiN膜127とでエミッタ窓120を形成し、SiN膜127がSiGe層126の直上に配置されるように形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】少工数で製造可能で且つ高い耐圧性能を有する半導体装置を提供する。

【解決手段】素子形成領域と、素子形成領域を外部領域から絶縁分離するべく素子形成領域表面から基板表面までの深さで素子形成領域側面を包囲するよう形成された第1絶縁トレンチ領域10aとを備える半導体装置であって、素子形成領域は、埋め込みコレクタ領域と、コレクタ耐圧領域4と、ベース領域5と、表面コレクタ領域8bと、エミッタ領域8aと、ベース領域と表面コレクタ領域との間におけるキャリアの直線的な移動を遮るよう、当該領域間において素子形成領域表面から基板表面にまでの深さで形成される第2絶縁トレンチ領域10bとを備え、半導体装置を平面視した際、第2絶縁トレンチと第1絶縁トレンチ領域との間には、キャリアが第2絶縁トレンチを迂回してベース領域と表面コレクタ領域との間を移動するためのキャリア迂回領域12a,12bが形成される。

(もっと読む)

半導体装置

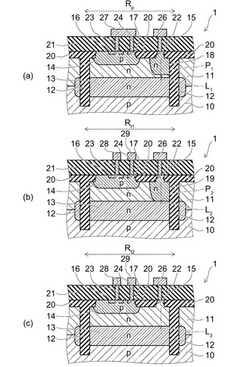

【課題】 放熱性を改善したバイポーラトランジスタを有する半導体装置を提供することにある。

【解決手段】 複数のバイポーラトランジスタQuが配列される半導体装置であって、エミッタ配線L3は幅広部と細長部とを有し、細長部におけるバイポーラトランジスタ素子数が、幅広部が配置された配列の外縁に沿う方向に配列されたバイポーラトランジスタ素子数よりも少なくなるように配置する。

【効果】エミッタ配線の寄生抵抗によるエミッタ−ベース間電圧ばらつきを低減する。

(もっと読む)

不純物濃度プロファイルの測定方法、その方法に用いられるウェーハ、および、その方法を用いる半導体装置の製造方法

【課題】半導体層の不純物濃度およびプロファイルを正確に制御することを可能とする不純物濃度プロファイルの測定方法、その方法に用いられるウェーハ、および、それを用いた半導体装置の製造方法を提供する。

【解決手段】基板10と、前記基板10の主面上に設けられた半導体層12,17であって、前記主面上において互いに面積の異なる複数の第1領域17a,17bに形成された第1の部分と、前記主面上で前記第1領域17a,17bを取り囲む第2領域17cに形成され前記第1の部分とは異なる構造を有する第2の部分と、を有する半導体層12,17と、を有するウェーハを用いる。そして、前記半導体層のうちの複数の前記第1の部分の表面から深さ方向の不純物濃度プロファイルを測定し、前記第1の部分の面積に依存する前記不純物濃度プロファイルの変化を求める。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】BiFETデバイスに含まれるFETのオン抵抗の悪化を抑制する。

【解決手段】共通基板1上に第1SL10及び第2SL20積層体が順に形成された半導体装置であって、第2積層体が除去されて残存する第1積層体は、電界効果型トランジスタを構成し、第1積層体上に積層された第2積層体は、電界効果型トランジスタとは異なる素子(バイポーラトランジスタ)を構成し、電界効果型トランジスタを構成する第1積層体は、第1積層体に形成されるリセスの停止位置を規定し、かつInGaPから成るエッチング停止層10と、リセス内に配置されるゲート電極25の下方に配置され、かつAlGaAsから成る下部化合物半導体層8と、エッチング停止層10と下部化合物半導体層8との間に挿入され、エッチング停止層に含まれるリンが下部化合物半導体層まで熱拡散し、下部化合物半導体層を構成する元素と化合することを抑止するスペーサ層9とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】容易なプロセスにより単結晶半導体層を形成したSOI構造のMISFETの提供

【解決手段】半導体基板1上に、第1の絶縁膜2を介して、一部に空孔4を有する第2の絶縁膜3が設けられ、空孔4上及び第2の絶縁膜3の一部上に島状に絶縁分離された半導体層6が設けられ、半導体層6上にゲート酸化膜12を介して、空孔4直上に空孔4の幅以下のゲート電極13が設けられ、半導体層6には、ゲート電極13に自己整合して低濃度のソースドレイン領域(9,10)が、ゲート電極13の側壁に設けられたサイドウォール14に自己整合して高濃度のソースドレイン領域(8,11)がそれぞれ設けられ、ゲート電極13(配線図示せず)及び高濃度のソースドレイン領域(8,11)にはバリアメタル17を有する導電プラグ18を介してバリアメタル20を有する配線21が接続されているMISFET。

(もっと読む)

半導体装置

【課題】支持基板に接地電極を備えることなく、第1、第2素子形成領域間でノイズが伝播することを抑制することができる半導体装置を提供する。

【解決手段】支持基板10を、第1導電型領域10aと第2導電型領域10bとを有し、第1素子形成領域20にノイズが印加されてノイズが伝播されたときの当該ノイズの伝播経路中に、第1、第2導電型領域10a、10bで構成されるPNP接合またはNPN接合を有するものとする。このような半導体装置では、PNP接合またはNPN接合の間に構成される空乏層により、第1、第2素子形成領域20、30の間でノイズが伝播することを抑制することができる。

(もっと読む)

半導体装置

【課題】同一基板上にヘテロ接合バイポーラトランジスタ(HBT)と電界効果トランジスタ(FET)とが形成され、HBTのコレクタ抵抗が低減されてHBTの特性が向上され、かつFETのゲートリセスのエッチング精度が良好で、FETのオン抵抗が低い半導体装置を安定的に提供する。

【解決手段】HBT101Aにおいては、サブコレクタ層が複数の半導体層13〜15の積層構造からなり、かつ、サブコレクタ層においてコレクタ層17より張り出した部分上にコレクタ電極28が形成されている。FET101B、101Cにおいては、HBT101Aのサブコレクタ層をなす複数の半導体層のうち半導体基板1側の少なくとも1層の半導体層13が、キャップ層の少なくとも一部の層を兼ねている。HBTサブコレクタ層の総膜厚が500nm以上であり、FETキャップ層の総膜厚が50nm以上300nm以下である。

(もっと読む)

半導体装置

【課題】第1、第2素子形成領域間でノイズが伝播することを抑制することができる半導体装置を提供することを目的とする。

【解決手段】第1、第2素子形成領域20、30に形成された半導体素子のうち、第1素子形成領域20に形成された半導体素子を外部機器と接続し、第1素子形成領域20と第2素子形成領域30との間に、第1導電型層60と、当該第1導電型層60に挟まれる第2導電型層61とを配置し、第1、第2導電型層60、61の間に、オフ時に半導体層12の表面から埋込絶縁膜11に達し、第1、第2素子形成領域20、30との間を仕切る空乏層63、64を構成する。

(もっと読む)

シリコンゲルマニウムトランジスタの製造方法

【課題】犠牲エミッタ膜を高い選択性で除去することにより特性のバラツキを抑制し、高精度なホトリソグラフィー技術を必要としないシリコンゲルマニウムトランジスタの製造方法を提供する。

【解決手段】SiGe膜6上のシリコン酸化膜8上にN型の犠牲エミッタポリシリコン23を形成し、その周囲にシリコン窒化膜からなるサイドウォール7を形成する。次に、ノンドープのポリシリコン膜24を形成し、サイドウォール7及び犠牲エミッタポリシリコン23をマスクにSiGe膜6にP型不純物をイオン注入して、外部ベース領域を形成する。次に、犠牲エミッタポリシリコン23をエッチングして除去し、その下のシリコン酸化膜8も除去する。その後、犠牲エミッタポリシリコン23等が除去されたエミッタ部分にエミッタポリシリコンを形成する。犠牲エミッタポリシリコン23をエッチングして除去する工程では、エッチャントとしてTMAH水溶液を使用する。

(もっと読む)

半導体装置及びその製造方法

【課題】結晶欠陥による接合リークを防止しながら、バイポーラトランジスタの面積を縮小し、コレクタ容量の低減によってトランジスタ特性を向上できるようにした半導体装置及びその製造方法を提供する。

【解決手段】活性領域1からSTI4上にかけて連続して形成したSiGe膜は、半導体基板3上ではSiGeエピ膜6となり、STI4上ではSiGeポリ膜7となる。半導体基板3とSTI4の境界はSiGe−HBT形成工程以前の洗浄工程によって段差15が生じており、SiGeエピ膜6及び半導体基板3には、上記境界を基点とした結晶欠陥が応力によって発生する可能性がある。この境界に第1のP型不純物層8及び第2のP型不純物層9を設けることで、結晶欠陥をこれらP型不純物層8、9に内包し、接合リークの発生を抑制する。

(もっと読む)

トレンチにより制限された分離拡散領域を備えた相補型アナログバイポーラトランジスタ

【課題】表面上に素子をより高密度に実装する。

【解決手段】第1のトレンチと第2のトレンチとの間の位置において、エピタキシャル層の表面から基板へと下方に延在するドーパントのウェルは、エピタキシャル層の背景ドーピング濃度とは異なるドーピング濃度を有し、エピタキシャル層の残りの部分と第1および第2の接合を形成する。第1の接合は、第1のトレンチの底部から基板に延在し、第2の接合は、第2のトレンチの底部から前記基板に延在する。ウェルおよび第1および第2のトレンチは分離構造を構成し、分離構造は、分離構造の一方側のエピタキシャル層に形成された第1の素子と分離構造の他方側のエピタキシャル層に形成された第2の素子とを電気的に分離する。分離構造による電気的分離は第1および第2のトレンチとPN接合とによってもたらされ、ウェルは第1の導電型の材料でドープされ、基板およびエピタキシャル層は、第1の導電型とは反対の第2の導電型の材料でドープされ、第1および第2の接合はPN接合である。

(もっと読む)

半導体装置およびその製造方法

【課題】形成する素子に要求される素子間耐圧や素子内部耐圧に応じたディープトレンチ膜を有する半導体装置を提供する。

【解決手段】P型のシリコン基板11上に、N+型埋め込み層12と、N型半導体層13と、が積層された基板10と、基板10にN+型埋め込み層12の形成位置よりも深く形成され、基板10内の素子形成領域内を区画するディープトレンチ20と、ディープトレンチ20の内壁に沿って形成される側壁酸化膜23,24と、ディープトレンチ20内を埋めるTEOS膜を含むディープトレンチ膜26と、ディープトレンチ膜26で区画される素子形成領域に形成されるLDMOSと、を備え、ディープトレンチ20は、N+型埋め込み層12の上面よりも浅い位置の境界深さまでの第1のディープトレンチ21と、境界深さから底部までの第1のディープトレンチ21よりも小さい開口径を有する第2のディープトレンチ22によって構成される。

(もっと読む)

半導体装置およびその製造方法

【課題】低コストで性能向上が可能なBiCMOS型半導体集積回路装置を実現することができる半導体装置およびその製造方法を提供する。

【解決手段】n型の半導体基板1の表面から所定の深さに、コレクタ領域を構成するn型の不純物領域26を備える。当該不純物領域26の上方、かつ半導体基板1に形成されたシャロートレンチ分離14で挟まれた領域18にはp型のベース領域20を備える。ベース領域20には、n型の半導体膜からなるエミッタ電極が接触して設けられている。当該半導体装置は、不純物領域26がベース領域20下からシャロートレンチ分離14下まで延在し、当該シャロートレンチ分離14を貫通して不純物領域26に電気的に接続するコンタクトプラグ52を備える。

(もっと読む)

バイポーラ・トランジスタ及びその製造方法

【課題】 バイポーラ・トランジスタ構造体、バイポーラ・トランジスタを設計し製造する方法、及びバイポーラ・トランジスタを有する回路を設計する方法を提供する。

【解決手段】 バイポーラ・トランジスタを設計する方法は、バイポーラ・トランジスタの初期設計を選択するステップ(図25の240)と、バイポーラ・トランジスタの初期設計をスケーリングしてバイポーラ・トランジスタの縮小設計を生成するステップ(245)と、バイポーラ・トランジスタの縮小設計の応力補償が必要かどうかを、スケーリング後のバイポーラ・トランジスタのエミッタの寸法に基づいて判断するステップ(250)と、バイポーラ・トランジスタの縮小設計の応力補償が必要な場合に、縮小設計のトレンチ分離レイアウト・レベルのレイアウトを、縮小設計のエミッタ・レイアウト・レベルのレイアウトに対して調節して(255)バイポーラ・トランジスタの応力補償縮小設計を生成するステップ(260)と、を含む。

(もっと読む)

半導体基板、電子デバイス、半導体基板の製造方法及び電子デバイスの製造方法

【課題】半導体基板、電子デバイス、半導体基板の製造方法及び電子デバイスの製造方法を提供する。

【解決手段】シリコンに不純物原子が導入された不純物領域104を有するベース基板102と、不純物領域104に接して設けられている複数のシード体112と、複数のシード体112の各々に接して設けられ、複数のシード体112の各々とそれぞれ格子整合または擬格子整合する複数の化合物半導体114とを備える半導体基板100。当該半導体基板100は、ベース基板102上に設けられ、不純物領域104の少なくとも一部を露出する複数の開口が設けられた阻害体をさらに備えてもよい。

(もっと読む)

1 - 20 / 140

[ Back to top ]