Fターム[5F003BC09]の内容

バイポーラトランジスタ (11,930) | コレクタ (1,152) | マルチコレクタ (19)

Fターム[5F003BC09]に分類される特許

1 - 19 / 19

ヘテロ接合バイポーラトランジスタ

【課題】GaAsSb系の化合物半導体のベース層を有するInP系HBTにおいて、高周波特性を犠牲にすることなく、さらにオフ耐圧を向上させる。

【解決手段】InPからなる基板101の上に形成された第1コレクタ層102と、この上に形成された第2コレクタ層103と、この上に形成されてGa,As,およびSbから構成された化合物半導体からなるベース層104と、この上に形成されてInおよびPから構成された化合物半導体からなるエミッタ層105とを少なくとも備える。第2コレクタ層103は、第1コレクタ層102およびベース層104に接した状態で、ベース層104の伝導帯端のエネルギー準位よりも低く、第1コレクタ層102の伝導帯端よりも高い伝導帯端のエネルギー準位を有し、ベース層104の価電子帯端のエネルギー準位よりも低い価電子帯端のエネルギー準位を有したものとなっている。

(もっと読む)

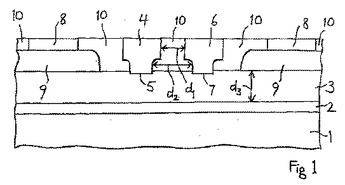

横方向のエミッタおよびコレクタを有するバイポーラトランジスタならびに製造方法

バイポーラトランジスタは、半導体材料からなる基板(1)と、基板内の高移動度層(2)と、高移動度層に隣接したドナー層(3)とを含む。エミッタ端子(4)がドナー層上のエミッタコンタクト(5)を形成し、コレクタ端子(6)がドナー層上のコレクタコンタクト(7)を形成する。ベース端子(8)が高移動度層に導電接続される。当該トランジスタは、GaAsのHEMT技術またはBiFET技術で製造可能である。  (もっと読む)

(もっと読む)

ESD保護素子

【課題】ESD耐量を向上させたESD保護素子を提供する。

【解決手段】本発明によるESD保護素子は、バイポーラトランジスタを用いたESD保護素子である。バイポーラトランジスタは、第1端子(Pad)に接続されるコレクタ拡散層7とエミッタ端子とを備えるバイポーラトランジスタと、第2端子(GND)からエミッタ拡散層4を介してコレクタ拡散層7に至る複数の電流経路上のそれぞれに設けられた電流制御抵抗11とを具備する。

(もっと読む)

非単結晶半導体間隔部分がベース・リンク長を制御するバイポーラ接合トランジスタを有する半導体構成体の構成及び製造

【課題】 半導体構成体がバイポーラトランジスタ(101)及び間隔構成体(265−1又は265−2)を包含している。

【解決手段】 該トランジスタはエミッタ(241)、ベース(243)、コレクタ(245)を有している。該ベースはベースコンタクト部分(243−1)、該エミッタの下側で且つ該コレクタの物質上方に位置されているイントリンシックベース部分(243I−1)、該イントリンシックベース部分とベースコンタクト部分との間に延在しているベースリンク部分(243L−1)を包含している。該間隔構成体は、間隔コンポーネント及び上部半導体表面に沿って延在する分離用誘電体層(267−1又は267−2)を包含している。該間隔コンポーネントは、該ベースリンク部分の上方で該誘電体層上に位置されており、好適には多結晶半導体物質であるほぼ非単結晶の半導体物質の横方向間隔部分(269−1又は269−2)を包含している。該横方向間隔部分の両側の第1及び第2下部端部(305−1及び307−1)は該ベースリンク部分の両側の第1及び第2上部端部(297−1及び299−1)に対して横方向に適合し、その長さを決定し且つそれにより制御する。

(もっと読む)

半導体デバイス用基板、半導体デバイス装置、設計システム、製造方法、および設計方法

【課題】結晶薄膜の膜質および膜厚を均一にする。

【解決手段】半導体デバイスを形成するためのデバイス用薄膜と、デバイス用薄膜を囲み、デバイス用薄膜の前駆体が結晶に成長することを阻害する阻害部と、前駆体が結晶に犠牲成長することによって形成された犠牲成長部であって、デバイス用薄膜の周辺に阻害部で隔てられて設けられた犠牲成長部と、犠牲成長部の上部を覆い、かつデバイス用薄膜の上部を露出する保護膜を備えた。保護膜はポリイミドであってもよい。

(もっと読む)

n型ベースを有するバイポーラトランジスタ及びその製造方法

【解決手段】ベースコンタクト接続部(12)、エミッタ部(4、5)及びコレクタ部がn層(3)上に配置され、当該n層は、更なるnpnバイポーラトランジスタために用いることができる。当該コレクタ部はエミッタ部に対して側方に配置され、当該エミッタ部及びコレクタ部の少なくとも一方は、当該n層の表面領域上でショットキーコンタクト(14)を備える。 (もっと読む)

バイポーラトランジスタの製造方法

【課題】各拡散領域を形成する際のアライメントずれを抑制することができ、各拡散領域の位置精度が高く、電気特性のばらつきを低減することのできるバイポーラトランジスタの製造方法を提供する。

【解決手段】N型半導体基板10の表層部に、ベース領域であるP型拡散領域30、エミッタ領域である第1のN型拡散領域31およびコレクタ領域である第2のN型拡散領域32a,32bを形成するバイポーラトランジスタ100の製造方法であって、半導体基板上10に、複数の開口部を有するLOCOS酸化膜20を形成し、所定の開口部を介して不純物をイオン注入し、P型拡散領域30または第1のN型拡散領域31の一方を最初に形成し、次に、縮小または拡大された前記所定の開口部を介して不純物をイオン注入し、P型拡散領域30または第1のN型拡散領域31のもう一方を形成する製造方法とする。

(もっと読む)

半導体装置及びその製造方法

【課題】トレードオフの関係にあるHBTの特性上のメリットとHFETの特性上のメリットとを両立することが可能な半導体装置及びその製造方法を提供する。

【解決手段】Bi−HFETであって、HBTは、順次積層されたサブコレクタ層107、GaAsコレクタ層108、GaAsベース層109及びInGaPエミッタ層110を有し、サブコレクタ層107は、GaAs外部サブコレクタ領域107aと、GaAs外部サブコレクタ領域107a上に位置するGaAs内部サブコレクタ領域107bとを有し、GaAs外部サブコレクタ領域107a上には、メサ状のコレクタ部830と、コレクタ電極203とが離間して形成され、HFETは、GaAs外部サブコレクタ領域107aの一部により構成されたGaAsキャップ層105と、GaAsキャップ層105上に形成されたソース電極304及びドレイン電極305とを有する。

(もっと読む)

半導体装置

【課題】耐性の低下を抑制するとともに、誤作動を抑制することができる半導体装置を提供すること。

【解決手段】本実施形態の半導体装置1は、一対のトランジスタQ1,Q2が形成された第一導電型の半導体基板13を有する。各トランジスタQ1,Q2は、半導体基板13中に形成された第二導電型のコレクタ領域101と、このコレクタ領域101内に形成された第一導電型のベース領域102と、前記ベース領域102内に形成された第二導電型のエミッタ領域103とを有している。各トランジスタQ1,Q2の各コレクタ領域101は、離間配置されるとともに、各トランジスタQ1,Q2のコレクタ領域101間には、第一導電型の第一領域11が形成されている。各トランジスタQ1,Q2のコレクタ領域101の下部同士は、半導体基板13内に形成された第二導電型の埋め込み層12により接続されている。

(もっと読む)

電力増幅器

【課題】集積回路チップと実装基板との接続の容易性や、放熱性の良好さを維持したままで、各単位セル動作の均一性を確保し、出力段トランジスタの総合的な動作特性を改善する。

【解決手段】

コレクタ電極配線101は、平行する2つの単位セル列用コレクタ電極配線1,2が、その一方の端部で、出力用配線3によって接続されてなり、この出力端とされる一方、単位セル列用コレクタ電極配線1,2の他方の端部は、セル列間接続配線4により相互に接続されたものとなっており、これによって、各単位セルの動作の均一性の改善がなされるものとなっている。

(もっと読む)

ヘテロ接合バイポーラトランジスタ及びこれを用いた電力増幅器

【課題】大出力電力に対応した電力増幅用ヘテロ接合バイポーラトランジスタを小さい面積にレイアウトすることを可能とする。

【解決手段】サブコレクタ層上に、コレクタ層が互いに分離された複数のトランジスタ要素をエミッタの長辺方向に1列に配置して、ヘテロ接合バイポーラトランジスタを形成する。さらに、前記ヘテロ接合バイポーラトランジスタを単位トランジスタとして、マルチフィンガー型ヘテロ接合バイポーラトランジスタを構成する。

(もっと読む)

半導体装置およびその製造方法

【課題】NPNトランジスタ等のバイポーラリニア素子とIIL素子とを同一の半導体基板上に備えた半導体装置であって、高耐圧であるとともに、動作特性の優れたIIL素子を有するものを提供すること。

【解決手段】IIL素子に含まれたマルチコレクタ型NPNトランジスタTr1は、半導体基板101の裏面側から表面側へ向かう縦方向に順にN型エミッタ層Tr1E、P型ベース層Tr1B、N型コレクタ層Tr1Cを備える。マルチコレクタ型NPNトランジスタのP型ベース層Tr1Bは、エミッタ層Tr1E側で高く、かつコレクタ層Tr1C側で低くなるように傾斜した不純物濃度プロファイルを持つ。

(もっと読む)

半導体装置及びその製造方法

【課題】 ベース/コレクタ接合容量およびベース層の引き出し抵抗を減少させることのできる電極構造を有する半導体素子を含む半導体装置及びその製造方法を提供すること。

【解決手段】 半絶縁性基板1の上にエピタキシャル成長法によって、サブコレクタ層2、コレクタ層3、ベース層4、エミッタ層5、エミッタキャップ層6の構成材料層を形成し、これらをメサ構造に加工してヘテロ接合バイポーラトランジスタ(HBT)素子20を形成する。HBT素子20では、ベース電極8をセンターに配置し、この幅方向両側にエミッタメサおよびエミッタ電極9を各2本形成する。ベース電極8の上には厚さが厚く、低抵抗なベース引き出し配線18を直接形成する。この際、ベース層4およびコレクタ層3の一部をその積層方向に同一パターンに除去し、この除去領域21を含む領域上にベース電極8およびベース引き出し配線18を形成する。

(もっと読む)

ベースアクセス抵抗を改善したNPNバイポーラトランジスタ用の方法及び装置

複数の短エミッタからなる構造は、共通のDTI領域及びベースポリの単一巨大片を共有する。これにより、ベース電流が、2方向のみとは対照的に、4方向(例えば2次元)に流れることができる。これにより、より優れたNPNトランジスタRF性能及び高周波ノイズ性能に不可欠なトランジスタのベース抵抗の顕著な低減がなされる。  (もっと読む)

(もっと読む)

半導体装置、および温度検出方法

【課題】構造面および製造面において、簡易で生産性に優れた小型で低コストの半導体装置および、当該半導体装置を高精度に動作させるための温度検出方法の提供を図る。

【解決手段】半導体装置10は、半導体基板に形成した半導体素子によって温度検出をおこなう温度検出部12と、半導体基板に設けられ、温度検出部12の検出信号を外部出力するための温度検出部出力端子T3と、温度検出部出力端子T3に接続され、温度検出部12に駆動電流を供給する電流発生手段と、温度検出部出力端子T3に接続され、温度検出部出力端子T3の電圧値を測定する電圧測定手段とを備え、電流発生手段から温度検出部12に対して所定量の電流を供給した際に電圧測定手段によって測定された電圧値に基づいて温度検出をおこなう。

(もっと読む)

マルチコレクタ型ラテラルPNPトランジスタおよびその製造方法、カレントミラー定電流回路並びに半導体装置

【課題】 コレクタ電流比の精度を高めることができるマルチコレクタ型ラテラルPNPトランジスタを提供すること。

【解決手段】 層状に設けられたベース領域3と、ベース領域3の表面に閉領域をなすパターンで形成されたエミッタ領域5とを備える。ベース領域3の表面のうちエミッタ領域5から離間した位置に、エミッタ領域5に対して対称なパターンで互いに離間して形成された少なくとも一対のコレクタ領域6A,6Bを備える。各領域3,5,6A,6Bを覆う絶縁膜を備える。その絶縁膜は少なくともエミッタ領域5に対応した位置にエミッタ電極配線接続用のコンタクト窓19を有する。そのコンタクト窓19のパターン寸法W2は、エミッタ領域5のパターン寸法W1に対して1/2以下である。

(もっと読む)

半導体装置およびその製造方法

【課題】 電力利得および高周波出力特性が向上した通信機器用バイポーラトランジスタを提供する。

【解決手段】 真性ベース領域とベース電極20Bとを接続する外部ベース層11の平面形状をU字状にする。そして、基板1の主面に平行な面内において、コレクタ電極20Cの長辺とエミッタ電極20Eの長辺とを平行に配置し、コレクタ電極20Cとエミッタ電極20Eとを交互に並んで配列する。一方、ベース電極20Bは、コレクタ電極20Cおよびエミッタ電極20Eのそれぞれの一端部を結ぶ直線の外側に配置し、ベース電極20Bの長辺をコレクタ電極20Cおよびエミッタ電極20Eのそれぞれの長辺と直交するように配向する。

(もっと読む)

横型バイポーラトランジスタ

【課題】 この発明は、SOI基板上に形成するうえで好適な構造を有する横型バイポーラトランジスタに関し、MOSプロセスの流用による形成を可能とし、かつ、十分なコレクタ電流を確保することを目的とする。

【解決手段】 埋め込み酸化膜11を有するSOI基板上に、複数のベース・エミッタ領域を形成する。個々のベース・エミッタ領域には、ベース引き出しP+拡散層(例えば14A)と、エミッタN+拡散層(例えば15A,15B)を含ませる。隣接するベース・エミッタ領域の間にコレクタN+拡散層16を配置する。各拡散層の間を埋めるように低濃度のP型ウェル拡散層(例えば12B,12C)を配置する。全てのベース引き出しP+拡散層14A〜14Eをベースコンタクト8に接続し、全てのエミッタN+拡散層15A〜15Iをエミッタコンタクト9に接続する。

(もっと読む)

マルチフィンガバイポーラトランジスタ

【課題】 半絶縁性半導体基板上に形成される放熱効率の高い小型のマルチフィンガバイポーラトランジスタを提供する。

【解決手段】 半絶縁性半導体基板61上面に、階段状で凸形状の基本セル1〜4を配列形成している。各基本セル1〜4は、n型半導体層62、p型半導体層63、n型半導体層64を順に積層形成してなり、n型半導体層62の上面にコレクタフィンガ電極31a〜34a、31b〜34bを、p型半導体層63の上面にベースフィンガ電極21a〜24a、21b〜24bを、n型半導体層64の上面にエミッタフィンガ電極11〜14を形成している。エミッタフィンガ電極11〜14は、第1ビアホール101〜104、中間電極40、および第2ビアホール201〜208を介して半絶縁性半導体基板61の下面に形成された接地電極50に導通している。

(もっと読む)

1 - 19 / 19

[ Back to top ]