Fターム[5F032AA12]の内容

素子分離 (28,488) | 絶縁物を用いる分離 (9,448) | 素子領域側面を絶縁物で分離するもの (8,208) | 絶縁化分離 (375)

Fターム[5F032AA12]の下位に属するFターム

選択酸化(LOCOS)分離 (337)

耐酸化マスクを用いない酸化分離 (3)

複数の溝間を全て酸化しその酸化物で分離するもの (16)

絶縁物をイオン注入で形成するもの (7)

Fターム[5F032AA12]に分類される特許

1 - 12 / 12

半導体装置の製造方法、半導体装置

【課題】SiCが用いられる半導体層中において、簡易な工程で再現性よく埋め込み絶縁層を形成する。

【解決手段】単結晶のSiC12の表面の温度を局所的に急激に上昇させ、その後で急激に冷却することによって、単結晶を局所的に非晶質化層30を形成することができる。この非晶質層30は、元の単結晶SiCの導電型や抵抗率に関わらず、高抵抗層(絶縁層)となる。このため、こうした非晶質層を埋め込み絶縁層と同様に使用することができる。このためには、(1)レーザー光を効率的に吸収する層100を局所的に半導体層の上に形成してからレーザー光を照射する、(2)レーザー光を局所的に半導体層に照射する、という2つの手段のいずれかを用いることができる。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】工程増を最小限とした簡便な手法で、素子形成領域における化合物半導体と同時に、しかもその結晶性を損なうことなく確実な素子分離を実現し、信頼性の高い化合物半導体装置を実現する。

【解決手段】Si基板1上の素子分離領域に初期層3を選択的に形成し、初期層3上を含むSi基板1上の全面に化合物半導体の積層構造4を形成して、積層構造4は、素子分離領域では初期層3と共に素子分離構造4Bとなり、素子形成領域ではソース電極5、ドレイン電極6及びゲート電極7が形成される素子形成層4Aとなる。

(もっと読む)

III族窒化物半導体からなる半導体素子およびその製造方法

【課題】III 族窒化物半導体からなる半導体素子の製造方法において、素子分離工程を容易とすること。

【解決手段】HFET1は、SI−SiCからなる基板10上に、ノンドープのGaN層11、ノンドープのAlGaN層12が積層され、AlGaN層12上にソース電極13、ゲート電極14、ドレイン電極15が形成され、素子分離領域16によって他の素子と分離されている構造である。素子分離領域16は、CF4 ガスプラズマに晒して絶縁化させることで形成した。このようにプラズマ曝露によって素子分離領域を形成したとしても素子の動作に影響を与えることはなく、良好な絶縁特性が得られる。

(もっと読む)

半導体装置製造方法

【課題】 半絶縁性半導体基板をドライエッチングで加工後、選択エピタキシャル技術を用いることにより、素子を形成すると共に、メサエッチングを行わずに素子分離を実現する。

【解決手段】 共通の基板上に複数の半導体素子を形成すると共に、所定の間隔で分割することにより、独立した複数の半導体素子を形成する半導体装置製造方法において、前記基板として絶縁基板を使用し、この基板表面に絶縁膜を形成し、前記複数の半導体素子を形成する領域に対応した前記絶縁膜を取り除くステップと、前記基板を異方性エッチングにより、任意の深さまで取り除き、素子部を成長させる基板部と複数の素子間に介在する境界部とを形成するステップと、前記基板を選択エピタキシャルにより、前記基板に素子部を成長させるステップと、前記境界部において、前記基板を切断するステップとを有することを特徴とする。

(もっと読む)

薄膜トランジスタの製造方法、薄膜トランジスタ及び画像表示装置

【課題】簡便なプロセスで素子分離が可能な薄膜トランジスタの製造方法、薄膜トランジスタおよび画像表示装置を提供すること。

【解決手段】絶縁基板上にゲート電極、ゲート絶縁膜、一対の主電極領域を形成する工程と、一対の主電極領域上を含む絶縁基板上の全面に有機半導体層を形成する工程と、有機半導体層と一対の主電極領域との間のチャネル領域を覆う封止層を形成する工程と、有機半導体層の前記封止層の形成されていない領域を非活性化させる工程と、を備えたことを特徴とする薄膜トランジスタの製造方法。

(もっと読む)

光半導体集積装置およびその製造方法

【課題】素子分離領域を有する光半導体集積装置の製造において、マスクを使った半導体層の選択成長時における突起構造の形成を抑制する。

【解決手段】誘電体パターンを素子領域の境界部に局所的に形成し、前記誘電体パターンをマスクにエッチングを行うことで素子分離領域を前記素子領域の境界部に形成し、その後、前記素子分離領域に隣接する素子領域に半導体膜の成膜を、前記誘電体パターンをマスクとした選択成長によりに実行する。

(もっと読む)

半導体装置

【課題】オン抵抗が低く集積化が可能な縦型パワーMOSトランジスタを提供すること。

【解決手段】本発明の縦型パワーMOSトランジスタは、半導体基板から酸化膜によって絶縁分離した単結晶領域を有する誘電体分離基板の単結晶領域表面に、ソース電極と、ドレイン電極と、ゲート電極とを配置し、単結晶領域が前記酸化膜に接する領域に低抵抗半導体領域を配置し、ソース領域を半導体表面に向けて突出した分離領域で挟み、この分離領域の上に配置した前記低抵抗半導体領域にドレイン領域を配置した。

(もっと読む)

半導体装置及びその製造方法

【課題】フリップチップ工法等による実装に於いてもSOI構造の支持基板の電位を安定的に固定可能にすると共に、低抵抗な基板コンタクトを形成する。

【解決手段】SOI構造の支持基板1と最上層配線13とを接続する複数の導電層と複数の配線層は、最上層配線13と共にチップ周縁部に沿って形成され、以ってトランジスタTrが形成されるトランジスタ形成領域TRの周囲に形成される。

(もっと読む)

半導体装置

【課題】基板浮遊効果の低減を図ったSOI構造の半導体装置を得る。

【解決手段】SOI層3の各トランジスタ形成領域は下層部にウェル領域が形成される部分酸化膜31によって分離される。NMOSトランジスタ間を分離する部分酸化膜31の下層にp型のウェル領域11が形成され、PMOSトランジスタ間を分離する部分酸化膜31の下層にn型のウェル領域12が形成され、NMOSトランジスタ,PMOSトランジスタ間を分離する部分酸化膜31の下層にp型のウェル領域11及びn型のウェル領域12が隣接して形成される。ボディー領域は隣接するウェル領域11に接している。層間絶縁膜4上に形成された配線層は、層間絶縁膜4中に設けられたボディーコンタクトを介してボディー領域と電気的に接続される。

(もっと読む)

半導体装置の製造方法

【課題】高温プロセスに弱い、シリコン・ゲルマニウムのような格子歪みを有する半導体層を持つ素子の分離方法を提供し、素子分離端でのリーク電流を低減し、信頼性の確保を可能にすることを目的としている。

【解決手段】素子分離端にゲート絶縁膜を介して直接ゲートがかからないような構造を形成することを特徴とする。具体的には、ゲート絶縁膜およびゲートの一部を形成した後にトレンチ構造を形成して絶縁膜を埋め込み、素子分離端とゲートの間にはゲート絶縁膜と埋め込んだ絶縁膜が存在するように形成する。さらに、ゲート電極の一部およびトレンチの側壁を同時に酸化することで酸化レートの差異からゲート電極の一部がトレンチ側壁よりも厚く酸化され、ゲート電極の一部が素子分離端にかからないようにすることでゲート電圧の影響を小さくし、素子分離端でチャネルが形成されないようにすることを特徴としている。

(もっと読む)

薄膜トランジスタ、それを備えた平板表示装置、前記薄膜トランジスタの製造方法、及び前記平板表示装置の製造方法

【課題】薄膜トランジスタ、それを備えた平板表示装置、前記薄膜トランジスタの製造方法、及び前記平板表示装置の製造方法を提供する。

【解決手段】ゲート電極と、ゲート電極と絶縁されたソース及びドレイン電極と、ゲート電極と絶縁され、ソース及びドレイン電極にそれぞれ接する有機半導体層を含み、有機半導体層は、少なくともチャンネル領域の周囲に、他部と少なくともその結晶構造が異なって変質した変性領域を有することを特徴とする薄膜トランジスタ。

(もっと読む)

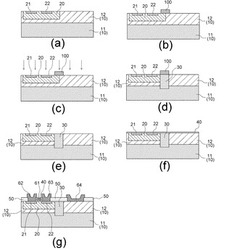

基板の製造方法および半導体装置の製造方法

【課題】第2半導体層の側壁に絶縁膜を形成して、第1半導体層の結晶方位を引き継いだエピタキシャル成長層を形成することで、結晶方位(100)の半導体層と結晶方位(110)の半導体層を同一基板上に結晶欠陥を抑制して形成することを可能とする。

【解決手段】第1半導体層11と絶縁層12と第2半導体層13とを順に積層した基板を用い、第2半導体層13上に酸化膜エッチング時の耐性と耐酸化性とを有するマスク層15を形成する工程と、第1領域のマスク層15から絶縁層12までを第1半導体層11上に残して第2領域の第1半導体層11を露出させる工程と、第1半導体層11表層と第2半導体層13の露出した側壁を酸化する工程と、マスク層15をエッチングマスクに用いて酸化層21を除去し、第1半導体層11を露出させる工程と、露出された第1半導体層11上にエピタキシャル成長層17を形成する工程とを備えた製造方法である。

(もっと読む)

1 - 12 / 12

[ Back to top ]