Fターム[5F032AA13]の内容

素子分離 (28,488) | 絶縁物を用いる分離 (9,448) | 素子領域側面を絶縁物で分離するもの (8,208) | 絶縁化分離 (375) | 選択酸化(LOCOS)分離 (337)

Fターム[5F032AA13]の下位に属するFターム

溝内を酸化するもの (76)

耐酸化マスクが直接基板と接しているもの (5)

多孔質酸化を用いるもの (2)

Fターム[5F032AA13]に分類される特許

1 - 20 / 254

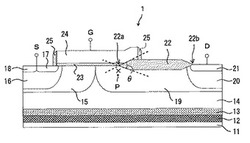

半導体装置およびその製造方法

【課題】LOCOS酸化膜端部の直下の電界集中が容易に緩和され、LOCOS酸化膜直下の半導体導電層の良好な耐圧および抵抗を実現することのできる半導体装置を提供する。

【解決手段】半導体装置(1)は、LOCOS酸化膜(22)の半導体基板の表面に対してラテラル方向に終端しているエッジ(22a、22b)の少なくとも一部(22a、22b)が、上面と下面とに15度以上30度以下の角度(θ)で挟まれて終端するプロファイルを有している。

(もっと読む)

CMOS垂直置換ゲート(VRG)トランジスタ

【課題】本発明は、CMOS垂直置換ゲート(VRG)トランジスタを提供する。

【解決手段】集積回路構造は平面に沿って形成された主表面を有する半導体領域及び表面中に形成された第1及び第2のソース/ドレインドープ領域を含む。絶縁トレンチが第1及び第2のソース/ドレイン領域間に形成される。第1のソース/ドレイン領域とは異なる伝導形のチャネルを形成する第3のドープ領域が、第1のソース/ドレイン領域上に配置される。第4のドープ領域が第2のソース/ドレイン領域上に形成され、第2のソース/ドレイン領域とは相対する伝導形をもち、チャネル領域を形成する。第5及び第6のソース/ドレイン領域が、それぞれ第3及び第4のドープ領域上に形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】隣接するSOI領域とバルクシリコン領域とが短絡することを防止する。

【解決手段】一つの活性領域内にSOI領域およびバルクシリコン領域が隣接する半導体装置において、それぞれの領域の境界にダミーゲート電極8を形成することにより、BOX膜4上のSOI膜5の端部のひさし状の部分の下部の窪みにポリシリコン膜などの残渣が残ることを防ぐ。また、前記ダミーゲート電極8を形成することにより、それぞれの領域に形成されたシリサイド層14同士が接触することを防ぐ。

(もっと読む)

半導体装置およびその製造方法

【課題】トレンチ構造の表面に不要な溝が形成されず、また、素子の面積効率を良好なものとすることができる半導体装置の製造方法の提供。

【解決手段】トレンチ内にポリシリコンが充填され、当該ポリシリコンの上部がシリコン酸化膜により覆われたトレンチ構造を有する半導体装置の製造方法であって、シリコン活性層の上面に第1のシリコン酸化膜が積層されてなる基板に異方性エッチングを行うことにより、上記第1のシリコン酸化膜の上面から上記シリコン活性層内に伸びるトレンチを形成するトレンチ形成工程と、上記トレンチの側壁全体を一体的に覆う第2のシリコン酸化膜を形成する側壁酸化膜形成工程と、上記第2のシリコン酸化膜の形成後に、上記トレンチ内にポリシリコンを充填する充填工程と、上記トレンチ内に充填したポリシリコンの上部露出面を酸化させてキャップを形成するキャップ形成工程と、を備える。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】露光光源として真空紫外光を用いるホトリソ技術のパターン解像限界より微細な拡散抵抗を製造することはできないから、高抵抗の拡散抵抗は実現できなかった。

【解決手段】一組の薄膜構造体の対向する間隔に、サイドウォール形成用の絶縁膜を形成する際に生じる空隙を利用して露光光源として真空紫外光を用いるホトリソ技術のパターン解像限界より微細な拡散抵抗を形成する。薄膜構造体を配線抵抗として利用すれば、これらを接続して設けることにより温度特性に優れる抵抗素子を構成することもできる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】SOIウェハに高耐圧素子の領域と低耐圧素子の領域とが形成された半導体装置であって、製造工程の中で、作業ステージに静電吸着したり、異常放電を引き起こしたりすることを抑えることができる半導体装置を提供する。

【解決手段】半導体層2と、半導体層2の上に形成された絶縁層3と、絶縁層3の上に形成された半導体の第1領域10aと、絶縁層3の上に形成され、第1領域10aに隣接する半導体の第2領域20と、絶縁層3の上に形成され、第1領域10aの側面を覆うように取り囲み、第1領域10aと第2領域20とが直接接続するように開口された開口部31aを有する絶縁体の第1絶縁壁30aとを具備する。

(もっと読む)

半導体装置

【課題】耐圧の向上が図られる半導体装置を提供する。

【解決手段】n-型半導体領域には、ドレイン領域となるn-型の拡散領域が形成されている。n-型の拡散領域の周囲を取囲むようにp型の拡散領域が形成されている。p型の拡散領域には、ソース領域となるn+型の拡散領域が形成されている。n-型の拡散領域の直下には、p-型の埋め込み層13が形成されている。n-型の半導体領域の領域には、高電位が印加されるn+型の拡散領域が形成され、そのn+型の拡散領域の表面上には電極が形成されている。電極とドレイン電極とは、配線20によって電気的に接続されている。配線20の直下に位置する部分に、p-埋め込み層13に達するトレンチ3aが形成されて、ポリシリコン膜81が形成されている。

(もっと読む)

半導体装置の製造方法およびCMOSイメージセンサーの製造方法

【課題】 半導体装置に発生するノイズを低減する

【解決手段】 シリコン基板100の第1部分110を覆い、シリコン基板100の第1部分110に隣接する第2部分120を覆わない窒化シリコン膜200をマスクとしてシリコン基板100を熱酸化することにより、酸化シリコン膜300を形成する。窒化シリコン膜200をマスクとして酸化シリコン膜300のバーズビーク部310の下へ斜めイオン注入を行うことにより、不純物領域121を形成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置を形成する。

【解決手段】薄膜領域TA1中に第1の素子領域、第2の素子領域および第1の分離領域を有し、厚膜領域TA2中に第3の素子領域、第4の素子領域および第2の分離領域を有する半導体装置を次のように製造する。(a)絶縁層1bを介してシリコン層1cが形成された基板を準備する工程と、(b)基板の第1の分離領域および第2の分離領域のシリコン層中に素子分離絶縁膜3を形成する工程と、を有するよう製造する。さらに、(c)薄膜領域TA1にハードマスクを形成する工程と、(d)ハードマスクから露出した、第3の素子領域および第4の素子領域のシリコン層上に、それぞれシリコン膜7を形成する工程と、(e)第3の素子領域および第4の素子領域のシリコン膜7間に、素子分離絶縁膜11を形成する工程と、を有するよう製造する。

(もっと読む)

半導体装置

【課題】半導体基板上へのVFETと他の種類の素子との混載が可能でありながら、半導体基板上に積層される半導体層の表面に大きな段差を有しない半導体装置を提供する。

【解決手段】P型シリコン基板2上には、酸化シリコンからなるボックス層3、N+型横方向導電層4およびN−型表面層5が積層されている。ボックス層3上には、N−型表面層5の表面からボックス層3に至る深さを有する、平面視環状のディープトレンチ6が形成されている。ディープトレンチ6およびボックス層3に取り囲まれるトランジスタ形成領域8は、その周囲から分離されている。このトランジスタ形成領域8において、N−型表面層5の表層部には、ソース領域14およびドレイン領域16が形成されている。またディープトレンチ6の側面に沿って、ドレイン領域16とN+型横方向導電層4とに接続されたN+型縦方向導電層17が形成されている。

(もっと読む)

半導体装置

【課題】より確実に画素間クロストークを抑制することが可能な、固体撮像素子を備える半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、半導体基板SUBの主表面上に配置された第1導電型の不純物層DPWと、不純物層DPW上に、第1導電型の不純物領域と第2導電型の不純物領域とが互いに接合する構成を含む光電変換素子と、光電変換素子を含む単位画素を構成し、光電変換素子と電気的に接続されるトランジスタM1〜M4とを備えている。平面視において光電変換素子の外周部の少なくとも一部には、内部に空隙AGが含まれ、光電変換素子と、光電変換素子に隣接する光電変換素子とを、互いに電気的に絶縁する分離絶縁層SIが配置されている。上記分離絶縁層SIは、第1導電型の不純物層DPWの最上面に接する。

(もっと読む)

半導体素子および作製方法

【課題】ソフトエラー率を有意に低下させる半導体素子およびその作製方法に関する。

【解決手段】半導体基板(100)には、第1の型の不純物でドープされた第1ウェル領域(104)の下に第1の型の第1ドープ領域(102)がある。第1ウェル領域は、第1ドープ領域と電気的に接続されている。第1ウェル領域と第1ドープ領域(102)との間に分離領域(206)を形成する。分離領域は第2ウェル領域と電気接続されている。分離領域および第2ウェル領域は、第1の不純物型と反対の型の第2の不純物型でドープされている。前記方法はさらに、第1ウェル領域内および分離領域下に第2ドープ領域を形成する工程をさらに有し得る。第1の型の不純物を有する第3ドープ領域を、分離領域の上に形成することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】 本発明は、より寄生容量の少ない素子の実現が可能な素子分離構造を有する半導体装置およびその製造方法を提供することにある。

【解決手段】 SOI基板上に形成される半導体装置は、素子分離領域に形成される素子分離溝(空洞)17と、半導体層11と支持基板13の間に介在する埋め込み絶縁層の一部に素子分離溝(空洞)17に接する空洞領域20を有する。

【効果】寄生容量を低減でき、また、素子の耐圧を高めることができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ソース領域とドレイン領域間のリーク電流の発生が抑制された、LOCOS分離構造の半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体基板の上部の一部に互いに離間して形成された第1導電型のソース領域及びドレイン領域と、ソース領域とドレイン領域に挟まれた領域を含んで半導体基板上に配置されたゲート絶縁膜と、半導体基板上にゲート絶縁膜と連続して配置された、ゲート絶縁膜よりも膜厚の厚いLOCOS絶縁膜と、ゲート絶縁膜上及びゲート絶縁膜周囲のLOCOS絶縁膜上に渡り連続的に配置された多結晶シリコン膜からなるゲート電極とを備え、ゲート電極のチャネル幅方向の端部である周辺領域におけるゲート閾値電圧がゲート電極の中央領域におけるゲート閾値電圧よりも高い。

(もっと読む)

半導体装置の製造方法

【課題】SON構造の半導体装置において、フォトリソグラフィー工程で高精度の位置合わせができ、プロセスラインの汚染を防止することができて、素子特性の劣化が防止され、信頼性の高い半導体装置の製造方法を提供する。

【解決手段】SON構造9上部のシリコン層32の段差18をアライメントマーク20として用いることによって、アライメントマーク20の形状崩れが防止されて、フォトリソグラフィー工程で高精度の位置合わせができるようになる。また、段差18が小さいためにフォトリソグラフィー工程で凹部へのレジストの残留やプロセス途中で発生するゴミの残留が防止され、プロセスラインの汚染が防止できる。その結果、素子特性の劣化が防止され、信頼性の高い半導体装置の製造方法を提供することができる。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板上の所定の領域内の窒化膜を、当該領域へのダメージを抑制しつつ選択的に除去することにより、信頼性の高い半導体装置を実現する。

【解決手段】半導体装置の製造方法は、半導体基板上の第1領域の全域を覆い、第2領域内の所定領域を覆う窒化膜を形成する工程と、窒化膜の全表面に酸化皮膜を形成する酸化皮膜形成工程と、この後、第1領域上を被覆し、第2領域上の所定の酸化膜形成対象領域を被覆しないパターンのレジスト膜を前記窒化膜上に形成する工程と、ふっ酸液によるウェットエッチングによって、酸化膜形成対象領域の窒化膜の表面に形成された酸化皮膜を選択的に除去して前記窒化膜を露出させるふっ酸エッチング工程と、レジスト膜を剥離する工程と、高温のリン酸液によって露出した窒化膜を除去する工程と、窒化膜が除去された酸化膜形成対象領域の基板表面に熱酸化による酸化膜を形成する工程とを含む。

(もっと読む)

半導体装置の製造方法

【目的】SON構造上に素子を形成する場合や繰り返しのエピタキシャル成長で素子を形成する場合に正確な位置あわせをすることができる半導体装置の製造方法を提供すること。

【解決手段】シリコンウェハ1のダイシングライン4などの無効領域の内部にSON構造11のアライメントマーク9を形成し、このアライメントマーク9を赤色レーザ(透過型レーザ)の反射光16の変化で認識することで、図示しないSON構造23上に素子を形成する場合や繰り返しのエピタキシャル成長で素子を形成する場合に正確な位置合わせをすることができる。

(もっと読む)

半導体装置

【課題】本発明は、SOIにおいて適したゲッタリング方法を適用して得られる半導体装置を提供する。

【解決手段】埋め込み酸化膜と、埋め込み酸化膜上に表面シリコン層を有するSOI構造を有する半導体装置において、埋め込み酸化膜上に、表面シリコン層を活性層として有するトランジスタと、素子分離絶縁膜を有し、素子分離絶縁膜上に容量が形成されており、素子分離絶縁膜に希ガス元素又は金属元素が含まれていることを特徴とする半導体装置とする。

(もっと読む)

半導体装置の製造方法

【課題】500keV〜3000keVのエネルギーイオン注入を行っても、目的とする領域に精度良く、不純物拡散領域を形成することができる半導体装置の製造方法を提供すること。

【解決手段】半導体基板10の表面に、イオン注入を行うための開口部42Aを持つレジストパターン42を形成する工程であって、開口部42Aの縁部42Bがイオン注入予定領域50の外縁部50Aよりも内側に位置するようにして、レジストパターン42を形成する工程と、レジストパターン42から露出した半導体基板10の表面の少なくとも一部に対して、ウエットエッチングを施す工程と、レジストパターン42をマスクとし、500keV〜3000keVのエネルギーイオン注入により、半導体基板10の深部に不純物拡散領域(例えばN−型不純物拡散領域12)を形成する工程と、を有する半導体装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI基板上に形成されたメサ分離構造のMOSトランジスタのトランジスタ特性のバラツキを低減する。

【解決手段】MOSトランジスタは、埋込み酸化膜3上に形成されたメサ型SOI層5と、メサ型SOI層5の上面中央部の上に形成されたゲート酸化膜7と、メサ型SOI層5の上面端部の上にゲート酸化膜7よりも厚い膜厚で形成された第1シリコン酸化膜9と、メサ型SOI層5の側面に第2シリコン酸化膜11を介して形成されたシリコン窒化膜からなる側壁膜13と、ゲート酸化膜7上に形成されたゲート電極15を備えている。

(もっと読む)

1 - 20 / 254

[ Back to top ]