Fターム[5F033QQ51]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エネルギービームの照射 (929)

Fターム[5F033QQ51]の下位に属するFターム

照射の対象 (905)

Fターム[5F033QQ51]に分類される特許

21 - 24 / 24

層形成方法、配線基板、電気光学装置、および電子機器

【課題】 下地層の段差を吸収して平坦な面を提供する絶縁層であって、コンタクトホールを有する絶縁層を、インクジェット法で形成すること。

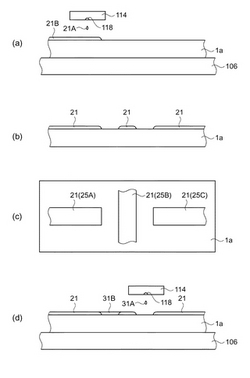

【解決手段】 インクジェット法を用いた層形成方法は、(a)第1レベル面上に位置する第1導電層21の側面が第1絶縁材料31Aで覆われるように、前記第1レベル面上に第1の濃度を有する前記第1絶縁材料31Aを吐出するステップと、(b)吐出された前記第1絶縁材料31Aを活性化または乾燥して、前記第1導電層21に接する第1絶縁層31Bを形成するステップと、(c)前記第1導電層21上と前記第1絶縁層31B上とに、前記第1の濃度よりも高い第2の濃度を有する第2絶縁材料を吐出するステップと、(d)吐出された前記第2絶縁材料を活性化または乾燥して、前記第1導電層21と前記第1絶縁層31Bとを覆う第2絶縁層を形成するステップと、を含んでいる。

(もっと読む)

半導体装置の製造方法

【課題】加工パターンの疎密に依存することなく面内均一に精度良好なパターン加工行うことが可能なエッチング工程を備えた半導体装置の製造方法を提供する。

【解決手段】基板11上にSiOCH系絶縁膜からなる被エッチング膜13を形成し、マスクパターン15上からのプラズマ処理を行う。これにより、マスクパターン15から露出している被エッチング膜13部分をSiO2化して改質部13bを形成する前処理を行う。次に、マスクパターン15およびSiOCH系材料からなる未改質部13aに対して選択的に改質部13bをエッチング除去する。

(もっと読む)

アクティブマトリクス基板、その画素欠陥修正方法及び製造方法

【課題】異物や膜残り等によるソース電極とドレイン電極との短絡、ドレイン電極やドレイン引出配線の断線及びTFT動作不良等による画素欠陥に対して、開口率を減少させることなく、点欠陥となる画素を容易かつ確実に修正することができ、液晶表示装置の歩留りを向上させることができるアクティブマトリクス基板を提供する。

【解決手段】基板上に、複数本の走査信号線及びデータ信号線と、信号線の交点に設けられ、ゲート電極が走査信号線に接続され、ソース電極がデータ信号線に接続された薄膜トランジスタと、上記薄膜トランジスタのドレイン電極又はドレイン引出配線に接続された画素電極とを備えるアクティブマトリクス基板であって、上記アクティブマトリクス基板は、データ信号線が少なくとも部分的に複線化された構造を有し、かつ修正用接続電極を備えるアクティブマトリクス基板である。

(もっと読む)

下にあるバリア層への多孔性低誘電率膜の接着を促進する手法

下にあるバリア層に対する多孔性低誘電率膜の接着は、その上にある多孔性低誘電率膜より炭素含量が低く、シリコン酸化物が豊富な中間層を形成することにより向上する。この接着層は、多数の手法のうち一つを単独で又は組み合わせて利用して形成されてもよい。一つのアプローチでは、接着層は、低誘電率材料の堆積直前にO2/CO2/などの濃酸化ガスを導入してSi前駆体を酸化することにより形成することができる。別のアプローチでは、α−テルピネン、シメン及びその他の酸素非含有有機物などの熱的に不安定な化学物質が、低誘電率膜の堆積前に除去される。また別のアプローチでは、ハードウェア又はシリコン非含有成分を導入する方式などの処理パラメータが変更されて、低誘電率膜の堆積の前に酸化物界面の形成を可能とすることもできる。さらに別のアプローチでは、吸収量、エネルギー又は熱アニール処理の使用などの電子ビーム処理のパラメータが制御され、バリアと低誘電率膜との間の界面で炭素種を除去することもできる。さらなるアプローチでは、低誘電率堆積の前に前処理プラズマが導入されバリア界面の加熱を増進することにより、低誘電率堆積ガスが導入され、低誘電率膜が堆積される時、薄い酸化物界面を形成することもできる。 (もっと読む)

21 - 24 / 24

[ Back to top ]