Fターム[5F038AR29]の内容

Fターム[5F038AR29]に分類される特許

1 - 11 / 11

半導体装置

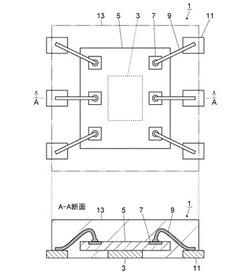

【課題】パッケージ応力に起因する回路部品の電気特性変動のバラツキによって出力信号が変動する内部回路について、パッケージ応力に起因する出力信号の変動を防止する。

【解決手段】半導体チップ5に形成された内部回路はその回路を構成する複数の回路部品の電気特性の変動のバラツキによって出力信号が変動するものである。チップタブ3の平面サイズは半導体チップ5の平面サイズよりも小さい。上方から見てチップタブ3の配置位置の全部が半導体チップ5の配置位置と重なっている。さらに、封止樹脂13に起因して半導体チップ5に加わる応力の大きさがチップタブ3上で均一になる位置関係でチップタブ3の周縁と上記半導体チップ5の周縁は間隔をもって配置されている。上記回路部品は半導体チップ5内部で上記チップタブ3上に配置されている。

(もっと読む)

半導体装置及びその試験方法

【課題】半導体チップに部分的に大きな電流が流れるのを抑制する技術を提供することを目的とする。

【解決手段】半導体装置は、ゲート電極5を有する半導体チップ1と、半導体チップ1の表面に設けられ、当該表面にかかる応力を検出する応力検出用素子7とを備える。そして、半導体装置は、応力検出用素子7で検出された応力に基づいて、ゲート電極5に印加される制御信号を制御する。また、平面視において半導体チップ1の中央部にかかる応力を検出する応力検出用素子7が、第1応力検出用素子7−1として設けられ、平面視において半導体チップ1の外周部にかかる応力を検出する応力検出用素子7が、第2応力検出用素子7−2として設けられることが好ましい。

(もっと読む)

半導体集積回路のレイアウト設計装置、レイアウト設計方法及びレイアウト設計プログラム並びに半導体集積回路装置の製造方法

【課題】半導体集積回路の設計TATの増大を防止する。

【解決手段】レイアウト設計装置は、パッケージに起因して半導体チップに加わるパッケージ応力の応力値の分布を示す応力分布データを読み込む応力分布データ読込み手段3と、半導体チップのチップレイアウトデータから素子レイアウトデータを抽出する素子レイアウトデータ獲得手段7と、半導体チップに搭載される各素子について応力値と素子の特性変動の関係を示した検量線データを保持する検量線データ保持部9と、応力分布データ、素子レイアウトデータ及び検量線データに基づいて各素子についてパッケージ応力による素子特性変動を算出する素子特性変動計算手段11と、素子特性変動を打ち消すように素子レイアウトデータを補正する素子レイアウト補正手段13と、補正後素子レイアウトデータを用いてチップレイアウトデータを補正するチップレイアウト補正手段と、を備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】抵抗値の調整が容易な半導体装置及びその製造方法を得る。

【解決手段】シリコン基板上に所定間隔で形成された配線層と、前記シリコン基板上及び前記両配線層上に形成されたパッシベーション膜と、前記両配線間の前記パッシベーション膜上に形成された抵抗体層と、前記抵抗体層上に形成された、各配線層と抵抗体層とを導通する電極層とを備え、前記抵抗体層上に、前記両電極層間における該抵抗体層の平面的な大きさを決める絶縁バリア層を形成した。

(もっと読む)

ICチップの基板が薄くなった箇所を検出する装置

【課題】ICチップの基板が薄くなった箇所を検出する装置を提供する。

【解決手段】ICチップの基板が薄くなった箇所を検出する装置は、基板の活性領域に、ホイートストン・ブリッジとして接続された、棒形状の分散された複数の抵抗を備え、ブリッジの第1の対向する抵抗の組は、第1の方向に向いており、ブリッジの第2の対向する抵抗の組は、第2の方向に向いており、第1及び第2の方向は、基板が薄くなった箇所がブリッジの不均衡値を変化させる方向である。

(もっと読む)

半導体装置

【課題】 抵抗部と分離部の間のリーク電流を抑える技術を提供する。

【解決手段】 半導体装置100は、半導体基部10と分離部20と抵抗部30と電流補償部40を備えている。抵抗部30は、高電位側に接続される高電位側接続部位30Hと、低電位側に接続される低電位側接続部位30Lを有する。分離部20は、抵抗部30の高電位側接続部位30Hに隣接する第1部位20Hが高電位側に接続され、抵抗部30の低電位側接続部位30Lに隣接する第2部位20Lが低電位側に接続される。電流補償部40は、第1部位20Hと第2部位20Lの間の少なくとも一部に配置されている。電流補償部40と分離部20の間の抵抗値は、抵抗部30と分離部20の間の抵抗値よりも小さい。

(もっと読む)

半導体装置

【課題】 半導体パッケージの封止樹脂から半導体チップに対して応力がかかっても、特性値のシフトが少ない半導体装置を提供する。

【解決手段】 半導体チップの一辺に対し垂直方向のチャネルを形成するMOSトランジスタと水平方向のチャネルを形成するMOSトランジスタを組み合わせることで、応力に起因する特性値変動を相殺し、特性値のシフトが少ない半導体装置とする。

(もっと読む)

半導体装置及びその製造方法

【課題】SMT膜のレイアウトに関わらず、抵抗値のバラツキが小さく良好な特性を示す抵抗素子を有し、高速に動作可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、半導体基板11上に形成された素子分離領域12と、素子分離領域に取り囲まれたp型領域を有する活性領域13A及びn型領域を有する活性領域13Cと、p型領域を有する活性領域13A上に形成されたn型ゲート電極16Aを有するn型MOSトランジスタと、n型領域を有する活性領域13C上に形成されたp型ゲート電極16Cを有するp型MOSトランジスタと、素子分離領域12上に形成されたp型抵抗体16Dとを備えている。p型抵抗体16Dの内部応力は、p型ゲート電極16Cの内部応力よりも大きい。

(もっと読む)

半導体装置

【課題】本発明は、ボンディングによって圧力を加えても抵抗値が変動しない半導体装置を提供することを目的とする。

【解決手段】N形半導体からなる第1の抵抗素子20及びP形半導体からなる第2の抵抗素子22は、直列接続されている。集積回路12に電気的に接続された電極14上にはバンプ18が設けられている。第1の抵抗素子20は、バンプ18とオーバーラップして第1の抵抗値を有する第1のオーバーラップ部24を含む。第2の抵抗素子22は、バンプ18とオーバーラップして第2の抵抗値を有する第2のオーバーラップ部26を含む。第1のオーバーラップ部24は、受ける荷重に比例して第1の抵抗値が低下する性質を有する。第2のオーバーラップ部26は、受ける荷重に比例して第2の抵抗値が増加する性質を有する。第1の抵抗値の低下率は、第2の抵抗値の増加率のx倍である。第1の抵抗値は、第2の抵抗値の1/x倍である。

(もっと読む)

抵抗素子およびそれを用いた半導体集積装置

【課題】 十分な精度の抵抗値が得られる抵抗素子およびそれを用いた半導体集積装置を提供する。

【解決手段】 半導体基板11と、半導体基板11の主面に絶縁膜12を介して形成された導電体13と、導電体13上に絶縁膜14を介して形成されたポリシリコン抵抗体15と、ポリシリコン抵抗体15上に絶縁膜16を介して形成された導電体17と、導電体13、17に電圧を印加する手段とを有する。

ポリシリコン抵抗体15に電界を印加してストレスを生じさせ、ピエゾ抵抗効果により抵抗値が高い方向または低い方向にシフトさせる。

(もっと読む)

半導体装置

【目的】 パッケージ化等による応力がかかっても、初期の抵抗値を保持できる半導体装置やブリーダ抵抗回路においては正確な分圧比を保持でき、ブリーダ抵抗回路を用いた例えばボルテージディテクタ、ボルテージレギュレータ等の半導体装置を小さなチップ面積で提供することを目的とする。

【構成】 P型の半導体薄膜で形成されたP型薄膜抵抗体と、N型の半導体薄膜で形成されたN型薄膜抵抗体とから構成し、応力がかかった場合の抵抗値変化を防止した。さらに、P型薄膜抵抗体と、N型薄膜抵抗体とを上下に接触させて積層、又は左右に接触させて配置した構造をとることと、ブリーダ抵抗回路における、1単位となる抵抗値を規定する抵抗体の一端のコンタクト領域は、P型薄膜抵抗体と、N型薄膜抵抗体とで同一とすることによって、ブリーダ抵抗回路の占有面積の縮小を図ることができるようにした。

(もっと読む)

1 - 11 / 11

[ Back to top ]