Fターム[5F038BB07]の内容

Fターム[5F038BB07]に分類される特許

1 - 20 / 141

半導体装置

半導体集積回路

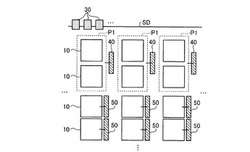

【課題】回路規模を低減しつつ任意の論理を実現可能な半導体集積回路を提供する。

【解決手段】実施形態の半導体集積回路は、第1論理ブロックを少なくとも1つ含む第1回路群と、第1論理ブロックよりも多い数の第2論理ブロックを含む第2回路群と、入力データを第1論理ブロックまたは第2論理ブロックへ入力する機能、および、第1論理ブロックまたは第2論理ブロックから出力される出力データを外部へ出力する機能を有する入出力部とを含む。第1回路群は、第1スイッチブロックと、第1電源制御回路とを有する。第1電源制御回路は、第1回路群に含まれる第1論理ブロックおよび第1スイッチブロックに対する電力の供給および停止を共通に制御する。第2回路群は、第2スイッチブロックと第2電源制御回路とを有する。第2電源制御回路は、第2回路群に含まれる論理ブロックおよび第2スイッチブロックに対する電力の供給および停止を共通に制御する。

(もっと読む)

電源制御装置、電源制御装置の制御方法、およびプログラム

【課題】多様な信号規格の処理に対応する半導体集積回路において、様々な周期性の違いに伴いタイミングと時間幅が変わるアイドル状態に対応した電源制御を適用し、消費電力を低減する。

【解決手段】処理状態と待機状態とを周期的に繰り返して処理を行う半導体集積回路の電源ドメインを制御する電源制御装置であって、待機状態の発生期間および発生間隔を含む周期的特徴情報を取得する周期情報取得部103と、電源ドメインが待機状態における待機電圧から半導体集積回路が動作可能となる電圧へ復帰するまでに要する復帰時間と対応付けられた待機電圧候補から、発生期間よりも復帰時間が短くなる待機電圧を電源制御情報として設定する電源制御情報設定部104と、電源制御情報に従って発生期間における電源ドメインの待機電圧を制御する電源制御部105とを備える。

(もっと読む)

半導体装置

【課題】抵抗体とヒューズ素子が並列に接続された半導体装置において、ヒューズ素子切断時に抵抗体への損傷がなく、抵抗体とヒューズ素子とを積層すること。

【解決手段】半導体基板上に第1の絶縁膜を介して形成された抵抗体を設け、抵抗体の上に第2の絶縁膜を介して形成された遮光層を設け、遮光層の上に第3の絶縁膜を介して形成されたヒューズ素子のヒューズ部を有し、抵抗体と遮光層とヒューズ部を重畳した半導体装置とする。

(もっと読む)

半導体装置

【課題】トリミング回路を備えた半導体装置において、内部電源の電圧レベルを半導体装置の外部から適切に制御できるようにすること。

【解決手段】半導体装置は、複数のレベルの間で遷移する第1のテストモード信号を受信し、第1のテストモード信号の遷移に応じてカウント動作を行うバイナリカウンタ回路と、バイナリカウンタ回路の所定のビットの値を示すビット信号、および、バイナリカウンタ回路のカウント動作を制御する第2のテストモード信号を受信し、ビット信号および第2のテストモード信号に応じて、第1のテストモード信号を遷移させるか否かを制御する制御回路と、バイナリカウンタ回路のカウント値に応じて、複数の基準電位の中からいずれかの基準電位を選択するセレクタと、セレクタにより選択された基準電位に応じて、内部電源を発生する内部電源発生回路と、を備える。

(もっと読む)

半導体装置

【課題】次段回路で基準電圧として用いられる定電圧を生成する基準電圧回路について、ツェナーダイオードの製造ばらつき等が出力定電圧の温度特性に及ぼす影響を低減する。また、当該出力定電圧の温度特性の平坦性を向上する。また、回路規模の増大を抑制しつつ優れた起動性、応答性および安定性を実現する。

【解決手段】分圧回路332は直列接続されたダイオード304,306,308に対して並列的に設けられている。分圧回路332の低電位側接続点yの電圧は正の温度特性を示し、分圧回路332の高電位側接続点xの電圧は負の温度特性を示す。分圧点zにおける定電圧V0が平坦な温度特性を持つように分圧抵抗316,318の抵抗値が設定されている。分圧回路332の分圧点zは、フィードバックループに接続されることなく次段回路へ接続されることにより、次段回路へ定電圧V0を出力する。

(もっと読む)

半導体装置

【課題】電圧生成回路を備えた半導体装置において、電圧生成回路の電荷供給能力が十分でない場合であってもチャージシェアを引き起こすことなく、電圧生成回路の出力電圧を従来よりも高精度に検出できるようにする。

【解決手段】半導体装置1は、電圧生成回路11と、第1のスイッチSW2と、充電回路20とを備える。電圧生成回路11は、電圧を生成して出力し、生成する電圧の大きさを調整する機能を有する。第1のスイッチSW2は、オン状態のときに互いに導通する第1および第2の導通端子を有し、第1の導通端子が電圧生成回路11の出力ノードと配線を介して接続される。充電回路20は、第1のスイッチSW2の第2の導通端子に接続された配線を充電する。

(もっと読む)

半導体装置

【課題】回路特性を調整するためのトリミング時間を短縮する。

【解決手段】切断ポイントが座標Y1に配列されたラダーヒューズLFAと、切断ポイントが座標Y2に配列されたラダーヒューズLFBとを備える。回路特性を調整するための補正データが第1の範囲内にある場合はラダーヒューズLFA,LFBの両方に対してトリミング動作を行い、回路特性を調整するための補正データが第2の範囲内にある場合はラダーヒューズLFAに対してトリミング動作を行うことなく、ラダーヒューズLFBに対してトリミング動作を行う。これにより、補正データが第2の範囲内である場合には、ラダーヒューズLFAに対してレーザ照射する必要がない。このため、例えば量産段階で必要となる調整範囲をラダーヒューズLFBに割当てれば、1回のスキャンでトリミングを完了することが可能となる。

(もっと読む)

半導体装置及びその制御方法

【課題】様々な導通状態にある複数の電気ヒューズを有する半導体装置において、複数の電気ヒューズによりプログラミングされた結果を誤判定なく読み出すことのできる半導体装置及び半導体装置の制御方法を提供する。

【解決手段】其々がプログラム状態又は非プログラム状態である複数のヒューズ素子と、複数のヒューズ素子のプログラム状態又は非プログラム状態に対応する判定結果信号FLDa,FLDbを其々出力する複数のヒューズ判定回路92a,92bと、第1のタイミング信号LOAD_ENDを共通に受け、第1のタイミング信号LOAD_ENDに同期して複数の判定結果信号FLDa,FLDbを其々ラッチ及び出力する複数のラッチ回路93a,93bとを備える。

(もっと読む)

バンドギャップ型基準電圧発生回路

【課題】バンドギャップ型基準電圧発生回路において、高温における寄生ダイオードのリーク電流の影響を制御して、基準電圧の温度特性の向上を図る。

【解決手段】NPN型BIPトランジスタQ1の寄生ダイオードD1とは別に、i個(iは1以上の自然数)の温度特性制御ダイオードD31〜D3iをNPN型BIPトランジスタQ1のコレクタに接続する。温度特性制御ダイオードD31〜D3iは、Pチャネル型MOSトランジスタM1,M2からなるカレントミラー回路を介して、寄生ダイオードD21〜D2Kのリーク電流の増加による基準電圧Vrefへの影響をキャンセルするように作用する。

(もっと読む)

半導体装置

【課題】トリミングデータによって調整可能な基準電圧発生回路を備えた半導体装置において、電源が立上がるまでの基準電圧のばらつきの影響を受けないようにする。

【解決手段】半導体装置10において、基準電圧生成部1は、外部電源電圧VCCに基づいて、トリミングデータTRM1に応じて調整された第1の基準電圧V1*およびこのトリミングデータTRM1に依存しない第2の基準電圧V2を生成する。不揮発性メモリ3は、第1の基準電圧V1*に基づく電圧によって動作し、上記のトリミングデータTRM1を記憶する。パワーオンリセット回路5は、電源立上げ時に外部電源電圧VCCが第2の基準電圧V2の定数倍に達したときにリセット信号の論理レベルを切替える。制御回路6は、リセット信号の論理レベルの切替に応答して、不揮発性メモリ3に記憶された上記のトリミングデータTRM1を基準電圧生成部1に読込ませる。

(もっと読む)

集積回路装置及び電子機器

【課題】センサーデバイスからの検出信号の精度の高いA/D変換を実現できる集積回路装置及び電子機器等の提供。

【解決手段】集積回路装置は、電源電圧VDDAを生成する電源回路60と、電源回路60から電源電圧VDDAが供給され、供給された電源電圧VDDAに基づいて動作し、電源電圧VDDAにより規定されるA/D変換範囲で、センサーデバイス30からの検出信号に対応する信号についてのA/D変換を行うA/D変換器ADCと、電源回路60から電源電圧VDDAが供給され、供給された電源電圧VDDAをセンサーデバイス30に供給する電源端子PVDAを含む。

(もっと読む)

半導体装置のトリミング方法、及びトリミング制御回路

【課題】スイッチ素子の製造バラツキを排除し、より均一で確実な溶断が行える半導体装置のトリミング方法、及びトリミング制御回路を提供すること。

【解決手段】電位が異なる第1電源(電源端子c)と第2電源(接地端子d)との間にて直列接続された第1スイッチ素子S1〜S3およびフューズF1〜F3を内蔵した半導体装置101における第1スイッチ素子S1〜S3をオン制御することでフューズF1〜F3に電圧を印加してフューズF1〜F3を溶断する半導体装置101のトリミング方法であって、第1スイッチ素子S1〜S3をターンオン制御することにより、第1電源(電源端子c)からフューズF1〜F3を溶断させない第1電圧値を所定時間印加するステップと、第1電圧値の印加が完了した後、第1電源(電源端子c)からフューズF1〜F3を溶断させる第2電圧値を印加するように切り替えるステップと、を含む。

(もっと読む)

可変抵抗回路を備えた半導体集積回路

【課題】トリミング用のスイッチ素子のオン抵抗によって抵抗値に誤差が生じることがなく、電源電圧依存性や温度依存性もなくレイアウト面積も小さい可変抵抗回路を備えた半導体集積回路を提供すること。

【解決手段】複数の抵抗を直列に接続した抵抗回路と、複数の抵抗の直列に接続する数を選択する複数のスイッチ素子を有する選択回路と、スイッチ素子のオン抵抗値を制御する制御回路と、を備え、制御回路はスイッチ素子のオン抵抗値と抵抗回路の抵抗の抵抗値とが所定の比になるように制御する、構成とした。

(もっと読む)

半導体装置

【課題】電源投入時において誤って設定されたレベル調整回路の出力を、テストモードを用いて初期化し、目標レベルである正規の設定値へと高速に調整する半導体装置を提供する。

【解決手段】テストモード時に外部から入力されるテストデータを保持する複数のラッチ回路2と、ラッチ回路2が保持するテストデータが入力され、テストデータの論理の組合せによりコードを発生するデコード回路3と、ラッチ回路2が保持するテストデータの論理レベルに変化があった時、予め設定された期間の間、HレベルまたはLレベルとなるゲート駆動信号UPDN_B<i>、UPDN_T<i>、UPDN_T<i−1>を出力し、電流供給回路(引き下げ回路8、引き上げ回路9)を駆動する遷移検出回路7と、を備える。

(もっと読む)

半導体回路装置

【課題】

半導体回路装置に内蔵された内部回路に供給する動作電圧について、内部回路に対する動作モードの変更に伴う動作電圧の安定期間を待つことなく、動作モード変更時でも動作開始時刻を速くすることが可能な構成を有する半導体回路装置を提供する。

【解決手段】

上記の課題を解決するため、外部電源から電圧供給を受ける電源線と、回路群と、回路群の動作電圧が異なる複数の動作モードに応じた制御信号を出力する制御回路と、回路群と、電源線とに電気的に接続し、回路群に前記電源線の電圧以下の電圧を供給する電源供給回路と、を備え、動作モードの変更後において、高い動作電圧を回路群が必要とする場合、電源供給回路は、高い動作電圧より高い電圧を回路群に供給した後、制御信号に応じて、変更後の動作モードに必要な動作電圧を供給する半導体回路装置を提供する。

(もっと読む)

分圧回路及び半導体装置

【課題】検出精度がよく、かつ回路規模、チップサイズの縮小させた分圧回路及び半導体装置を提供すること。

【解決手段】2進コードに従って抵抗値が重み付けされて形成される第1抵抗回路と、同じ2進コードに従って抵抗値が重み付けされて形成される第2抵抗回路と、同じ2進コードに従って抵抗値が重み付けされ、重み付けのビット数が最大である第3抵抗を有する第3抵抗回路と備え、第3抵抗の両端のいずれかを2つのトランスミッションゲートで択一的に出力端子と接続する構成とした。

(もっと読む)

半導体装置及び半導体装置の試験方法

【課題】テストコストの低減及び不良解析の精度向上を図った半導体装置を提供する。

【解決手段】半導体装置100は、被調整電源13の出力である被調整電源出力電圧Vaを調整するトリミングコードTRMC(=TRMC1)を変化させながら発生し、被調整電源出力電圧Vaが入力電圧Vinに対応する値となった場合、電圧供給回路25の出力電圧Voutの基準電圧Vrefと同じ電圧レベルに出力変更し、入力初段回路へ供給する。また、トリミングコードTRMCをトリミングコード記憶回路16に記憶し、記憶したトリミングコードTRMC(=TRMC2)に基づき被調整電源出力電圧Vaを設定する。

(もっと読む)

基準電圧発生回路及びそれを用いたアナログ回路

【課題】複数の基準電圧を電圧選択回路で切り替えて出力する基準電圧発生回路において、基準電圧が入力されるアナログ回路の積分非直線性(INL)の精度を向上させる。

【解決手段】基準電圧発生回路1は、抵抗値が調節可能であり、一端が第1電源V1に接続される第1可変抵抗回路RTと、抵抗R1,R2,R3が直列に接続され、一端が第1可変抵抗回路RTに接続された直列抵抗回路と、抵抗値が調節可能であり、一端が上記直列抵抗回路に接続され、他端が第2電源GNDに接続される第2可変抵抗回路と、第1可変抵抗回路RTと直列抵抗回路の間の端子N4の電圧、直列抵抗回路を構成する抵抗R1,R2,R3の間の端子N2,N3の電圧、又は直列抵抗回路と第2可変抵抗回路RBの間の端子N1の電圧のいずれかを選択して出力する電圧選択回路3と、を備えている。

(もっと読む)

デジタル回路部への供給電圧を決定する方法、デジタル回路部への供給電圧を設定する方法、電子機器及び供給電圧決定装置

【課題】一般的なデジタル回路において消費電力を削減させることを可能とする新たな手法を提案すること。

【解決手段】携帯型電話機100のプロセッサーであるホストCPU130は、規定の入力テスト信号をデジタル回路部であるGPS受信部110に印加し、当該入力テスト信号に応答するGPS受信部110からの出力信号に基づいて、GPS受信部110の動作を検査する。また、GPS用可変電圧部190に電圧指示信号を出力することでGPS受信部110に供給する検査用電圧を変更する。そして、GPS受信部110の検査と、検査用電圧の変更とを繰り返し実行して、GPS受信部110への供給電圧を決定する。

(もっと読む)

1 - 20 / 141

[ Back to top ]