Fターム[5F038DF04]の内容

半導体集積回路 (75,215) | 集積回路機能及び回路ブロック構成 (8,544) | 特定機能回路(単一機能) (5,304) | CPU、マイクロプロセッサ (715)

Fターム[5F038DF04]に分類される特許

1 - 20 / 715

半導体装置

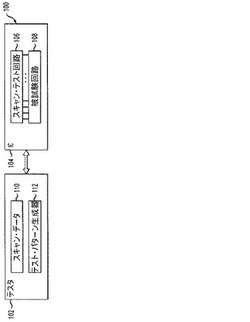

スキャン・チェーン用動的クロック領域バイパス

【課題】スキャン・テスト回路およびスキャン・テスト回路を使用して試験を受けるさらなる回路を備える集積回路を提供すること。

【解決手段】スキャン・テスト回路は、それぞれ別個のクロック領域に関連した複数のサブチェーンを有する少なくとも1つのスキャン・チェーン、および1つまたは複数のサブチェーンを選択的にバイパスするように構成されたクロック領域バイパス回路を備える。スキャン・チェーンは、スキャン・シフト・モードの動作において、サブチェーンを全部よりは少なく含む直列シフト・レジスタを形成するように構成可能であり、サブチェーンの少なくとも残りの1つが、スキャン・シフト・モードにおいて直列シフト・レジスタの部分でないように、クロック領域バイパス回路によりバイパスされる。特定のクロック領域に関連するスキャン・チェーンの部分を選択的にバイパスすることにより、クロック領域バイパス回路は、スキャン・テスト期間の試験時間と電力消費を減らす役割を果たす。

(もっと読む)

給電電圧の変動を吸収する電源構造を持つ集積回路

【課題】給電ユニット(エナジーハーベスティングデバイス)に改変を加えること無く、不安定な給電電圧、特に、低い給電電圧ででも正常に動作する、回路ユニットを含む集積回路を提供する。

【解決手段】本発明に係る集積回路は、外部電源に接続された第1の電源リングで囲まれた第1の回路ブロックと、第1の電源リングを介して前記外部電源に接続された第2の電源リングで囲まれた第2の回路ブロックとを含み、第1の回路ブロック内の半分以上が同期回路で構成され、第2の回路ブロック内の半分以上が非同期回路で構成されている。

(もっと読む)

半導体装置

【課題】部分的な経年劣化の予兆を早期に発見することができる半導体装置を提供する。

【解決手段】LSI1は、複数のモジュールと、複数の遅延モニタを含む遅延モニタ群15とを備える。各遅延モニタは、複数段のゲート素子を有するリングオシレータを含む。各遅延モニタは、ゲート素子の遅延時間を測定する。CPU#0は、遅延モニタによって測定された遅延時間に基づいて、遅延モニタの近傍のモジュールの経年劣化を判定する。

(もっと読む)

半導体装置

【課題】直流電源配線に電流が流れたか否かを検出可能な回路を備えた半導体装置を提供する。

【解決手段】半導体装置において、駆動回路BLDU,BLDD,BLBDU,BLBDDは、電流磁界またはスピン注入によってトンネル磁気抵抗素子TMR,TMRBを第1の磁化状態に初期設定するために、制御信号線BL,BLBに直流電流を流す。電源配線DLは、トンネル磁気抵抗素子TMR,TMRBに近接して設けられる。ここで、トンネル磁気抵抗素子TMR,TMRBは、電源配線DLに直流電流が流れるときに生じる電流磁界によって第2の磁化状態に変化する。センスアンプ10は、トンネル磁気抵抗素子TMR,TMRBが第1の磁化状態から第2の磁化状態に変化したか否かを判定するために、制御信号線BL,BLBを介してトンネル磁気抵抗素子TMR,TMRBに流れる電流を検出する。

(もっと読む)

半導体集積回路

【課題】クランプ電圧を正確な値に設定できる半導体集積回路を提供することを目的とする。

【解決手段】第1の電圧である電源を供給されて定電流を発生する定電流部60と、定電流部60で発生された定電流を供給されて第1の電圧より低い第2の電圧を発生し、第1の電圧の電源を第2の電圧にクランプするクランプ部71と、クランプ部71でクランプされた電源を供給されて基準電圧を発生する基準電圧発生部72とを有し、クランプ部71は、ゲートとドレインに接続され縦型接続された複数段のMOSトランジスタM11−1〜M11−nである。

(もっと読む)

半導体装置

【課題】寿命が長い半導体装置を提供する。

【解決手段】このLSIは、2つのCPU1,2と、CPU1,2のうちのいずれか1つのCPUを示す論理レベルのデータ信号が書き込まれた記憶回路4と、リセット信号REが非活性化レベルにされてLSIのリセットが解除された場合、記憶回路4の記憶データの論理レベルに対応するCPUのみに電源電圧を供給するとともに、記憶回路4の記憶データを現在の論理レベルと異なる論理レベルのデータ信号に書き換える制御回路3,5とを備える。したがって、故障の検知や、厳密なタイミング制御を必要とせずに、CPUの長寿命化を図ることができる。

(もっと読む)

半導体チップ

【課題】チップ面積が小さく低コストで誤動作が発生し難い半導体チップを提供する。

【解決手段】半導体チップ1をパッケージ3に搭載する場合は80個のパッドPAをパッケージ3の80個の端子TAに接続し、半導体チップ1をパッケージ5に搭載する場合は100個のパッドPA,PB,PCをパッケージ5の100個の端子TAに接続する。半導体チップ1の内部回路は、電極E1,E2が絶縁されている場合は80端子のマイクロコンピュータ4として動作し、電極E1,E2がボンディングワイヤWの端部によって短絡されている場合は100端子のマイクロコンピュータ4として動作する。したがって、パッケージの端子数を設定する専用パッドが不要となる。

(もっと読む)

プロセッサシステム及び半導体集積装置

【課題】処理速度の低下を最低限に抑えかつ従来技術に比較して消費電流の変動を抑える。

【解決手段】プロセッサシステム1は、プログラムメモリ2に格納された複数の命令コードを任意の順序で連続して実行する。テーブルメモリ53は、各命令コードと各命令コードの実行時の消費電流量との関係を示す消費電流量テーブルを格納する。電流変動抑制回路51は、消費電流量テーブルを参照して、連続する2つの命令コードの実行時の消費電流量の差の大きさが所定のしきい値以下になるように、上記連続する2つの命令コードのうちの一方の命令コードの実行時にプロセッサシステム1に流す補正消費電流を算出し、上記算出された補正消費電流量の補正消費電流をプロセッサシステム1に流すように、補正消費電流発生回路54を制御する。

(もっと読む)

メモリ電圧制御装置およびメモリ電圧制御方法

【課題】メモリを低電圧で制御して省電力制御を図ることおよびエラーの発生を防止することを改善できるメモリ電圧制御装置およびメモリ電圧制御方法を提供する。

【解決手段】メモリ電圧制御装置10およびメモリ電圧制御方法は、デバイス13,14と、デバイス13,14の異常を検出する電気機器11と、を備え、電気機器11は、デバイス13,14の異常を検出した時に、デバイス13,14に対して動的または静的に駆動電圧を昇圧する制御を行う。

(もっと読む)

半導体装置

【課題】セキュリティ情報を格納した領域への物理的な破壊攻撃を、従来よりも簡単な手法で検知する。

【解決手段】半導体装置1において、第1の機能モジュール3は、正常に動作しているか否かのテスト対象となる。第2の機能モジュール2は、第1の機能モジュール3にテストデータを出力し、テストデータに応じて第1の機能モジュールから出力された出力信号が正常なデータパターンと一致するか否かを判定する。第3の機能モジュール7は、耐タンパ性を必要とする。シールド配線SLは、基板に対して垂直方向から見たときに第3の機能モジュール7が設けられた領域を覆うように設けられ、その両端部は第1の機能モジュール3と接続される。シールド配線SLが断線しているとき、上記の出力信号は正常なデータパターンと一致しなくなる。

(もっと読む)

半導体装置

【課題】データの誤書換を防止することが可能な低消費電力の半導体装置を提供する。

【解決手段】マイクロコンピュータ1は、電源電圧VCCが正常範囲から外れた場合にリセット信号REを出力する電圧検出器2と、各々がデータを不揮発的に記憶する複数のメモリセルを含むメモリアレイ5と、イレーズコマンドまたはプログラムコマンドに応答して、電圧検出器2の応答時間TR以上の保留時間TSだけ経過した後にデータのイレーズまたはプログラムを実行し、リセット信号REに応答してリセットされる制御部7とを備える。したがって、電圧検出器2の応答時間TRが長い場合でも、データの誤書換を防止できる。

(もっと読む)

半導体集積回路装置

【課題】部品点数を増加させることなく、低コストでかつ効率的に半導体集積回路装置の高信頼性化を実現させる。

【解決手段】ユーザプログラムの実行時において、周期タイマ2からタイマカウンタ信号が出力されると、CPUコア6,7はASEメモリ3に格納されたテスト用プログラムを実行し、そのチェック結果をトレースメモリ11に格納する。デバッグ回路10は、トレースメモリ11に格納されたチェック結果のコンペア処理を行い、CPUコア6,7が正常か否かを判定する。正常の場合、CPUコア6,7は、再びユーザプログラムを実行する。異常の場合、デバッグ回路10は、状態信号をシステム停止回路12に出力する。この状態信号を受けると、システム停止回路12は、動作制御信号をCPUコア6,7にそれぞれ出力し、半導体集積回路装置1の再起動処理が行われる。

(もっと読む)

半導体集積回路

【課題】SOI型の半導体集積回路において電源遮断時の低消費電力及び電源供給時の動作性能向上に資することができる電源遮断制御を可能にする。

【解決手段】本発明に係る半導体集積回路は、第1電源スイッチと、前記第1電源スイッチに直列接続される論理回路を有する。前記論理回路は、順序回路(FF1,FF2)及び組み合わせ回路(LOG1,LOG2)を含み、前記第1電源スイッチと前記組み合わせ回路との間に第2電源スイッチが接続される。第1モードにおいて前記第1電源スイッチをオフ状態に制御し、前記順序回路及び前記組み合わせ回路を非通電状態にし、第2モードにおいて前記第1電源スイッチをオン状態に維持し且つ前記第2電源スイッチをオフ状態に制御し、前記順序回路を通電状態、前記組み合わせ回路を非通電状態にする電源スイッチ制御回路を有する。

(もっと読む)

半導体集積回路装置

【課題】電源遮断領域の信号配線の自由度を低下させないで、電源遮断用スイッチから電源遮断領域に至る電圧伝達経路における電圧降下を抑える。

【解決手段】半導体集積回路装置(80)は、電源遮断用スイッチ(90)と電源遮断領域(763)とが形成された半導体チップ(22)とを含む。半導体チップは基板(21)に結合される。上記電源遮断領域の外側に上記電源遮断用スイッチを配置することで、電源遮断領域内の配線チャネル数の低減を回避する。そして上記基板には、上記半導体チップ内から上記電源遮断用スイッチを介して上記半導体チップの外に伝達された電源電圧を再び上記半導体チップ内に伝達して上記電源遮断領域へ給電するための基板側給電路(30)を形成することで、上記電源遮断用スイッチと上記電源遮断領域との間の電圧降下を抑える。

(もっと読む)

縦構造キャパシタを備える半導体装置

【課題】縦構造キャパシタの剥離を防止し、チップサイズの増加を抑制した半導体装置を提供する。

【解決手段】半導体装置には、第1の回路の機能素子として使用される第1の縦構造キャパシタと、第2の回路の機能素子として使用され、第1の縦構造キャパシタよりも容量値の大きい第2の縦構造キャパシタと、が含まれている。半導体装置では、第1の縦構造キャパシタを、第2の縦構造キャパシタに隣接、又は、包含させるようにレイアウトする。

(もっと読む)

半導体装置

【課題】複数の回路ブロックの特性を正確に一致させる。

【解決手段】例えば、端子31A,31Bと、これら端子間に設けられた回路110A,110Bを備える。回路110Aは端子31Aに接続され、端子31Aから端子31Bへ向かって配置されたセル120A,130A,140Aを含む。回路110Bは端子31Bに接続され、端子31Bから端子31Aへ向かって配置されたセル120B,130B,140Bを含む。セル120A,120Bのレイアウトは、形状、サイズ及び向きがトランジスタレベルで同一である。セル130A,130B及びセル140A,140Bのレイアウトは、形状及びサイズが同一であり、トランジスタの向きが180°相違している。これにより各セルを対称配置しつつ、センシティブなセル120A,120Bにおいては電流方向の違いによる特性差が生じない。

(もっと読む)

半導体装置

【課題】InやZnなどを含む酸化物半導体をチャネル領域に用いたトランジスタを、P型トランジスタのように駆動できる半導体装置を提供する。

【解決手段】トランジスタとインバータを有し、インバータの出力はトランジスタのゲートに入力され、トランジスタのチャネル領域はIn、Zn若しくはSnを含む酸化物半導体膜を有し、インバータを構成するトランジスタのチャネル領域はシリコンを有し、インバータにハイ電圧を入力すると、インバータからロー電圧が出力されるとともにトランジスタのゲートにロー電圧が入力されてトランジスタはオフし、インバータにロー電圧を入力すると、インバータからハイ電圧が出力されるとともにトランジスタのゲートにハイ電圧が入力されてトランジスタはオンする半導体装置によって解決する。

(もっと読む)

半導体集積回路

【課題】電源が遮断されてもデータが保持される新規な論理回路を提供する。また、消費電力を低減できる新規な論理回路を提供する。

【解決手段】2つの出力ノードを比較する比較器と、電荷保持部と、出力ノード電位確定部とを電気的に接続することにより、論理回路を構成する。それにより、電源が遮断されてもデータが保持される論理回路を得ることができる。また、論理回路を構成するトランジスタの総個数を低減させることができる。更に、酸化物半導体を用いたトランジスタとシリコンを用いたトランジスタを積層させることで、論理回路の面積の削減が可能になる。

(もっと読む)

半導体集積装置

【課題】SiPのチップ間を接続するための端子数が増加する。

【解決手段】パッケージ内部に第1の半導体チップと第2の半導体チップが集積される半導体集積回路であって、前記第1の半導体チップは、第1の通信部と、複数のアナログ回路とを備え、前記第2の半導体チップは、第2の通信部と、前記複数のアナログ回路の特性調整用データを格納するメモリ部とを備え、前記第1の通信部と前記第2の通信部とがシリアルデータ通信線で接続され、前記シリアルデータ線を経由して前記第1の半導体チップが備える複数のアナログ回路の特性調整用データをそれぞれ複数のアナログ回路に転送する半導体集積回路。

(もっと読む)

1 - 20 / 715

[ Back to top ]