Fターム[5F038DF06]の内容

半導体集積回路 (75,215) | 集積回路機能及び回路ブロック構成 (8,544) | 補助機能 (1,408)

Fターム[5F038DF06]の下位に属するFターム

機能調整制御 (266)

省電力 (982)

耐放射線 (28)

プロテクト、コピー防止 (122)

Fターム[5F038DF06]に分類される特許

1 - 10 / 10

半導体装置

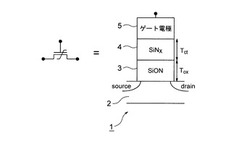

【課題】FETの駆動力性能や遮断性能などを向上できる半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板上に形成され、オフ状態とオン状態とで閾値電圧を可変させるFETからなる半導体素子と、を備える。前記半導体素子は、前記半導体基板のチャネル形成箇所の上方に形成される絶縁膜と、前記絶縁膜の上方に配置されるゲート電極と、前記絶縁膜と前記ゲート電極との間に介挿され、前記チャネルとの間よりも、前記ゲート電極との間で、より多くの電子の授受を行なうチャージトラップ膜と、を有する。

(もっと読む)

電源状態判定回路を有する集積回路

【課題】電源オープン検出回路の動作マージンを大きくする。

【解決手段】電源端子とグランド端子と入力端子と内部回路とが形成された集積回路において,入力端子と電源端子との間に設けられ,入力端子から前記電源端子への方向の一方向性回路と,電源端子が外部電源と接続しているか否かを検出して電源オープン検出信号を出力する電源状態判定回路とを有する。一方向性回路は,電源端子の電圧がゲートに印加される第1のトランジスタと,第1のトランジスタに直列に接続された第2のトランジスタとを有し,入力端子には外部電源の電圧が入力される。

(もっと読む)

アンチヒューズ構造体及びアレイ

【課題】アンチヒューズ構造体及びアレイを提供する。

【解決手段】基板内に第1拡散領域で形成されたビットラインと、ビットライン上に形成された絶縁層と、絶縁層上に形成されたワードラインと、を備えるアンチヒューズ構造体である。ビットラインの周辺部に形成された第2拡散領域をさらに備える。ビットラインは、第1ドーピング物質でドーピングされた領域であり、第2拡散領域は、第2ドーピング物質でドーピングされた領域である。ビットラインの両側部に形成された素子分離膜をさらに備える。

(もっと読む)

半導体装置と半導体装置の識別方法

【課題】配置面積に対する識別能力の向上、製造工程の煩雑さを回避しつつ高信頼性を実現した半導体装置の識別方法を提供する。

【解決手段】識別情報発生回路は、互いに同じ製造過程をもって同一の形態として半導体基板上に形成された複数の識別要素を含み、上記複数の識別要素の持つ電気的特性バラツキに起因する上記複数の識別要素の相互の物理量の大小関係により決定される複数ビットからなる識別情報を発生させる。カウンタは、上記識別情報発生回路から識別情報を奇数回読み出し、2値のうち一方の値であるときにはカウントアップし、他方の値あるときにはカウントダウンする。制御回路は、上記決められた読み出し回数が完了したときのカウント値が正ならば当該ビットを上記一方の値とし決定し、カウント値が負ならば当該ビットを上記他方の値とし決定して識別情報を生成して出力する。

(もっと読む)

半導体集積回路

【課題】単位面積当たりの容量を大きくする。

【解決手段】半導体集積回路であって、第1の電極と、半導体基板上に形成され、第2の電極を有するトランジスタと、同一の配線層に形成された第3及び第4の電極とを有する。前記第1の電極は、前記トランジスタを構成する拡散領域と接続されている。前記第2の電極は、前記トランジスタのゲートを構成している。前記第3及び第4の電極は、いずれも櫛形の形状を有しており、それぞれの少なくとも一部が前記トランジスタと重なるように形成されている。

(もっと読む)

半導体装置と検証方法

【課題】IDIPから出力されるIDのユニーク性やランダム性の自己診断を可能にした半導体装置及びその検証方法を提供する。

【解決手段】互いに同じ製造過程をもって同一の形態として半導体基板上に形成された複数の識別要素の持つ電気的特性バラツキに起因する上記複数の識別要素の相互の物理量の大小関係に決定される複数ビットからなる識別情報(ID)を発生させる識別情報発生回路(IDIP)を備えた半導体装置に上記複数ビットの識別情報におけるランダム性を判別する判別回路を設ける。この判別回路は、確率論に基づく簡単な手法により実現することができる。

(もっと読む)

集積回路装置及び電子機器

【課題】静電気放電等を原因とする誤動作を防止できる集積回路装置等の提供。

【解決手段】集積回路装置は、イネーブル信号ENBが第2の電圧レベルである場合に、パッド18からの入力信号Dをバッファリングして出力するI/O回路20と、I/O回路20からの出力信号が入力される回路ブロック50と、信号ENBが第1の電圧レベルである期間T1と、信号ENBが第1の電圧レベルから第2の電圧レベルに遷移する期間を含む期間T2では、電源VDDCにより電圧レベルが設定される出力信号QPを回路ブロック50に出力し、信号ENBが第2の電圧レベルとなる期間T3では、I/O回路20からの出力信号QIに応じた出力信号QPを回路ブロック50に出力する誤動作防止回路30を含む。

(もっと読む)

トリミング回路

【課題】本発明は、トリミング素子のトリミング状態に依らず、消費電流を低減することが可能なトリミング回路を提供することを目的とする。

【解決手段】本発明に係るトリミング回路は、フューズFと;電源ラインとフューズFとの間に接続されたスイッチTr1と;その出力信号がトリミングデータOUTとして引き出されるラッチ回路FFと;電源ラインとラッチ回路FFのリセット端との間に接続され、フューズFとスイッチTr1との接続ノードに現れる電圧信号aに基づいて開閉制御されるスイッチTr2と;ラッチ回路FFのリセット端と接地ラインとの間に接続され、スイッチTr1と同一の開閉状態に制御されるスイッチTr3と;電源ラインとラッチ回路FFのリセット端との間に接続され、ラッチ回路FFの出力信号gに基づいて開閉制御されるスイッチTr4と;スイッチTr1、Tr3の開閉制御信号b、c及びラッチ回路FFのセット信号dを生成する制御回路CTRLと;を有して成る構成としている。

(もっと読む)

温度保護回路、電源装置、電子機器

【課題】本発明は、緊急度に応じて適切な温度保護動作を行い、延いては、システム全体として、より安全性の高い温度保護動作を行うことが可能な温度保護回路、並びに、これを備えた電源装置及び電子機器を提供することを目的とする。

【解決手段】本発明に係る温度保護回路は、監視対象温度Tjの異常上昇時にイネーブルとされる遮断信号Stsdを生成する温度保護回路であって、監視対象温度Tjの上昇勾配に応じて監視対象温度Tjが第1閾値温度Tth1に達してから遮断信号Stsdをイネーブルとするまでのタイミングを制御する手段と、監視対象温度Tjが第1閾値温度Tth1に達してから遮断信号Stsdがイネーブルとされるまでの期間にイネーブルとされる異常報知信号Serrを生成する手段と、を有して成る構成とされている。

(もっと読む)

半導体集積回路

【課題】高速動作化のためMOSトランジスタの基板がフォワードバイアスされたときのラッチアップ現象を防止する必要があるが、実デバイスでは、他の寄生バイポーラトランジスタが存在し、必ずしも最適な防止対策ではなかった。

【解決手段】基板とソースとが分離されたMOS回路を含む論理回路11と、MOS回路に印加する基板電圧を生成する基板電圧生成回路12と、MOS回路の基板とソースとの面積比が保存された別に基板分離されたレイアウト形状のダミーMOS回路21を含み、ダミーMOS回路のソースおよび基板の電流測定を通じてMOS回路のラッチアップ状況を監視するラッチアップモニター回路13と、ラッチアップモニター回路による電流比検出信号が示す電流比に応じた限界電圧を指示する限界電圧指示信号を生成し、基板電圧生成回路12による基板電圧を制限する限界電圧生成回路14を備える。

(もっと読む)

1 - 10 / 10

[ Back to top ]