Fターム[5F038DF10]の内容

半導体集積回路 (75,215) | 集積回路機能及び回路ブロック構成 (8,544) | 補助機能 (1,408) | プロテクト、コピー防止 (122)

Fターム[5F038DF10]に分類される特許

1 - 20 / 122

半導体装置

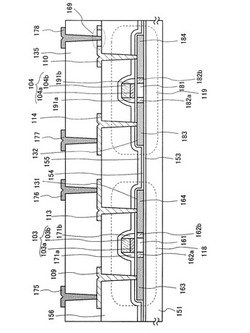

【課題】無線通信により交信可能な半導体装置において、個体識別子を容易に付けることができるようにする。

【解決手段】薄膜トランジスタ119と、薄膜トランジスタ上に第1の層間絶縁膜156と、第1の層間絶縁膜上の、ソース領域またはドレイン領域の一方に電気的に接続される第1の電極114と、ソース領域またはドレイン領域の他方に電気的に接続される第2の電極110と、第1の層間絶縁膜、第1の電極、及び第2の電極上に形成された第2の層間絶縁膜135と、第2の層間絶縁膜上の、第1の電極または第2の電極の一方に電気的に接続される第1の配線177と、第2の層間絶縁膜上の、第1の電極または第2の電極の他方に電気的に接続されない第2の配線178とを有し、第2の配線と前記第1の電極または第2の電極の他方は、第2の層間絶縁膜中の分断領域169によって、電気的に接続されない半導体装置及びその作製方法に関するものである。

(もっと読む)

半導体装置

【課題】

実施形態は、解析が簡便な半導体装置を提供する。

【解決手段】

本実施形態の半導体装置は、内部信号を伝送可能な第1配線101と、第1配線101

と電気的に接続された測定電極100と、測定電極100と隣接するように配置され、内

部信号を計測するときに接地電位VSSが印加され、内部信号を計測する以外のときに所

望の電圧が印加されたダミー電極102,103とを備える。

例えば、測定電極100は、環状に形成されており、ダミー電極は、第1電極102と

第2電極103とを有し、第1電極102は、測定電極100の内側に形成された空間に

隣接するように配置され、第2電極103は、測定電極100の外側に隣接するように配

置される。

(もっと読む)

鍵格納回路、半導体集積回路、及びシステム

【課題】格納された鍵の値の推測を困難にすることができる、鍵格納回路、半導体集積回路、及びシステムを提供する。

【解決手段】LSI10に搭載された鍵格納ブロック20は、k個のヒューズメモリセル30を有するヒューズブロック22と、鍵生成回路24と、を備えており、ヒューズブロック22からは予め実装されているビット長kの固定出力値fout[k−1:0]が出力される。鍵生成回路24は、レジスタ及び復号器を含んで構成されており、復号器は、演算処理により、固定出力値fout[k−1:0]と、レジスタの出力値と、からビット長n(n>k)の鍵key[n−1:0]を生成して出力する。

(もっと読む)

半導体装置

【課題】セキュリティ情報を格納した領域への物理的な破壊攻撃を、従来よりも簡単な手法で検知する。

【解決手段】半導体装置1において、第1の機能モジュール3は、正常に動作しているか否かのテスト対象となる。第2の機能モジュール2は、第1の機能モジュール3にテストデータを出力し、テストデータに応じて第1の機能モジュールから出力された出力信号が正常なデータパターンと一致するか否かを判定する。第3の機能モジュール7は、耐タンパ性を必要とする。シールド配線SLは、基板に対して垂直方向から見たときに第3の機能モジュール7が設けられた領域を覆うように設けられ、その両端部は第1の機能モジュール3と接続される。シールド配線SLが断線しているとき、上記の出力信号は正常なデータパターンと一致しなくなる。

(もっと読む)

半導体装置

【課題】スキャンテストを可能にしながら内部データの漏洩及び改竄を防止する半導体装置を提供する。

【解決手段】複数のフリップフロップを有するユーザー回路と、テストモード時に、前記複数のフリップフロップを接続してスキャンチェーンを構成する接続経路とを有し、前記接続経路は、前記複数のフリップフロップのうちいずれかの前記フリップフロップの非反転出力値を論理演算して出力する論理演算回路、または、前記複数のフリップフロップのうちいずれかの前記フリップフロップの反転出力値を後段のフリップフロップに出力する反転値接続経路を有する。

(もっと読む)

半導体装置

【課題】本発明は、第1状態と第2状態との二つの状態のうち、第1状態に初期化し、初期化した第1状態に対応する電位の信号を生成することが可能な半導体装置を提供する。

【解決手段】本発明は、“0”(第1状態)と“1”(第2状態)との二つの状態のうち、“0”に初期化し、初期化した“0”に対応する電位の信号Aを生成することが可能な半導体装置10である。半導体装置10は、並列に複数接続され、“0”と“1”との二つの状態を保持することが可能なフリップフロップ回路2と、複数のフリップフロップ回路2と接続し、複数のフリップフロップ回路2のうち、少なくとも一つのフリップフロップ回路2で保持する状態が“0”の場合、“0”に対応する電位の信号を生成し、出力するAND回路3とを備える。

(もっと読む)

半導体装置

【課題】ゲート電極へのチャージアップの有無を解析する手法を用いても、書き込まれた情報を解析することができないようにするアンチヒューズをメモリ素子として有する半導体装置を提供する。

【解決手段】基板10は第1導電型、例えばp型の半導体基板(例えばシリコン基板)である。アンチヒューズは、ゲート電極120及び第2導電型拡散層130を有している。第2導電型拡散層130は基板10に形成されており、例えばn型である。第1コンタクト122はゲート電極120に接続している。第2コンタクト142は第1コンタクト122と同一層に形成されており、基板10のうち第2導電型拡散層130が形成されていない領域に接続している。第2コンタクト142は第1コンタクト122に隣接している。

(もっと読む)

未知の半導体装置の機能の非破壊的な決定

【課題】外部放射線に対して応答する接合を分析することを通して機能を推測することによる、集積回路の非破壊的なリバースエンジニアリングのためのシステム及び技術を提供する。

【解決手段】少なくとも1つの電源と電気的に導通している複数の半導体接合を含む半導体装置の機能を決定するための以下を含む方法。

・半導体装置の表面を照射すること;

・照射に応答する複数の半導体接合のうち少なくとも幾つかのレイアウトを決定すること;

・決定されたレイアウト内で、複数の半導体接合の少なくとも幾つかのグルーピングを同定し、各ブルーピングはそれぞれの機能セルを表すこと;

・複数の外部アクセス可能な接点のうち少なくとも1つへの刺激を変化させること;及び

・前記変化した刺激に応答して複数の相互接続された機能セルの1つ以上の接続を推測すること。

(もっと読む)

半導体集積回路装置およびテストモード設定方法

【課題】簡易な回路で、よりセキュリティ性を向上させる。

【解決手段】半導体集積回路装置(100)は、複数の機能ブロック(125−127)と、取り込み部(131)と、検出部(132)と、判定部(150)とを具備し、動作パターンが所定の規則に従って変化したときにテストモードに移行する。複数の機能ブロック(125−127)は、制御装置(200)からの指示に応答して動作する。取り込み部(131)は、複数の機能ブロック(125−127)のそれぞれの動作状態を示す信号を取り込む。検出部(132)は、複数の機能ブロック(125−127)のうちの少なくとも1つの機能ブロックの動作状態の変化を検出する。判定部(150)は、取り込まれた動作状態を示す信号によって示される動作パターンが所定の規則に従って変化するか否かを判定する。

(もっと読む)

半導体集積回路装置

【課題】保護対象の回路ブロックの上に配置された導電パターンに加えられた改変の検出する精度を向上するための技術を提供することを目的とする。

【解決手段】半導体基板に形成された回路ブロックと、回路ブロックのうち保護対象の部分の上層に配置された導電パターンと、導電パターンに接続され、導電パターンの回路定数により決定される発振周波数で発振する発振回路と、発振回路の発振周波数が事前に設定された範囲に含まれるか否かを判定し、発振周波数が事前に設定された範囲に含まれない場合に、導電パターンに改変が加えられたことを検出する検出回路とを有することを特徴とする半導体集積回路装置が提供される。

(もっと読む)

スキャンパス内蔵半導体集積回路

【課題】既存のテスト回路を用いて簡単な回路や制御を追加することでセキュリティ性を高める。

【解決手段】スキャンレジスタ方式の回路を保持したLSIにおいて、スキャン入力端子181〜183から入力したパスワードを、パスワード入力レジスタ101〜103に保持する。パスワード入力レジスタ101〜103とマスター・パスワード131〜133とをそれぞれ比較器111〜113で比較し、結果をパスワード判定回路100に送る。比較結果が全て一致していたら、スキャンパス・チェーン191〜193と出力バッファ151〜153との間の経路をスルーにする。逆に比較結果に不一致がある場合は、スキャンパス・チェーン191〜193と出力バッファ151〜153との間の経路を遮断する。

(もっと読む)

半導体集積回路装置

【課題】半導体基板の表側に配置された回路が半導体基板の裏側から解析されることを検出する技術を提供することを目的とする。

【解決手段】回路ブロックが配置された第1面と、第1面の反対側の第2面とを有する半導体基板と、半導体基板を搭載する実装基板と、実装基板のうち、回路ブロックの保護対象の部分と重なる領域に配置された導電パターンと、導電パターンに改変が加えられたことを検出する検出回路とを有する半導体集積回路装置が提供される。半導体基板の第2面と実装基板とが対向するように、半導体基板が実装基板に搭載されている。

(もっと読む)

半導体集積回路装置

【課題】保護対象の回路ブロックの上に配置された導電パターンに加えられた改変の検出精度を向上するための技術を提供することを目的とする。

【解決手段】半導体基板に配置された回路ブロックと、回路ブロックのうち保護対象の部分の上層に配置された導電パターンと、導電パターンの第1部分の電位を基準電位にリセットするリセット部と、第1部分を電流供給ラインに接続する接続部と、第1部分の電位を基準電位にリセットした後に第1部分を電流供給ラインに接続してから一定時間経過後の第1部分の電圧が事前に設定された範囲に含まれるか否かを判定し、一定時間経過後の電圧が事前に設定された範囲に含まれない場合に導電パターンに改変が加えられたことを検出する検出回路とを有する半導体集積回路装置が提供される。第1部分の電圧の変化は、導電パターンの回路定数に依存する。

(もっと読む)

保護回路と半導体装置及び電子機器

【課題】従来はシールド線を部分的に切断又は剥離後、FIB加工等や適当な手段で物理解析を阻害しない迂回経路でシールド線に再接続する、あるいは外部から導体路をバイパスとしてシールド線に接続し、検出機能を無効にするような不正手段には脆弱であった。

【解決手段】半導体装置上の保護すべき領域を覆うように配線されかつ始点から終点に至る経路を1つのみ有する少なくとも1つのシールド線5を形成し、信号発生器2よりシールド線5に電気信号を与え、シールド線5に与えられた電気信号の変化を捉えたことを検出信号として出力する複数の検出器3を前記電気信号の変化が順番に伝播するように分散配置し、前記検出信号は判定器4に出力した順番に入力され前記検出信号の出力結果と前記検出信号が出力した順番とに基づいてシールド線5の状態を判定し、不正検知信号A1を出力することで、シールド線5の改竄を検出する保護回路を搭載する。

(もっと読む)

偽装トランジスタをカムフラージュするためのシリコンブロックプロセスステップの使用

【課題】アーチファクト縁部を利用してリバースエンジニアを混乱させる半導体デバイスおよび半導体デバイスを製造する方法を提供する。

【解決手段】輪郭を管理した導電性材料の層を配置して、デバイスが実際には動作不能であるときに、動作可能なデバイスのような導電性材料のアーチファクト縁部を形成する。実際に形成されるデバイスの特徴を示さないアーチファクト縁部を提供することにより、集積回路構造をカムフラージュするたの技術および構造である。

(もっと読む)

半導体集積回路および電子機器

【課題】不揮発性記憶素子にフューズ素子を用いた半導体集積回路において、目的とするデータと、検査データとしての目的とするデータの論理否定データとを記憶し、フューズ素子の不可逆性を利用することで、記憶回路と検証回路の回路規模をあまり大きくすることなく、またデータ検証の処理時間の増大を招くことなく、記憶データの信頼性と正真性を保証する。

【解決手段】記憶すべき情報を示す特定データを不可逆的に記憶する不揮発性記憶回路100aを有する半導体集積回路100において、該不揮発性記憶回路100aを、該特定データの非反転データを記憶する第1の記憶回路101と、該特定データの反転データを記憶する第2の記憶回路102とを有する構成とした。

(もっと読む)

半導体集積回路及びデータ処理システム

【課題】意図的に誤動作を生じさせるための局所的な光照射を検出するための構成を小さなチップ占有面積で実現し、検出感度を高くする。

【解決手段】ロジック回路(6)が形成された領域に分散され初段の入力が一定論理値にされて直列的に接続された複数個の検出インバータ(100)を検出素子として採用し、単数又は複数のインバータに光が照射されて各々に出力が反転することによって直列的に接続された複数個の検出インバータの最終出力が判定され、これにより局所的な光照射を検出することができる。

(もっと読む)

半導体装置及び半導体チップ

【課題】半導体チップを製造する際のダイシング精度の悪化を防止するとともに、流通後のTEGを用いた測定の実行を完全に防止する。

【解決方法】半導体装置は、複数の製品領域と、それら製品領域間に設けられたスクライブ領域とを備える。複数の製品領域のそれぞれは、プロービング用電極34、40とセンス電極36、38を少なくとも有するTEG30を有している。TEG30には、TEG内の他の部分と比較して電流許容量が低く設定されているセンス配線36a、38aが設けられている。半導体装置では、センス配線36a、38aに所定電流以下の電流が印加された状態でTEG30の特性を測定することができる。その一方、センス配線36a、38aに所定電流を越える電流を印加するとセンス配線36a、38aが破壊される。

(もっと読む)

半導体パッケージ

【課題】磁気メモリ素子に記憶された情報を不正な手段で読み出すことを困難にして、磁気メモリ素子に記憶された情報が漏洩することを抑制できる半導体パッケージを提供すること。

【解決手段】磁気を加えることにより情報を記憶するメモリセル11を有するダイ10を内部に備える半導体パッケージ1であって、パッケージ本体20の内部に配置され、メモリセル11の磁気メモリ素子を磁化可能な磁界MF1を少なくともメモリセル11が位置する空間に発生させる磁界源41と、ダイ10の基板面10Aを覆って配置され、メモリセル11に加わる磁界MF1を減衰させる磁気シールド材42と、を備えることを特徴とする。

(もっと読む)

試作品用半導体パッケージおよび半導体集積回路検査方法

【課題】CPUをデバッグ可能にパッケージングされ、CPUを他者が解析不可能にパッケージングされることができる半導体チップを提供すること。

【解決手段】第1パッド10と、第1パッド10に接続されている第2パッド11と、CPU5をデバッグするTAPコントローラ7に接続されている第3パッド12とを備えている。このような半導体チップ2は、第2パッド11と第3パッド12とが接続されるようにパッケージングされたときに、第1パッド10に接続されている外部端子24を介してTAPコントローラ7に電気信号を出力してCPU5をデバッグすることができる。このような半導体チップ2は、さらに、第2パッド11と第3パッド12とが電気的に接続されないようにパッケージングされたときに、外部端子とTAPコントローラ7とを切断することができ、他者がCPU5を解析することをより確実に防止することができる。

(もっと読む)

1 - 20 / 122

[ Back to top ]