鍵格納回路、半導体集積回路、及びシステム

【課題】格納された鍵の値の推測を困難にすることができる、鍵格納回路、半導体集積回路、及びシステムを提供する。

【解決手段】LSI10に搭載された鍵格納ブロック20は、k個のヒューズメモリセル30を有するヒューズブロック22と、鍵生成回路24と、を備えており、ヒューズブロック22からは予め実装されているビット長kの固定出力値fout[k−1:0]が出力される。鍵生成回路24は、レジスタ及び復号器を含んで構成されており、復号器は、演算処理により、固定出力値fout[k−1:0]と、レジスタの出力値と、からビット長n(n>k)の鍵key[n−1:0]を生成して出力する。

【解決手段】LSI10に搭載された鍵格納ブロック20は、k個のヒューズメモリセル30を有するヒューズブロック22と、鍵生成回路24と、を備えており、ヒューズブロック22からは予め実装されているビット長kの固定出力値fout[k−1:0]が出力される。鍵生成回路24は、レジスタ及び復号器を含んで構成されており、復号器は、演算処理により、固定出力値fout[k−1:0]と、レジスタの出力値と、からビット長n(n>k)の鍵key[n−1:0]を生成して出力する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、鍵格納回路、半導体集積回路、及びシステム、特に暗号化や復号化に用いられる鍵を格納する鍵格納回路、半導体集積回路、及びシステムに関するものである。

【背景技術】

【0002】

一般に、不揮発性メモリに、データ信号の暗号化や復号化に使用する鍵(以下、単に鍵という)を実装するLSI(半導体集積回路)が知られている。鍵の実装に、不揮発性メモリとして代表的なEPROMやFLASHメモリを使用するためには、メモリ混載プロセスを使用するか、または1つのパッケージに複数のチップを封入するマルチチップモジュール化を行う必要があり、何れもコスト、技術面等で問題があることから、鍵を実装するためだけに上記メモリを使用することは非現実的とされている。

【0003】

そのため、通常プロセスで使用可能なヒューズを上述の不揮発性メモリの代わりに使用し、ヒューズに鍵を実装する技術が知られている。例えば、特許文献1には、処理装置に含まれるヒューズにセキュアキー値を格納する技術が記載されている。

【0004】

ヒューズに鍵を実装する場合の例を図9に示す。図9に示したチップ(基板)112上に実装されたLSI(半導体集積回路)100は、鍵を格納するための鍵格納ブロック120を備えている。鍵格納ブロック120は、ヒューズメモリセル130を、実装する鍵のビット長に応じた個数、搭載している。図9に示した鍵格納ブロック120の場合では、鍵のビット長nに応じて、n個のヒューズメモリセル130(130n−1〜1300)を搭載している。ヒューズメモリセル130は、LSI100の電源電圧VDD側に接続されたヒューズ132と、GND(LSI100のGND)側に接続されたヒューズ134とを備えている。ヒューズ132及びヒューズ134のいずれかを電気的に切断することにより、ヒューズメモリセル130の出力の値がVDDか、GNDかの何れかに確定する。

【0005】

鍵の実装は、LSI100のウエハレベルのテスト工程等で、各ヒューズメモリセル130のヒューズ132及びヒューズ134のいずれか一方を切断することにより行われる。VDD側に接続されたヒューズ132を切断した場合は、ヒューズメモリセル130の出力は「0」に固定される。一方、GND側に接続されたヒューズ134を切断した場合は、ヒューズメモリセル130の出力は「1」に固定される。そのため、ヒューズメモリセル130のいずれかのヒューズ(132、134)を切断することにより鍵格納ブロック120の出力の値である鍵key[n−1:0]が確定する。LSI100を使用するユーザや用途によって、ヒューズを切断する組み合わせを変えることにより、個々に特有のユニークな値の鍵の実装が可能になる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2009−135905号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

上述のようにヒューズに鍵を実装する場合、1個のヒューズメモリセル130が鍵の1ビットに対応しているため、鍵のビット長に合わせた個数(ビット長と等しい個数)のヒューズメモリセル130を搭載する必要がある。

【0008】

ヒューズに鍵を実装する方法では、上述した不揮発性メモリに鍵を実装する場合に比べて、安価な通常プロセスで実現できるというメリットがあるものの、ヒューズ(ヒューズ132またはヒューズ134)1個が10μm角程度の大きさを有するため、実装する鍵のビット長が長い場合、搭載するヒューズメモリセル130(ヒューズ132、134)の個数が多くなり、その結果、チップサイズ(面積)が大きくなってしまい、コストが高くなる場合がある。

【0009】

また、上述のようにヒューズメモリセル130と鍵の値が1対1で対応しており、ヒューズを切断した跡は、目視、または顕微鏡等で容易に確認できるため、鍵情報を推測されやすいというセキュリティ上の問題があった。

【0010】

本発明は、上述した問題を解決するために提案されたものであり、格納された鍵の値の推測を困難にすることができる、鍵格納回路、半導体集積回路、及びシステムを提供することを目的とする。

【課題を解決するための手段】

【0011】

上記目的を達成するために、請求項1に記載の鍵格納回路は、少なくとも1つ以上のヒューズを有し、かつ前記ヒューズの切断状態に応じて予め定められた第1の値が格納された格納手段と、予め定められた第2の値が記憶された記憶手段と、前記格納手段に格納されている前記第1の値及び前記記憶手段に記憶されている前記第2の値を用いて予め定められた演算を実行することによりデータ信号を暗号化または復号化するための鍵を生成する鍵生成回路と、を備える。

【0012】

請求項11に記載の半導体集積回路は、基板と、前記基板上に実装された、前記請求項1から前記請求項10のいずれか1項に記載の鍵格納回路と、を備える。

【0013】

請求項13に記載のシステムは、前記鍵格納回路に格納された鍵に基づいて、データ信号を暗号化した暗号化信号を生成する暗号化信号生成回路を備えた前記請求項11に記載の半導体集積回路と、前記鍵格納回路に格納された鍵に基づいて、前記暗号化信号を復号化して前記データ信号を生成する復号化信号生成回路を備えた前記請求項11に記載の半導体集積回路と、を備える。

【発明の効果】

【0014】

本発明によれば、格納された鍵の値の推測を困難にすることができる、という効果を奏する。

【図面の簡単な説明】

【0015】

【図1】第1の実施の形態に係るLSI(半導体集積回路)の概略構成の一例を示す概略構成図である。

【図2】第1の実施の形態に係る鍵格納ブロックの概略構成の一例を示す回路図である。

【図3】第1の実施の形態に係る鍵生成回路の概略構成の一例を示す概略構成図である。

【図4】第2の実施の形態に係る鍵格納ブロックの概略構成の一例を示す回路図である。

【図5】第2の実施の形態に係る鍵生成回路の概略構成の一例を示す概略構成図である。

【図6】第3の実施の形態に係る鍵格納ブロックの概略構成の一例を示す回路図である。

【図7】第4の実施の形態に係る鍵格納ブロックの概略構成の一例を示す回路図である。

【図8】データ信号を暗号化するためのLSI(半導体集積回路)の概略構成の一例を示す概略構成図である。

【図9】従来の鍵格納ブロックの概略構成の一例を示す回路図である。

【発明を実施するための形態】

【0016】

[第1の実施の形態]

【0017】

以下、図面を参照して第1の実施の形態の鍵格納ブロック(鍵格納回路)及び当該鍵格納ブロックを備えたLSI(Large Scale Integration:半導体集積回路、以下単にLSIという)について詳細に説明する。なお、本実施の形態では、予め鍵により暗号化されたデータ信号(暗号化データ信号)を当該鍵を用いて復号化する場合について説明する。

【0018】

まず、本実施の形態のLSIの構成について説明する。本実施の形態のLSIの概略構成の一例を図1に示す。図1に示した本実施の形態のLSI10は、チップ(基板、以下、単にチップという)12上に、データ信号復号化回路14及び鍵格納ブロック20が搭載されている。

【0019】

本実施の形態のLSI10では、データ信号が鍵により暗号化された暗号化データ信号が外部から入力される。データ信号復号化回路14は、入力された暗号化データ信号を鍵格納ブロック20に格納されている鍵を用いて、予め定められた復号化方法により復号した復号化データ信号(元のデータ信号)を出力する機能を有している。なお、本実施の形態のデータ信号は、例えば、映像信号や個人情報を含む信号等、特に限定されるものではない。また、データ信号復号化回路14で行われる復号化の方法は、一般に用いられる方法等でよく、特に限定されるものではない。また、データ信号復号化回路14から出力された復号化データ信号を使用する処理回路等は、LSI10内に搭載されていてもよいし、LSI10の外部に設けられていてもよく、特に限定されるものではない。

【0020】

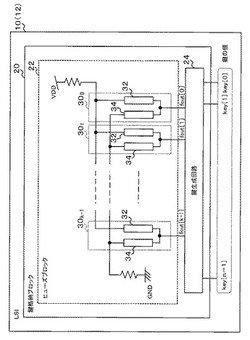

本実施の形態の鍵格納ブロック20は、データ信号の復号化(暗号化)に使用される鍵を格納する機能を有しており、ヒューズブロック22と、鍵生成回路24と、により構成されている。本実施の形態の鍵格納ブロック20の概略構成の一例の回路図を図2に示す。

【0021】

本実施の形態の鍵格納ブロック20は、複数(本実施の形態ではk個)のヒューズメモリセル30(30k−1〜300)を有するヒューズブロック22及び鍵生成回路24を備えて構成されている。ヒューズメモリセル30は、LSI10の電源電圧VDD側に接続されたヒューズ32と、GND(LSI10のGND)側に接続されたヒューズ34と、を備えている。なお、本実施の形態では、具体的一例として、鍵格納ブロック20は、nビットの鍵を格納する。

【0022】

本実施の形態では、LSI10のウエハレベルのテスト工程で、ヒューズブロック22のヒューズメモリセル30が有するヒューズ32及びヒューズ34のいずれか一方を切断することにより、ヒューズメモリセル30の出力の値は、VDDか、GNDかの何れかに確定される。なお、本実施の形態でヒューズ(32、34)の「切断」とは、少なくとも電気的な切断であればよく、物理的に切断されていなくてもよい。

【0023】

本実施の形態では、具体的一例として、VDD側に接続されたヒューズ32を切断した場合は、ヒューズメモリセル30の出力は「0」に固定される。一方、GND側に接続されたヒューズ34を切断した場合は、ヒューズメモリセル30の出力は「1」に固定される。このようにヒューズ(32、34)を切断することにより、ヒューズブロック22からは、ビット長kの固定出力値fout[k−1:0]が鍵生成回路24に出力される。本実施の形態では、固定出力値fout[k−1:0]と、復号器42により生成される鍵(key[n−1:0])とは、1対1の対応関係にある(詳細後述)。

【0024】

なお、本実施の形態のヒューズブロック22は、鍵を復号するための情報が実装されているものであり、鍵情報(鍵の値)そのものを実装するものではない。そのため、本実施の形態のヒューズブロック22に備えられるヒューズメモリセル30の数は、鍵のビット長nに依存しない。従って、ヒューズメモリセル30の個数を鍵のビット長nよりも少ない個数とすることができる。そのため、本実施の形態では、k<nとしている。

【0025】

なお、本実施の形態では、搭載するヒューズメモリセル30の個数は、ヒューズブロック22により格納可能な、ユニークな鍵の数に依存している。具体的一例として、ユニークな鍵の数を16個に設定した場合、搭載するヒューズメモリセル30の数は16=24であるため、4個となる。従ってこのような場合は、鍵格納ブロック20に格納する鍵のビット長nが192ビットであっても、256ビットであっても、鍵格納ブロック20が搭載するヒューズメモリセル30の個数は4個でよい。従って、LSI10(鍵格納ブロック20)では、4個のヒューズメモリセル30のヒューズ(32、34)の切断の仕方を変更するのみで、鍵のビット長nに係らず、16個のユニークな鍵に対応することができる。

【0026】

本実施の形態の鍵生成回路24の概略構成の一例を図3に示す。図1に示した本実施の形態の鍵生成回路24は、レジスタ40及び復号器42を含んで構成されている。本実施の形態のレジスタ40は、予め格納されている固定値が出力される。なお、レジスタ40は、予め固定値を格納しておくことができる論理回路であればよく、例えばフリップフロップ等の回路素子により構成されるものを用いることができ、その種類等は特に限定されるものではない。また、鍵生成回路24以外の別のプロセッサ等で用いられるレジスタをレジスタ40として併用してもよい。レジスタ40の容量等は、特に限定されないが、本実施の形態(鍵を生成するための固定値の格納)専用のレジスタとして構成する場合は、固定値に応じた容量にすればよいが、容量をなるべく小さくすることにより、チップサイズの増加やコストの増加を抑制することができる。

【0027】

なお、レジスタ40の代わりに、EPROMやフラッシュメモリ等を用いるようにしてもよいが、レジスタ40を用いる場合、実装後の工程で設定する自由度を増すことができると共に、より高速に処理が行えるため好ましい。

【0028】

本実施の形態の復号器42は、ヒューズブロック22の固定出力値fout[k−1:0]と、レジスタ40の出力値と、を用いて所定の演算処理を行う演算処理回路(本実施の形態では論理回路)であり、当該演算処理を実行することにより、LSI10の個々に特有のユニークなビット長nの鍵(key[n−1:0])を生成して出力する機能を有している。

【0029】

復号器42で行われる演算処理は、ヒューズブロック22の固定出力値fout[k−1:0]とレジスタ40の出力値とによりビット長nの鍵(key[n−1:0])が生成できる演算処理であればよく、加減乗除等予め定められた処理を行うものであればよく、特に限定されるものではない。なお、本実施の形態の演算処理では、復号器42に入力される固定出力値fout[k−1:0]のビット長kよりも鍵key[n−1:0]のビット長nが長くなる。

【0030】

なお、例えば、ヒューズブロック22に実装されている固定値は、目視や顕微鏡等で確認できるため、鍵の値そのものではなくとも、数が少ない方がよい場合がある。一方、ヒューズブロック22の個数が多い方が、ウエハレベルのテスト等、実装後の工程で設定する自由度を増すことができる。また、レジスタ40に格納されている値のビット数を多くすると、レジスタ40の回路全体が大きくなるため、鍵格納ブロック20(LSI10)の面積増加や、コスト増加を招く場合がある。

【0031】

従って、ヒューズブロック22に実装されている固定出力値fout[k−1:0]、レジスタ40に格納されている固定値、及び演算処理の方法は、ヒューズブロック22から出力される固定出力値fout[k−1:0]のビット長k、鍵key[n−1:0]のビット長n、LSI10の仕様、ユーザ所望のセキュリティ、及びコスト等の観点により定めればよい。

【0032】

以上説明したように本実施の形態のLSI10に搭載された鍵格納ブロック20は、k個のヒューズメモリセル30を有するヒューズブロック22と、鍵生成回路24と、を備えており、ヒューズブロック22からは予め実装されているビット長kの固定出力値fout[k−1:0]が出力される。鍵生成回路24は、レジスタ40及び復号器42を含んで構成されており、復号器42は、演算処理により、固定出力値fout[k−1:0]と、レジスタ40の出力値と、からビット長n(n>k)の鍵key[n−1:0]を生成して出力する。

【0033】

このように本実施の形態の鍵格納ブロック20では、ヒューズブロック22に鍵そのものを格納するのではなく、ヒューズブロック22に格納された固定出力値foutに基づいて、LSI10(鍵格納ブロック20)内部で鍵を生成するため、ヒューズブロック22を目視または、顕微鏡等で確認した場合であっても、鍵の値を推測することが困難になり、高いセキュリティを確保することができる。

【0034】

また、本実施の形態では、ヒューズメモリセル30の個数は、鍵のビット長kに依存せず、1対1で対応していないため、格納する鍵のビット長kよりも少ない数とすることができる。従って、実装する鍵のビット長kが大きくなっても鍵格納ブロック20(LSI10)に搭載するヒューズメモリセル30の個数は変わらず、チップサイズの増加やコストの増加を抑制することができる。特に、セキュリティの観点から鍵のビット長kを大きくすることが好まれているが、演算処理の仕方や、レジスタ40に格納されている値を変化させればよく、ヒューズメモリセル30の個数を増加しなくてもよいため、チップサイズの増加やコストの増加を抑制することができる。

【0035】

また、ヒューズメモリセル30のヒューズ(32、34)を切断する組み合わせを変えることにより、ヒューズメモリセル30の個数に依存したユニークな値の鍵の実装が可能になる。

【0036】

[第2の実施の形態]

【0037】

以下、図面を参照して本発明の第2の実施の形態について説明する。なお、第1の実施の形態と略同様の構成、動作については、その旨を記載し、詳細な説明を省略する。なお、本実施の形態では、鍵生成回路のレジスタが複数の固定値を格納しており、復号器が複数の固定値のいずれかを演算処理に使用する。

【0038】

本実施の形態の鍵格納ブロックを搭載したLSI(チップ)の概略構成の一例を図4に示す。本実施の形態の鍵格納ブロック53は、チップ12上にヒューズブロック22と、レジスタ選択ブロック56と、鍵生成回路58と、が搭載されている。本実施の形態の鍵生成回路58の概略構成の一例を図5に示す。本実施の形態の鍵生成回路58は、x個のメモリ45(451〜45x)を含むレジスタ41及び復号器43を有して構成されている。なお、本実施の形態では、メモリ45を「メモリ」と称しているが、論理回路により構成されるメモリ(いわゆるレジスタと同様)である。

【0039】

レジスタ選択ブロック56は、レジスタ41に含まれるx個のメモリ45のいずれかを選択するためのビット長lの選択信号となる固定出力値(fout[k+1:k])を出力する機能を有している。そのため、選択信号のビット長lと同じ個数のヒューズメモリセル30(30k+1〜30k)を備えており、選択信号情報が実装されている。なお、ヒューズメモリセル30の選択信号情報の実装の仕方は、ヒューズブロック22に固定出力値を実装する方法と同様であり、ヒューズメモリセル30のヒューズ32及びヒューズ34のいずれか一方を切断することにより、出力を確定させる。また、実装するタイミングは、ヒューズブロック22に固定出力値を実装するタイミングと一緒であってもよいし、別であってもよい。

【0040】

復号器43は、選択回路46及び鍵復号化回路47を備えて構成されている。選択回路46は、レジスタ選択ブロック56から出力された選択信号fout[k+1:k]に基づいて、レジスタ41のメモリ45の出力値のいずれかを選択して、鍵復号化回路47に出力する機能を有している。

【0041】

鍵復号化回路47は、選択回路46から出力された出力値と、固定出力値fout[k−1:0]と、から演算処理によりビット長kの鍵key[n−1:0]を生成して出力する。なお、鍵復号化回路47の演算処理は、第1の実施の形態の復号器42と略同様の処理であるためここでは詳細な説明を省略する。

【0042】

このように本実施の形態では、鍵生成回路58がx個のメモリ45を含んでおり、レジスタ選択ブロック56のヒューズメモリセル30に何れのメモリ45を選択するかを示す情報が格納されている。従って、第1の実施の形態と同様の効果に加えて、さらに、鍵の値を推測しづらくすることができる。

【0043】

また、レジスタ41に含まれるメモリ45の個数に応じた個数のユニークな鍵を生成することができる。これにより、レジスタ選択ブロック56に実装される選択信号情報を変えるのみで複数のユーザやユーザ仕様に対応できるため、より自由度を増すことができる。

【0044】

なお、本実施の形態では、選択信号情報をレジスタ選択ブロック56に実装する構成について説明したがこれに限らず、ヒューズを用いずに他のメモリ等の記憶可能な媒体に格納(実装)するようにしてもよい。

【0045】

[第3の実施の形態]

【0046】

以下、図面を参照して本発明の第3の実施の形態について説明する。なお、第1の実施の形態と略同様の構成、動作については、その旨を記載し、詳細な説明を省略する。なお、本実施の形態では、鍵生成回路が、鍵格納ブロックに格納されている鍵の一部を生成する。

【0047】

本実施の形態の鍵格納ブロックを搭載したLSIの概略構成の一例を図6に示す。本実施の形態の鍵格納ブロック63は、ヒューズブロック64と、鍵格納サブブロック66と、鍵生成回路68と、が搭載されている。

【0048】

本実施の形態のヒューズブロック64は、ビット長kの鍵のうち、ビット長m分の鍵を生成するための情報が実装されている。そのため、ヒューズブロック64は、i個のヒューズメモリセル30(30i−1〜300)を搭載している。なお、第1の実施の形態と同様に、搭載するヒューズメモリセル30の個数iは、鍵生成回路68により生成される鍵のビット長mよりも小さいため、i<mである。

【0049】

本実施の形態の鍵生成回路68は、第1の実施の形態の鍵生成回路24と略同様の構成、動作を有しており、演算処理により、ヒューズブロック64から出力された固定出力値fout[i−1:0]と、レジスタ40の出力値と、からビット長m(m>i)の鍵key[m−1:0]を生成して出力する。

【0050】

また、本実施の形態では、鍵格納サブブロック66のヒューズメモリセル30(30n−1〜30m)に、鍵の一部(本実施の形態では、n−mビット分の鍵)が実装されている。なお、鍵格納サブブロック66のヒューズメモリセル30の鍵の実装の仕方は、ヒューズブロック22に固定出力値を実装する方法と同様であり、ヒューズメモリセル30のヒューズ32及びヒューズ34のいずれか一方を切断することにより、出力を確定させる。また、実装するタイミングは、ヒューズブロック22に固定出力値を実装するタイミングと一緒であってもよいし、別であってもよい。

【0051】

鍵格納ブロック63は、鍵格納サブブロック66のヒューズメモリセル30に実装されているビット長n−mの鍵と、鍵生成回路68により生成されたビット長mの鍵とを組み合わせてビット長nの鍵としてデータ信号復号化回路14に出力する。なお、本実施の形態の鍵格納ブロック63では、鍵生成回路68により生成されたビット長mの鍵にそのまま鍵格納サブブロック66に実装されているビット長n−mの鍵を付加することにより組み合わせているが組み合わせ方はこれに限らない。なお組み合わせ方を異ならせることにより、同一のヒューズブロック64と鍵格納サブブロック66とが搭載された鍵格納ブロック63であっても、格納(出力)する鍵の値を異ならせることができる。また、鍵格納ブロック63内に両者を組見合わせるための組合回路を設けて、当該回路により組み合わせるようにしてもよい。

【0052】

このように本実施の形態では、一部(本実施の形態ではビット長n−m)の鍵を鍵格納サブブロック66のヒューズメモリセル30に実装し、残り(本実施の形態ではビット長m)の鍵を第1の実施の形態と同様に、鍵生成回路68が演算処理によりヒューズブロック64から出力されるビット長iの固定出力値fout[i−1:0]とレジスタ40の出力値とから生成して出力する。鍵格納ブロック63は、鍵格納サブブロック66から出力された鍵と、鍵生成回路68から出力された鍵とを組み合わせて最終的な鍵(ビット長kの鍵key[k−1:0])を出力する。

【0053】

従って、第1の実施の形態と同様に、鍵格納ブロック63に搭載するヒューズメモリセル30の全個数を、最終低な鍵のビット長k以下の個数とすることができるため、チップサイズの増加やコストの増加を抑制することができる。

【0054】

また、最終的な鍵の一部のみがヒューズメモリセル30に実装されているため、第1の実施の形態と同様に、鍵の値を推測しづらくすることができる。

【0055】

さらに、本実施の形態では、鍵の一部を鍵格納サブブロック66のヒューズメモリセル30に実装するため、ウエハプロセス後に、ユーザの所望等に応じて、鍵(最終的な鍵)の値を変更したり、鍵の種類を増加させたりすることができる。また、ウエハプロセス中に実装させるのではなく、ウエハプロセス後に変更可能であるため、鍵の値を設定し易くなり、自由度が増す。

【0056】

[第4の実施の形態]

【0057】

以下、図面を参照して本発明の第4の実施の形態について説明する。なお、第1の実施の形態と略同様の構成、動作については、その旨を記載し、詳細な説明を省略する。なお、本実施の形態では、ヒューズブロックから出力される固定出力値fout[i−1:0]がタイマによって切り替えられる。

【0058】

本実施の形態の鍵格納ブロックを搭載したLSIの概略構成の一例を図7に示す。本実施の形態のLSI70のチップ72上には、鍵格納ブロック73と、原稿サイズ推定部76と、が搭載されている。また、本実施の形態の鍵格納ブロック73には、ヒューズブロック74と、鍵生成回路24と、が搭載されている。

【0059】

ヒューズブロック22には、第1の実施の形態のヒューズブロック22の構成に加えて、ヒューズメモリセル30の接続先を切り替えるための、一対のPMOSトランジスタ及びNMOSトランジスタからなる回路77、同様の回路78、及び反転回路79を備えている。タイマ76から「H」レベルの信号が出力されると、回路77により、ヒューズメモリセル30のヒューズ34がGNDに接続される。一方、回路78により、ヒューズメモリセル30のヒューズ32が電源電圧VDDに接続される。また、タイマ76から「L」レベルの信号が出力されると、回路77により、ヒューズメモリセル30のヒューズ34が電源電圧VDDに接続される。一方、回路78により、ヒューズメモリセル30のヒューズ32がGNDに接続される。従って、タイマ76から出力される信号のレベルにより、ヒューズメモリセル30の出力値「1」または「0」が切り替えられる。

【0060】

このように本実施の形態では、タイマ76から出力される信号のレベルにより、ヒューズブロック74のヒューズメモリセル30のヒューズ32及びヒューズ34の接続先である電源電圧VDDと、GNDとを切り替えることができる。これにより、タイマ76から出力される信号のレベルに応じて、ヒューズブロック74の固定出力値fout[i−1:0]を切り替えることができる。具体的には、固定出力値fout[i−1:0]の各ビットの「1」、「0」を反転させることができる。従って、鍵生成回路24で生成、出力される鍵の値key[k−1:0]をタイマ76から出力される信号のレベルに応じて変更することができる。

【0061】

従って、第1の実施の形態と同様の効果が得られると共に、より鍵の値を推測することが困難となり、より高いセキュリティを確保することができる。

【0062】

タイマ76の動作(出力される信号のレベルを変化させる動作)については、特に限定されない。なお、暗号化データ信号の送信側のLSI10と、受信側のLSI10とで、鍵の変更されるタイミングを把握している場合、例えば、同一周期で動作するタイマ76が搭載されている場合、送信側のLSI10から把握されているタイミングで鍵を変更して暗号化した暗号化データ信号を受信側のLSI10に送信するようにシステムを構成することが好ましい。このようにすることにより、さらに高いセキュリティを確保することができる。

【0063】

なお、上述した各実施の形態では、ヒューズ32とヒューズ34とを備えることによりヒューズメモリセル30に「1」または「0」を実装していたがこれに限らず、例えば1つのヒューズのみを備え、当該ヒューズが切断されているか否かにより実装するようにしてもよい。

【0064】

また、上述した各実施の形態では、暗号化データ信号を、鍵格納ブロック20に格納されている鍵に基づいて、データ信号復号化回路14により復号した復号化データ信号(元のデータ信号)を出力する構成(図1参照)について説明したがこれに限らず、図8に示すように、LSI11(チップ13)上に鍵格納ブロック20と、データ信号暗号化回路16とを搭載し、LSI11内で、データ信号を鍵格納ブロック20に格納された鍵を用いてデータ信号暗号化回路16で暗号化し、暗号化したデータ信号暗号化回路16を(例えば、LSI11の外部に)送信するように構成してもよい。この場合においても、データ信号暗号化回路16による鍵を用いた暗号化の方法は、一般に用いられる方法等でよく、特に限定されるものではない。また、図8に示したデータ信号を鍵格納ブロック20に格納された鍵により暗号化して暗号化データ信号を送信するLSI10と、図1に示した暗号化データ信号を鍵格納ブロック20に格納された鍵により復号化するLSI10と、を組み合わせたシステムを構成することが好ましいことは言うまでもない。

【0065】

なお、上述した各実施の形態で説明した、LSIや鍵格納ブロック、ヒューズブロック、鍵生成回路の構成等は一例であり、本発明の主旨を逸脱しない範囲内において状況に応じて変更されることは言うまでもない。また、上述した各実施の形態を組み合わせて用いてもよい。

【符号の説明】

【0066】

10 LSI(半導体集積回路)

【技術分野】

【0001】

本発明は、鍵格納回路、半導体集積回路、及びシステム、特に暗号化や復号化に用いられる鍵を格納する鍵格納回路、半導体集積回路、及びシステムに関するものである。

【背景技術】

【0002】

一般に、不揮発性メモリに、データ信号の暗号化や復号化に使用する鍵(以下、単に鍵という)を実装するLSI(半導体集積回路)が知られている。鍵の実装に、不揮発性メモリとして代表的なEPROMやFLASHメモリを使用するためには、メモリ混載プロセスを使用するか、または1つのパッケージに複数のチップを封入するマルチチップモジュール化を行う必要があり、何れもコスト、技術面等で問題があることから、鍵を実装するためだけに上記メモリを使用することは非現実的とされている。

【0003】

そのため、通常プロセスで使用可能なヒューズを上述の不揮発性メモリの代わりに使用し、ヒューズに鍵を実装する技術が知られている。例えば、特許文献1には、処理装置に含まれるヒューズにセキュアキー値を格納する技術が記載されている。

【0004】

ヒューズに鍵を実装する場合の例を図9に示す。図9に示したチップ(基板)112上に実装されたLSI(半導体集積回路)100は、鍵を格納するための鍵格納ブロック120を備えている。鍵格納ブロック120は、ヒューズメモリセル130を、実装する鍵のビット長に応じた個数、搭載している。図9に示した鍵格納ブロック120の場合では、鍵のビット長nに応じて、n個のヒューズメモリセル130(130n−1〜1300)を搭載している。ヒューズメモリセル130は、LSI100の電源電圧VDD側に接続されたヒューズ132と、GND(LSI100のGND)側に接続されたヒューズ134とを備えている。ヒューズ132及びヒューズ134のいずれかを電気的に切断することにより、ヒューズメモリセル130の出力の値がVDDか、GNDかの何れかに確定する。

【0005】

鍵の実装は、LSI100のウエハレベルのテスト工程等で、各ヒューズメモリセル130のヒューズ132及びヒューズ134のいずれか一方を切断することにより行われる。VDD側に接続されたヒューズ132を切断した場合は、ヒューズメモリセル130の出力は「0」に固定される。一方、GND側に接続されたヒューズ134を切断した場合は、ヒューズメモリセル130の出力は「1」に固定される。そのため、ヒューズメモリセル130のいずれかのヒューズ(132、134)を切断することにより鍵格納ブロック120の出力の値である鍵key[n−1:0]が確定する。LSI100を使用するユーザや用途によって、ヒューズを切断する組み合わせを変えることにより、個々に特有のユニークな値の鍵の実装が可能になる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2009−135905号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

上述のようにヒューズに鍵を実装する場合、1個のヒューズメモリセル130が鍵の1ビットに対応しているため、鍵のビット長に合わせた個数(ビット長と等しい個数)のヒューズメモリセル130を搭載する必要がある。

【0008】

ヒューズに鍵を実装する方法では、上述した不揮発性メモリに鍵を実装する場合に比べて、安価な通常プロセスで実現できるというメリットがあるものの、ヒューズ(ヒューズ132またはヒューズ134)1個が10μm角程度の大きさを有するため、実装する鍵のビット長が長い場合、搭載するヒューズメモリセル130(ヒューズ132、134)の個数が多くなり、その結果、チップサイズ(面積)が大きくなってしまい、コストが高くなる場合がある。

【0009】

また、上述のようにヒューズメモリセル130と鍵の値が1対1で対応しており、ヒューズを切断した跡は、目視、または顕微鏡等で容易に確認できるため、鍵情報を推測されやすいというセキュリティ上の問題があった。

【0010】

本発明は、上述した問題を解決するために提案されたものであり、格納された鍵の値の推測を困難にすることができる、鍵格納回路、半導体集積回路、及びシステムを提供することを目的とする。

【課題を解決するための手段】

【0011】

上記目的を達成するために、請求項1に記載の鍵格納回路は、少なくとも1つ以上のヒューズを有し、かつ前記ヒューズの切断状態に応じて予め定められた第1の値が格納された格納手段と、予め定められた第2の値が記憶された記憶手段と、前記格納手段に格納されている前記第1の値及び前記記憶手段に記憶されている前記第2の値を用いて予め定められた演算を実行することによりデータ信号を暗号化または復号化するための鍵を生成する鍵生成回路と、を備える。

【0012】

請求項11に記載の半導体集積回路は、基板と、前記基板上に実装された、前記請求項1から前記請求項10のいずれか1項に記載の鍵格納回路と、を備える。

【0013】

請求項13に記載のシステムは、前記鍵格納回路に格納された鍵に基づいて、データ信号を暗号化した暗号化信号を生成する暗号化信号生成回路を備えた前記請求項11に記載の半導体集積回路と、前記鍵格納回路に格納された鍵に基づいて、前記暗号化信号を復号化して前記データ信号を生成する復号化信号生成回路を備えた前記請求項11に記載の半導体集積回路と、を備える。

【発明の効果】

【0014】

本発明によれば、格納された鍵の値の推測を困難にすることができる、という効果を奏する。

【図面の簡単な説明】

【0015】

【図1】第1の実施の形態に係るLSI(半導体集積回路)の概略構成の一例を示す概略構成図である。

【図2】第1の実施の形態に係る鍵格納ブロックの概略構成の一例を示す回路図である。

【図3】第1の実施の形態に係る鍵生成回路の概略構成の一例を示す概略構成図である。

【図4】第2の実施の形態に係る鍵格納ブロックの概略構成の一例を示す回路図である。

【図5】第2の実施の形態に係る鍵生成回路の概略構成の一例を示す概略構成図である。

【図6】第3の実施の形態に係る鍵格納ブロックの概略構成の一例を示す回路図である。

【図7】第4の実施の形態に係る鍵格納ブロックの概略構成の一例を示す回路図である。

【図8】データ信号を暗号化するためのLSI(半導体集積回路)の概略構成の一例を示す概略構成図である。

【図9】従来の鍵格納ブロックの概略構成の一例を示す回路図である。

【発明を実施するための形態】

【0016】

[第1の実施の形態]

【0017】

以下、図面を参照して第1の実施の形態の鍵格納ブロック(鍵格納回路)及び当該鍵格納ブロックを備えたLSI(Large Scale Integration:半導体集積回路、以下単にLSIという)について詳細に説明する。なお、本実施の形態では、予め鍵により暗号化されたデータ信号(暗号化データ信号)を当該鍵を用いて復号化する場合について説明する。

【0018】

まず、本実施の形態のLSIの構成について説明する。本実施の形態のLSIの概略構成の一例を図1に示す。図1に示した本実施の形態のLSI10は、チップ(基板、以下、単にチップという)12上に、データ信号復号化回路14及び鍵格納ブロック20が搭載されている。

【0019】

本実施の形態のLSI10では、データ信号が鍵により暗号化された暗号化データ信号が外部から入力される。データ信号復号化回路14は、入力された暗号化データ信号を鍵格納ブロック20に格納されている鍵を用いて、予め定められた復号化方法により復号した復号化データ信号(元のデータ信号)を出力する機能を有している。なお、本実施の形態のデータ信号は、例えば、映像信号や個人情報を含む信号等、特に限定されるものではない。また、データ信号復号化回路14で行われる復号化の方法は、一般に用いられる方法等でよく、特に限定されるものではない。また、データ信号復号化回路14から出力された復号化データ信号を使用する処理回路等は、LSI10内に搭載されていてもよいし、LSI10の外部に設けられていてもよく、特に限定されるものではない。

【0020】

本実施の形態の鍵格納ブロック20は、データ信号の復号化(暗号化)に使用される鍵を格納する機能を有しており、ヒューズブロック22と、鍵生成回路24と、により構成されている。本実施の形態の鍵格納ブロック20の概略構成の一例の回路図を図2に示す。

【0021】

本実施の形態の鍵格納ブロック20は、複数(本実施の形態ではk個)のヒューズメモリセル30(30k−1〜300)を有するヒューズブロック22及び鍵生成回路24を備えて構成されている。ヒューズメモリセル30は、LSI10の電源電圧VDD側に接続されたヒューズ32と、GND(LSI10のGND)側に接続されたヒューズ34と、を備えている。なお、本実施の形態では、具体的一例として、鍵格納ブロック20は、nビットの鍵を格納する。

【0022】

本実施の形態では、LSI10のウエハレベルのテスト工程で、ヒューズブロック22のヒューズメモリセル30が有するヒューズ32及びヒューズ34のいずれか一方を切断することにより、ヒューズメモリセル30の出力の値は、VDDか、GNDかの何れかに確定される。なお、本実施の形態でヒューズ(32、34)の「切断」とは、少なくとも電気的な切断であればよく、物理的に切断されていなくてもよい。

【0023】

本実施の形態では、具体的一例として、VDD側に接続されたヒューズ32を切断した場合は、ヒューズメモリセル30の出力は「0」に固定される。一方、GND側に接続されたヒューズ34を切断した場合は、ヒューズメモリセル30の出力は「1」に固定される。このようにヒューズ(32、34)を切断することにより、ヒューズブロック22からは、ビット長kの固定出力値fout[k−1:0]が鍵生成回路24に出力される。本実施の形態では、固定出力値fout[k−1:0]と、復号器42により生成される鍵(key[n−1:0])とは、1対1の対応関係にある(詳細後述)。

【0024】

なお、本実施の形態のヒューズブロック22は、鍵を復号するための情報が実装されているものであり、鍵情報(鍵の値)そのものを実装するものではない。そのため、本実施の形態のヒューズブロック22に備えられるヒューズメモリセル30の数は、鍵のビット長nに依存しない。従って、ヒューズメモリセル30の個数を鍵のビット長nよりも少ない個数とすることができる。そのため、本実施の形態では、k<nとしている。

【0025】

なお、本実施の形態では、搭載するヒューズメモリセル30の個数は、ヒューズブロック22により格納可能な、ユニークな鍵の数に依存している。具体的一例として、ユニークな鍵の数を16個に設定した場合、搭載するヒューズメモリセル30の数は16=24であるため、4個となる。従ってこのような場合は、鍵格納ブロック20に格納する鍵のビット長nが192ビットであっても、256ビットであっても、鍵格納ブロック20が搭載するヒューズメモリセル30の個数は4個でよい。従って、LSI10(鍵格納ブロック20)では、4個のヒューズメモリセル30のヒューズ(32、34)の切断の仕方を変更するのみで、鍵のビット長nに係らず、16個のユニークな鍵に対応することができる。

【0026】

本実施の形態の鍵生成回路24の概略構成の一例を図3に示す。図1に示した本実施の形態の鍵生成回路24は、レジスタ40及び復号器42を含んで構成されている。本実施の形態のレジスタ40は、予め格納されている固定値が出力される。なお、レジスタ40は、予め固定値を格納しておくことができる論理回路であればよく、例えばフリップフロップ等の回路素子により構成されるものを用いることができ、その種類等は特に限定されるものではない。また、鍵生成回路24以外の別のプロセッサ等で用いられるレジスタをレジスタ40として併用してもよい。レジスタ40の容量等は、特に限定されないが、本実施の形態(鍵を生成するための固定値の格納)専用のレジスタとして構成する場合は、固定値に応じた容量にすればよいが、容量をなるべく小さくすることにより、チップサイズの増加やコストの増加を抑制することができる。

【0027】

なお、レジスタ40の代わりに、EPROMやフラッシュメモリ等を用いるようにしてもよいが、レジスタ40を用いる場合、実装後の工程で設定する自由度を増すことができると共に、より高速に処理が行えるため好ましい。

【0028】

本実施の形態の復号器42は、ヒューズブロック22の固定出力値fout[k−1:0]と、レジスタ40の出力値と、を用いて所定の演算処理を行う演算処理回路(本実施の形態では論理回路)であり、当該演算処理を実行することにより、LSI10の個々に特有のユニークなビット長nの鍵(key[n−1:0])を生成して出力する機能を有している。

【0029】

復号器42で行われる演算処理は、ヒューズブロック22の固定出力値fout[k−1:0]とレジスタ40の出力値とによりビット長nの鍵(key[n−1:0])が生成できる演算処理であればよく、加減乗除等予め定められた処理を行うものであればよく、特に限定されるものではない。なお、本実施の形態の演算処理では、復号器42に入力される固定出力値fout[k−1:0]のビット長kよりも鍵key[n−1:0]のビット長nが長くなる。

【0030】

なお、例えば、ヒューズブロック22に実装されている固定値は、目視や顕微鏡等で確認できるため、鍵の値そのものではなくとも、数が少ない方がよい場合がある。一方、ヒューズブロック22の個数が多い方が、ウエハレベルのテスト等、実装後の工程で設定する自由度を増すことができる。また、レジスタ40に格納されている値のビット数を多くすると、レジスタ40の回路全体が大きくなるため、鍵格納ブロック20(LSI10)の面積増加や、コスト増加を招く場合がある。

【0031】

従って、ヒューズブロック22に実装されている固定出力値fout[k−1:0]、レジスタ40に格納されている固定値、及び演算処理の方法は、ヒューズブロック22から出力される固定出力値fout[k−1:0]のビット長k、鍵key[n−1:0]のビット長n、LSI10の仕様、ユーザ所望のセキュリティ、及びコスト等の観点により定めればよい。

【0032】

以上説明したように本実施の形態のLSI10に搭載された鍵格納ブロック20は、k個のヒューズメモリセル30を有するヒューズブロック22と、鍵生成回路24と、を備えており、ヒューズブロック22からは予め実装されているビット長kの固定出力値fout[k−1:0]が出力される。鍵生成回路24は、レジスタ40及び復号器42を含んで構成されており、復号器42は、演算処理により、固定出力値fout[k−1:0]と、レジスタ40の出力値と、からビット長n(n>k)の鍵key[n−1:0]を生成して出力する。

【0033】

このように本実施の形態の鍵格納ブロック20では、ヒューズブロック22に鍵そのものを格納するのではなく、ヒューズブロック22に格納された固定出力値foutに基づいて、LSI10(鍵格納ブロック20)内部で鍵を生成するため、ヒューズブロック22を目視または、顕微鏡等で確認した場合であっても、鍵の値を推測することが困難になり、高いセキュリティを確保することができる。

【0034】

また、本実施の形態では、ヒューズメモリセル30の個数は、鍵のビット長kに依存せず、1対1で対応していないため、格納する鍵のビット長kよりも少ない数とすることができる。従って、実装する鍵のビット長kが大きくなっても鍵格納ブロック20(LSI10)に搭載するヒューズメモリセル30の個数は変わらず、チップサイズの増加やコストの増加を抑制することができる。特に、セキュリティの観点から鍵のビット長kを大きくすることが好まれているが、演算処理の仕方や、レジスタ40に格納されている値を変化させればよく、ヒューズメモリセル30の個数を増加しなくてもよいため、チップサイズの増加やコストの増加を抑制することができる。

【0035】

また、ヒューズメモリセル30のヒューズ(32、34)を切断する組み合わせを変えることにより、ヒューズメモリセル30の個数に依存したユニークな値の鍵の実装が可能になる。

【0036】

[第2の実施の形態]

【0037】

以下、図面を参照して本発明の第2の実施の形態について説明する。なお、第1の実施の形態と略同様の構成、動作については、その旨を記載し、詳細な説明を省略する。なお、本実施の形態では、鍵生成回路のレジスタが複数の固定値を格納しており、復号器が複数の固定値のいずれかを演算処理に使用する。

【0038】

本実施の形態の鍵格納ブロックを搭載したLSI(チップ)の概略構成の一例を図4に示す。本実施の形態の鍵格納ブロック53は、チップ12上にヒューズブロック22と、レジスタ選択ブロック56と、鍵生成回路58と、が搭載されている。本実施の形態の鍵生成回路58の概略構成の一例を図5に示す。本実施の形態の鍵生成回路58は、x個のメモリ45(451〜45x)を含むレジスタ41及び復号器43を有して構成されている。なお、本実施の形態では、メモリ45を「メモリ」と称しているが、論理回路により構成されるメモリ(いわゆるレジスタと同様)である。

【0039】

レジスタ選択ブロック56は、レジスタ41に含まれるx個のメモリ45のいずれかを選択するためのビット長lの選択信号となる固定出力値(fout[k+1:k])を出力する機能を有している。そのため、選択信号のビット長lと同じ個数のヒューズメモリセル30(30k+1〜30k)を備えており、選択信号情報が実装されている。なお、ヒューズメモリセル30の選択信号情報の実装の仕方は、ヒューズブロック22に固定出力値を実装する方法と同様であり、ヒューズメモリセル30のヒューズ32及びヒューズ34のいずれか一方を切断することにより、出力を確定させる。また、実装するタイミングは、ヒューズブロック22に固定出力値を実装するタイミングと一緒であってもよいし、別であってもよい。

【0040】

復号器43は、選択回路46及び鍵復号化回路47を備えて構成されている。選択回路46は、レジスタ選択ブロック56から出力された選択信号fout[k+1:k]に基づいて、レジスタ41のメモリ45の出力値のいずれかを選択して、鍵復号化回路47に出力する機能を有している。

【0041】

鍵復号化回路47は、選択回路46から出力された出力値と、固定出力値fout[k−1:0]と、から演算処理によりビット長kの鍵key[n−1:0]を生成して出力する。なお、鍵復号化回路47の演算処理は、第1の実施の形態の復号器42と略同様の処理であるためここでは詳細な説明を省略する。

【0042】

このように本実施の形態では、鍵生成回路58がx個のメモリ45を含んでおり、レジスタ選択ブロック56のヒューズメモリセル30に何れのメモリ45を選択するかを示す情報が格納されている。従って、第1の実施の形態と同様の効果に加えて、さらに、鍵の値を推測しづらくすることができる。

【0043】

また、レジスタ41に含まれるメモリ45の個数に応じた個数のユニークな鍵を生成することができる。これにより、レジスタ選択ブロック56に実装される選択信号情報を変えるのみで複数のユーザやユーザ仕様に対応できるため、より自由度を増すことができる。

【0044】

なお、本実施の形態では、選択信号情報をレジスタ選択ブロック56に実装する構成について説明したがこれに限らず、ヒューズを用いずに他のメモリ等の記憶可能な媒体に格納(実装)するようにしてもよい。

【0045】

[第3の実施の形態]

【0046】

以下、図面を参照して本発明の第3の実施の形態について説明する。なお、第1の実施の形態と略同様の構成、動作については、その旨を記載し、詳細な説明を省略する。なお、本実施の形態では、鍵生成回路が、鍵格納ブロックに格納されている鍵の一部を生成する。

【0047】

本実施の形態の鍵格納ブロックを搭載したLSIの概略構成の一例を図6に示す。本実施の形態の鍵格納ブロック63は、ヒューズブロック64と、鍵格納サブブロック66と、鍵生成回路68と、が搭載されている。

【0048】

本実施の形態のヒューズブロック64は、ビット長kの鍵のうち、ビット長m分の鍵を生成するための情報が実装されている。そのため、ヒューズブロック64は、i個のヒューズメモリセル30(30i−1〜300)を搭載している。なお、第1の実施の形態と同様に、搭載するヒューズメモリセル30の個数iは、鍵生成回路68により生成される鍵のビット長mよりも小さいため、i<mである。

【0049】

本実施の形態の鍵生成回路68は、第1の実施の形態の鍵生成回路24と略同様の構成、動作を有しており、演算処理により、ヒューズブロック64から出力された固定出力値fout[i−1:0]と、レジスタ40の出力値と、からビット長m(m>i)の鍵key[m−1:0]を生成して出力する。

【0050】

また、本実施の形態では、鍵格納サブブロック66のヒューズメモリセル30(30n−1〜30m)に、鍵の一部(本実施の形態では、n−mビット分の鍵)が実装されている。なお、鍵格納サブブロック66のヒューズメモリセル30の鍵の実装の仕方は、ヒューズブロック22に固定出力値を実装する方法と同様であり、ヒューズメモリセル30のヒューズ32及びヒューズ34のいずれか一方を切断することにより、出力を確定させる。また、実装するタイミングは、ヒューズブロック22に固定出力値を実装するタイミングと一緒であってもよいし、別であってもよい。

【0051】

鍵格納ブロック63は、鍵格納サブブロック66のヒューズメモリセル30に実装されているビット長n−mの鍵と、鍵生成回路68により生成されたビット長mの鍵とを組み合わせてビット長nの鍵としてデータ信号復号化回路14に出力する。なお、本実施の形態の鍵格納ブロック63では、鍵生成回路68により生成されたビット長mの鍵にそのまま鍵格納サブブロック66に実装されているビット長n−mの鍵を付加することにより組み合わせているが組み合わせ方はこれに限らない。なお組み合わせ方を異ならせることにより、同一のヒューズブロック64と鍵格納サブブロック66とが搭載された鍵格納ブロック63であっても、格納(出力)する鍵の値を異ならせることができる。また、鍵格納ブロック63内に両者を組見合わせるための組合回路を設けて、当該回路により組み合わせるようにしてもよい。

【0052】

このように本実施の形態では、一部(本実施の形態ではビット長n−m)の鍵を鍵格納サブブロック66のヒューズメモリセル30に実装し、残り(本実施の形態ではビット長m)の鍵を第1の実施の形態と同様に、鍵生成回路68が演算処理によりヒューズブロック64から出力されるビット長iの固定出力値fout[i−1:0]とレジスタ40の出力値とから生成して出力する。鍵格納ブロック63は、鍵格納サブブロック66から出力された鍵と、鍵生成回路68から出力された鍵とを組み合わせて最終的な鍵(ビット長kの鍵key[k−1:0])を出力する。

【0053】

従って、第1の実施の形態と同様に、鍵格納ブロック63に搭載するヒューズメモリセル30の全個数を、最終低な鍵のビット長k以下の個数とすることができるため、チップサイズの増加やコストの増加を抑制することができる。

【0054】

また、最終的な鍵の一部のみがヒューズメモリセル30に実装されているため、第1の実施の形態と同様に、鍵の値を推測しづらくすることができる。

【0055】

さらに、本実施の形態では、鍵の一部を鍵格納サブブロック66のヒューズメモリセル30に実装するため、ウエハプロセス後に、ユーザの所望等に応じて、鍵(最終的な鍵)の値を変更したり、鍵の種類を増加させたりすることができる。また、ウエハプロセス中に実装させるのではなく、ウエハプロセス後に変更可能であるため、鍵の値を設定し易くなり、自由度が増す。

【0056】

[第4の実施の形態]

【0057】

以下、図面を参照して本発明の第4の実施の形態について説明する。なお、第1の実施の形態と略同様の構成、動作については、その旨を記載し、詳細な説明を省略する。なお、本実施の形態では、ヒューズブロックから出力される固定出力値fout[i−1:0]がタイマによって切り替えられる。

【0058】

本実施の形態の鍵格納ブロックを搭載したLSIの概略構成の一例を図7に示す。本実施の形態のLSI70のチップ72上には、鍵格納ブロック73と、原稿サイズ推定部76と、が搭載されている。また、本実施の形態の鍵格納ブロック73には、ヒューズブロック74と、鍵生成回路24と、が搭載されている。

【0059】

ヒューズブロック22には、第1の実施の形態のヒューズブロック22の構成に加えて、ヒューズメモリセル30の接続先を切り替えるための、一対のPMOSトランジスタ及びNMOSトランジスタからなる回路77、同様の回路78、及び反転回路79を備えている。タイマ76から「H」レベルの信号が出力されると、回路77により、ヒューズメモリセル30のヒューズ34がGNDに接続される。一方、回路78により、ヒューズメモリセル30のヒューズ32が電源電圧VDDに接続される。また、タイマ76から「L」レベルの信号が出力されると、回路77により、ヒューズメモリセル30のヒューズ34が電源電圧VDDに接続される。一方、回路78により、ヒューズメモリセル30のヒューズ32がGNDに接続される。従って、タイマ76から出力される信号のレベルにより、ヒューズメモリセル30の出力値「1」または「0」が切り替えられる。

【0060】

このように本実施の形態では、タイマ76から出力される信号のレベルにより、ヒューズブロック74のヒューズメモリセル30のヒューズ32及びヒューズ34の接続先である電源電圧VDDと、GNDとを切り替えることができる。これにより、タイマ76から出力される信号のレベルに応じて、ヒューズブロック74の固定出力値fout[i−1:0]を切り替えることができる。具体的には、固定出力値fout[i−1:0]の各ビットの「1」、「0」を反転させることができる。従って、鍵生成回路24で生成、出力される鍵の値key[k−1:0]をタイマ76から出力される信号のレベルに応じて変更することができる。

【0061】

従って、第1の実施の形態と同様の効果が得られると共に、より鍵の値を推測することが困難となり、より高いセキュリティを確保することができる。

【0062】

タイマ76の動作(出力される信号のレベルを変化させる動作)については、特に限定されない。なお、暗号化データ信号の送信側のLSI10と、受信側のLSI10とで、鍵の変更されるタイミングを把握している場合、例えば、同一周期で動作するタイマ76が搭載されている場合、送信側のLSI10から把握されているタイミングで鍵を変更して暗号化した暗号化データ信号を受信側のLSI10に送信するようにシステムを構成することが好ましい。このようにすることにより、さらに高いセキュリティを確保することができる。

【0063】

なお、上述した各実施の形態では、ヒューズ32とヒューズ34とを備えることによりヒューズメモリセル30に「1」または「0」を実装していたがこれに限らず、例えば1つのヒューズのみを備え、当該ヒューズが切断されているか否かにより実装するようにしてもよい。

【0064】

また、上述した各実施の形態では、暗号化データ信号を、鍵格納ブロック20に格納されている鍵に基づいて、データ信号復号化回路14により復号した復号化データ信号(元のデータ信号)を出力する構成(図1参照)について説明したがこれに限らず、図8に示すように、LSI11(チップ13)上に鍵格納ブロック20と、データ信号暗号化回路16とを搭載し、LSI11内で、データ信号を鍵格納ブロック20に格納された鍵を用いてデータ信号暗号化回路16で暗号化し、暗号化したデータ信号暗号化回路16を(例えば、LSI11の外部に)送信するように構成してもよい。この場合においても、データ信号暗号化回路16による鍵を用いた暗号化の方法は、一般に用いられる方法等でよく、特に限定されるものではない。また、図8に示したデータ信号を鍵格納ブロック20に格納された鍵により暗号化して暗号化データ信号を送信するLSI10と、図1に示した暗号化データ信号を鍵格納ブロック20に格納された鍵により復号化するLSI10と、を組み合わせたシステムを構成することが好ましいことは言うまでもない。

【0065】

なお、上述した各実施の形態で説明した、LSIや鍵格納ブロック、ヒューズブロック、鍵生成回路の構成等は一例であり、本発明の主旨を逸脱しない範囲内において状況に応じて変更されることは言うまでもない。また、上述した各実施の形態を組み合わせて用いてもよい。

【符号の説明】

【0066】

10 LSI(半導体集積回路)

【特許請求の範囲】

【請求項1】

少なくとも1つ以上のヒューズを有し、かつ前記ヒューズの切断状態に応じて予め定められた第1の値が格納された格納手段と、

予め定められた第2の値が記憶された記憶手段と、

前記格納手段に格納されている前記第1の値及び前記記憶手段に記憶されている前記第2の値を用いて予め定められた演算を実行することによりデータ信号を暗号化または復号化するための鍵を生成する鍵生成回路と、

を備えた鍵格納回路。

【請求項2】

前記格納手段に格納されている第1の値のビット長は、前記鍵生成回路により生成される鍵のビット長よりも短い、請求項1に記載の鍵格納回路。

【請求項3】

前記記憶手段は、複数の記憶部を備え、前記格納手段は、前記複数の記憶部のうち、何れの記憶部を演算に用いるかを指定する指定手段を備える、請求項1または請求項2に記載の鍵格納回路。

【請求項4】

前記指定手段は、何れの記憶部を演算に用いるかを指定する情報を実装するヒューズを備える、請求項3に記載の鍵格納回路。

【請求項5】

前記格納手段は、前記鍵の一部を実装する鍵実装ヒューズを備え、

前記鍵生成回路は、演算を実行することにより得られた鍵と、前記鍵実装ヒューズに実装されている鍵と、を組み合わせて鍵を生成する、

請求項1から請求項4のいずれか1項に記載の鍵格納回路。

【請求項6】

前記格納手段は、電源電圧に接続されたヒューズ及びグランド電圧に接続されたヒューズの一対のヒューズから成るヒューズセルを備え、前記ヒューズセルは、前記一対のヒューズのいずれかが切断されている、

請求項1から請求項5のいずれか1項に記載の鍵格納回路。

【請求項7】

前記一対のヒューズの各々の接続先を切り替える切替手段を備えた、請求項6に記載の鍵格納回路。

【請求項8】

前記切替手段は、予め定められたタイミングで接続先を繰り返し切り替える、請求項7に記載の鍵格納回路。

【請求項9】

前記記憶手段は、論理回路により構成される、請求項1から請求項8のいずれか1項に記載の鍵格納回路。

【請求項10】

前記記憶手段は、レジスタである、請求項1から請求項9のいずれか1項に記載の鍵格納回路。

【請求項11】

基板と、

前記基板上に実装された、前記請求項1から前記請求項10のいずれか1項に記載の鍵格納回路と、

を備えた半導体集積回路。

【請求項12】

前記鍵格納回路に格納された鍵に基づいて、データ信号に対して暗号化及び復号化の少なくとも一方を行う信号生成回路を備えた、

請求項11に記載の半導体集積回路。

【請求項13】

前記鍵格納回路に格納された鍵に基づいて、データ信号を暗号化した暗号化信号を生成する暗号化信号生成回路を備えた前記請求項11に記載の半導体集積回路と、

前記鍵格納回路に格納された鍵に基づいて、前記暗号化信号を復号化して前記データ信号を生成する復号化信号生成回路を備えた前記請求項11に記載の半導体集積回路と、

を備えたシステム。

【請求項1】

少なくとも1つ以上のヒューズを有し、かつ前記ヒューズの切断状態に応じて予め定められた第1の値が格納された格納手段と、

予め定められた第2の値が記憶された記憶手段と、

前記格納手段に格納されている前記第1の値及び前記記憶手段に記憶されている前記第2の値を用いて予め定められた演算を実行することによりデータ信号を暗号化または復号化するための鍵を生成する鍵生成回路と、

を備えた鍵格納回路。

【請求項2】

前記格納手段に格納されている第1の値のビット長は、前記鍵生成回路により生成される鍵のビット長よりも短い、請求項1に記載の鍵格納回路。

【請求項3】

前記記憶手段は、複数の記憶部を備え、前記格納手段は、前記複数の記憶部のうち、何れの記憶部を演算に用いるかを指定する指定手段を備える、請求項1または請求項2に記載の鍵格納回路。

【請求項4】

前記指定手段は、何れの記憶部を演算に用いるかを指定する情報を実装するヒューズを備える、請求項3に記載の鍵格納回路。

【請求項5】

前記格納手段は、前記鍵の一部を実装する鍵実装ヒューズを備え、

前記鍵生成回路は、演算を実行することにより得られた鍵と、前記鍵実装ヒューズに実装されている鍵と、を組み合わせて鍵を生成する、

請求項1から請求項4のいずれか1項に記載の鍵格納回路。

【請求項6】

前記格納手段は、電源電圧に接続されたヒューズ及びグランド電圧に接続されたヒューズの一対のヒューズから成るヒューズセルを備え、前記ヒューズセルは、前記一対のヒューズのいずれかが切断されている、

請求項1から請求項5のいずれか1項に記載の鍵格納回路。

【請求項7】

前記一対のヒューズの各々の接続先を切り替える切替手段を備えた、請求項6に記載の鍵格納回路。

【請求項8】

前記切替手段は、予め定められたタイミングで接続先を繰り返し切り替える、請求項7に記載の鍵格納回路。

【請求項9】

前記記憶手段は、論理回路により構成される、請求項1から請求項8のいずれか1項に記載の鍵格納回路。

【請求項10】

前記記憶手段は、レジスタである、請求項1から請求項9のいずれか1項に記載の鍵格納回路。

【請求項11】

基板と、

前記基板上に実装された、前記請求項1から前記請求項10のいずれか1項に記載の鍵格納回路と、

を備えた半導体集積回路。

【請求項12】

前記鍵格納回路に格納された鍵に基づいて、データ信号に対して暗号化及び復号化の少なくとも一方を行う信号生成回路を備えた、

請求項11に記載の半導体集積回路。

【請求項13】

前記鍵格納回路に格納された鍵に基づいて、データ信号を暗号化した暗号化信号を生成する暗号化信号生成回路を備えた前記請求項11に記載の半導体集積回路と、

前記鍵格納回路に格納された鍵に基づいて、前記暗号化信号を復号化して前記データ信号を生成する復号化信号生成回路を備えた前記請求項11に記載の半導体集積回路と、

を備えたシステム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2013−55600(P2013−55600A)

【公開日】平成25年3月21日(2013.3.21)

【国際特許分類】

【出願番号】特願2011−194012(P2011−194012)

【出願日】平成23年9月6日(2011.9.6)

【出願人】(308033711)ラピスセミコンダクタ株式会社 (898)

【Fターム(参考)】

【公開日】平成25年3月21日(2013.3.21)

【国際特許分類】

【出願日】平成23年9月6日(2011.9.6)

【出願人】(308033711)ラピスセミコンダクタ株式会社 (898)

【Fターム(参考)】

[ Back to top ]