Fターム[5F038DT11]の内容

Fターム[5F038DT11]の下位に属するFターム

モニタ素子、モニタ回路 (1,067)

識別信号 (156)

チップ機能検査 (818)

Fターム[5F038DT11]に分類される特許

1 - 20 / 173

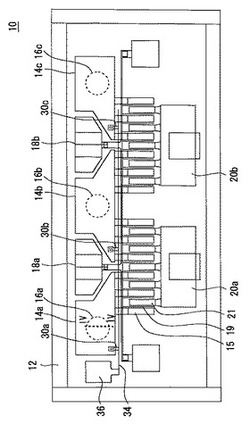

半導体装置

【課題】裏面電極と導通したパッドを破ることなく、複数のバイアホールの検査を短時間で実施できる半導体装置を提供する。

【解決手段】半導体装置は、基板と、該基板の裏面に形成された裏面電極と、該基板を貫通するN個(Nは2以上の整数)のバイアホール16のそれぞれを経由して該裏面電極と電気的に接続されるように該基板の表面に形成されたN個のパッドと、該N個のパッドのそれぞれに電気的に接続されたN個のエピ抵抗30とを有する。そして、該N個のエピ抵抗を介して該N個のパッドと接続された配線34と、該配線と接続された検査用パッド36と、該N個のパッド、及び該N個のバイアホールを経由して該裏面電極に電流を流すように該基板の表面に形成された電流印加用パターンと、を備える。

(もっと読む)

集積回路への電力供給方法、システム及びそれに使用される集積回路

【課題】半導体チップに供給する電圧を、公称最大動作電圧を超えて増加可能にする電力供給方法の提供。

【解決手段】組立てパッケージ内に所定の最大動作電圧を超えない電源電圧で動作するようにされた少なくとも一つの電力入力を有する複数の論理回路16を有するチップ4を有する集積回路2への電力供給方法は、論理回路の選択された1つの論理回路の電力入力において、論理回路の1つにおける電力入力においてチップ内に位置する計測点61で第2の電源電圧を直接測定すること、および計測点と選択された1つの論理回路の電源入力間の電圧降下に基づいて第1の電源電圧を決定するステップと、第1の電源電圧を、論理回路の選択された1つにおける所定の最大動作電圧に調節されるような値を有する基準電圧に調節するステップ、を備える。

(もっと読む)

半導体装置

【課題】ゲート絶縁膜の漏れ電流試験に影響を与えることなく、ゲート・ソース間に抵抗を挿入した半導体装置を提供すること。

【解決手段】実施形態に係る半導体装置は、ゲート電極及びソース電極間に抵抗が挿入されたトランジスタを内蔵する半導体装置であって、ゲート電極及びソース電極間に、抵抗に対して直列に挿入されたダイオードを備えることを特徴とする。

(もっと読む)

集積回路および集積回路の接続不良検出方法

【課題】製品組立後の経年劣化による接続不良を含め、簡単な構成で被実装基板との接続不良を検出する。

【解決手段】集積回路に、同一の電位が与えられる2以上の比較電圧用パッドと、比較電圧用パッドにかかる電圧を比較して、その比較結果に基づいて被実装基板との接続不良の有無を示す信号を出力する比較判別回路とを設け、比較判別回路において、少なくとも2つの比較電圧用パッドにかかる電圧の電位差が所定の値を超えた場合に、接続不良を示す信号を出力させる。

(もっと読む)

半導体装置、電子機器、および半導体装置の検査方法

【課題】電源端子または接地端子の接続不良を容易に検出する。

【解決手段】半導体装置の電源端子TCと第1の入出力端子T1との間には、電源端子TCがカソード側となり、第1の入出力端子T1がアノード側となるようにダイオードD11が設けられる。判定部10Aは、電源電圧Vccに等しいハイレベルの信号が第1の入出力端子T1に入力されたとき、電源端子TCの電圧が第1の入出力端子T1の電圧よりも低いか否かを判定する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】チップ面積を増大させることなく、針ずれに起因する誤測定や誤検査を防止することができる、半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置は、内部回路と、内部回路と電気的に接続されるとともに、検査装置に接続された複数の探針がそれぞれ接触する複数のパッドを備える。少なくとも2つのパッド2a、2bの間に、当該2つのパッド2a、2bを電気的に接続するとともに、所定の電流を印加することにより、恒久的に、電気的に切断されるヒューズ素子4が設けられる。パッド2a、2bの間の抵抗値を測定することで、針ずれの有無を検知することができる。その後、ヒューズ素子を切断し、内部回路の検査が実施される。

(もっと読む)

半導体集積回路

【課題】分周信号を検査するにあたって、その周波数のみならず第1区間長および第2区間長をも検査し、比較対象に用いる信号を生成する高価な検査装置を必要としない自己診断回路を有する半導体集積回路およびその検査方法を提供する。

【解決手段】分周回路の検査を、生成される分周信号の周波数およびデューティー比、すなわち第1区間および第2区間の比率、の2つに対して行う。外部からはデューティー比を定義する2つの期待値を供給する。

(もっと読む)

半導体回路、半導体装置、断線検出方法、及び断線検出プログラム

【課題】電池に関する信号線の断線を適切に検出することができる、半導体回路、半導体装置、断線検出方法、及び断線検出プログラムを提供する。

【解決手段】信号線Lnの断線検出を行う場合は、信号線Lnに信号線Lnの電位よりも低電位の信号線Ln−1よりも小さい電位を供給し、信号線Lnの電位と、信号線Ln−1の電位とを比較し、信号線Lcの電位>信号線Li(出力OUT=Lレベル)ならば、断線が無いことを検出し、信号線Lcの電位<信号線Li(出力OUT=Hレベル)ならば、断線が有ることを検出する。また、信号線Lnに信号線Lnよりも高電位の信号線Ln+1の電位よりも大きい電位を供給し、信号線Lnの電位と、信号線Ln+1の電位とを比較し、信号線Lcの電位<信号線Li(出力OUT=Hレベル)ならば、断線が無いことを検出し、信号線Lcの電位>信号線Li(出力OUT=Lレベル)ならば、断線が有ることを検出する。

(もっと読む)

半導体集積回路

【課題】半導体集積回路において、入力端子のオープン異常を、素子の追加量を抑えつつ且つ入力特性に影響を与えずに、検出可能にする。

【解決手段】マイコン21は、センサ信号を入力するための入力端子23が、プリント基板11の信号配線16に接続される。また、マイコン21において、電源電圧(5V)のラインとグランドラインとの各々と、入力端子23との間には、寄生ダイオードD1,D2がサージ電圧保護用のクランプダイオードとして機能するトランジスタ(MOSFET)T1,T2が接続されている。そして、マイコン21は、例えばトランジスタT2の方をハーフオン状態に駆動する駆動回路29を有しており、トランジスタT2をオフさせているときの入力端子23の電圧と、トランジスタT2をハーフオン状態に駆動したときの入力端子23の電圧とに基づいて、入力端子23が信号配線16と非接続になった異常(オープン異常)の有無を判定する。

(もっと読む)

半導体装置

【課題】異なる電位に対応する複数の外部電源配線間に間隔部分を有する半導体装置に対して,所定電源ピン数のテスタにより短絡試験を行う場合において,より多くの半導体装置の短絡試験を同時に行うことができる半導体装置を提供する。

【解決手段】半導体装置は,コア回路と,該コア回路の周囲に配置され且つコア回路と外部装置間の信号を入出力する複数の入出力回路と,複数の入出力回路のうちの第一の入出力回路グループに第一の電位の電源を供給する第一の電源配線と,複数の入出力回路のうちの第二の入出力回路グループに第二の電位の電源を供給し且つ第一の電源配線と間隔をあけて直列に延びる第二の電源配線と,第三の電位の電源を供給する第三の電源配線とを備え,第三の電源配線から延びる配線パターンが,第一の電源配線と第二の電源配線間の間隔部分に設けられる。

(もっと読む)

検査装置及び方法

【課題】検査対象回路が正常に機能しているか否かを電源電圧の立ち上がり期間に拘らず高精度に検査することができる半導体集積回路、検査装置及び方法を提供する。

【解決手段】検査装置10を、POR回路102の出力端子102Cから第1入力端子14Aにリセット信号が入力されたときに出力端子14Cからリセット信号と同レベルのリセット実行信号の出力を開始し、制御装置18の出力端子から第2入力端子14Bにトリガ信号が入力されたときにリセット実行信号の出力を終了して出力端子14Cからリセット解除信号と同レベルの解除実行信号の出力を開始するリセット制御回路14と、リセット制御回路14から出力された信号が予め定められたレベルであるか否かを判定することによりPOR回路102が正常に機能しているか否かを判定するテスタ124と、を含んで構成した。

(もっと読む)

未知の半導体装置の機能の非破壊的な決定

【課題】外部放射線に対して応答する接合を分析することを通して機能を推測することによる、集積回路の非破壊的なリバースエンジニアリングのためのシステム及び技術を提供する。

【解決手段】少なくとも1つの電源と電気的に導通している複数の半導体接合を含む半導体装置の機能を決定するための以下を含む方法。

・半導体装置の表面を照射すること;

・照射に応答する複数の半導体接合のうち少なくとも幾つかのレイアウトを決定すること;

・決定されたレイアウト内で、複数の半導体接合の少なくとも幾つかのグルーピングを同定し、各ブルーピングはそれぞれの機能セルを表すこと;

・複数の外部アクセス可能な接点のうち少なくとも1つへの刺激を変化させること;及び

・前記変化した刺激に応答して複数の相互接続された機能セルの1つ以上の接続を推測すること。

(もっと読む)

半導体装置、半導体装置の試験方法、及びデータ処理システム。

【課題】内部信号線の寄生抵抗値を測定できるようにする。

【解決手段】インターフェースチップとコアチップとを電気的に接続する1又は複数の内部信号線101を備え、インターフェースチップは、内部配線に電流を出力する第1の回路111を有し、コアチップは、第1の内部信号線101に電流を出力する第2の回路121を有し、インターフェースチップは、第1の回路111が出力する電流が流れる上記内部配線に接続される第1の入力端子151aと、第1の内部信号線101のインターフェースチップ内の端部101aに接続される第2の入力端子151bとを有し、第1の入力端子151aの電圧と第2の入力端子151bの電圧との電位差に応じた電圧を出力する判定回路150を有する。

(もっと読む)

半導体装置、半導体テスタおよび半導体テストシステム

【課題】テストコストを増大させることなく、オープン不良を検出することができる半導体装置、これを試験するための半導体テスタおよびこの半導体テスタを用いた半導体テストシステムを実現する。

【解決手段】内部回路の出力ピンと電気的に接続された複数のパッドを有する半導体装置において、一端が共通電位に接続され、他端がパッドに接続された第1のスイッチ回路と、内部回路の出力ピンとパッドの間に設けられ、第1のスイッチ回路が接続されたパッドと試験時に半導体テスタのテスタピンが接続されるパッドとを電気的に接続するマルチプレクサとを備える。

(もっと読む)

半導体装置の製造方法

【課題】エッチング装置の経時変化や状態変化等によらずトレンチの深さのばらつきを低減することができる半導体装置の製造方法を得る。

【解決手段】まず、所望の深さよりも浅い深さを持つトレンチ16をSi基板10の主面に形成する。次に、トレンチ16の深さを測定する。トレンチ16の底面からSi基板10に酸素イオン18を注入する。この際に、測定したトレンチ16の深さと所望の深さの差に基づいて酸素イオン18の注入エネルギーを調整して、Si基板10の所望の深さに酸素イオン18が注入されるようにする。次に、熱処理を行って酸素イオン18を注入した位置にSiO2膜22を形成する。次に、SiO2膜22をエッチングストッパとして用いて、トレンチ16の底面からSi基板10を更にエッチングしてトレンチ24を形成する。その後、SiO2膜22を除去する。

(もっと読む)

ポリシリコン抵抗の設計方法及び半導体装置の製造方法

【課題】半導体装置のサイズの大型化を抑制しつつ、ポリシリコン抵抗の抵抗値が設計値からずれた場合に補正できるようにする。

【解決手段】ポリシリコン抵抗の設計方法は、シリサイド領域1bが両端にそれぞれ形成されたポリシリコンにより構成され、シリサイド領域1bがコンタクト3へ接続されるポリシリコン抵抗1の、抵抗値を判定する工程を有する。抵抗値が設計値よりも大きい場合には、コンタクト3の位置とポリシリコン抵抗1の形成範囲とを変更せずに、シリサイドブロック膜の形成範囲を狭める補正を行うことによって、ポリシリコン抵抗1の抵抗値を減少させる工程を行う。抵抗値が設計値よりも小さい場合には、コンタクト3の位置を変更せずに、ポリシリコン(シリサイドブロック領域1a)の幅を狭める補正を行うことによって、ポリシリコン抵抗1の抵抗値を増大させる工程を行う。

(もっと読む)

集積回路およびウェーハを試験する無線周波数技術構造および方法

【課題】集積回路を有するウェーハの無線試験を行うためのウェーハ上に形成された試験回路を含む装置および方法を提供する。

【解決手段】ウェーハ16の外部にある試験ユニット12、および集積回路を含むウェーハ上に製造された少なくとも1つの試験回路14を含む。試験ユニット12は、RF信号を送信し、試験回路14に電力を供給する。試験回路14は、可変リング発振器を含み、集積回路の公称動作周波数での一連のパラメータ試験を実行し、試験結果を分析のために試験ユニット12に送信する。

(もっと読む)

熱特性推定装置及び方法、並びに、温度推定装置及び方法、並びに、半導体装置

【課題】 半導体装置が装置に実装された状態での熱特性を求めて、ジャンクション温度の推定に適用する。

【解決手段】 本発明は、ジャンクション温度が制限温度を超えると、当該半導体装置の負荷を低下させる熱保護手段を備えた半導体装置の熱特性を推定する熱特性推定装置と、熱特性を利用して半導体装置のジャンクション温度を推定する温度推定装置に関する。そして、本発明の熱特性推定装置は、半導体装置のジャンクション温度が制限温度となる消費電力で半導体装置を動作させた状態で半導体装置の周囲の雰囲気温度を測定する手段と、測定した温度を利用して、半導体装置の熱特性を推定する手段とを有することを特徴とする。

(もっと読む)

半導体装置

【課題】積層型半導体装置において積層される半導体チップ間の接続テストにあたり、回路規模の拡大の抑制およびテスト時間の短縮を図る。

【解決手段】チップ200において、トランジスタTR11乃至14の組とTR21乃至23の組を貫通電極201a乃至201hに対して互いに1つずつずらして配置して接続する。制御電圧VDDと基準電圧VSSを最下層から各層のチップに対して印加した状態で、トランジスタTR11乃至14は、下層にチップが積層され、上層にチップが積層されないときにオンとなるように駆動する。トランジスタTR21乃至23は、下層および上層にチップが積層されているときにオンとなるように駆動する。これにより、最上層とその下の層のチップ間のマイクロバンプ210と220の接合部のコンタクトチェーンを形成する。接続テストはコンタクトチェーンの抵抗値を測定する。

(もっと読む)

半導体装置

【課題】内部回路に電源電位または接地電位を供給するための外部端子に関して、開放および短絡を検出可能にした半導体装置を提供する。

【解決手段】内部回路と、通常動作時に外部から印加される電源電位または接地電位を内部回路に供給するための第1の端子と、テスト結果を出力するための第2の端子と、第1の端子とは異なる端子から供給される電位により生成された所定の基準電圧と第1の端子の電位とを比較する比較部と、比較部からの出力をテスト結果として保持する第1のレジスタと、テスト結果を第1のレジスタから第2の端子に出力するテスト結果出力部とを有する構成である。

(もっと読む)

1 - 20 / 173

[ Back to top ]