Fターム[5F038DT13]の内容

Fターム[5F038DT13]の下位に属するFターム

冗長回路使用検出 (35)

Fターム[5F038DT13]に分類される特許

1 - 20 / 121

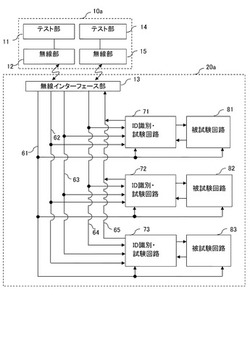

半導体集積回路、そのテスト方法及びテストシステム

【課題】テスト時間が短い半導体集積回路のテストシステム及びテスト方法を提供する。

【解決手段】本発明にかかる半導体集積回路20は、複数の被試験回路81乃至83を有し、外部のテストシステム10と無線で通信することにより、被試験回路81乃至83をそれぞれテストする複数のテストパターンに、被試験回路81乃至83を識別するIDが付加されたテスト入力信号を受信する無線インターフェース部13と、IDを識別し、IDに対応する被試験回路81乃至83に、IDが付加されたテスト入力信号に含まれるテストパターンを入力し、被試験回路81乃至83からテストパターンに応じたテスト結果が出力される度に、テスト結果に、IDを付加したテスト出力信号を、無線インターフェース部を介して、外部のテストシステム10に出力する試験回路と、を有するものである。

(もっと読む)

半導体装置

【課題】部分的な経年劣化の予兆を早期に発見することができる半導体装置を提供する。

【解決手段】LSI1は、複数のモジュールと、複数の遅延モニタを含む遅延モニタ群15とを備える。各遅延モニタは、複数段のゲート素子を有するリングオシレータを含む。各遅延モニタは、ゲート素子の遅延時間を測定する。CPU#0は、遅延モニタによって測定された遅延時間に基づいて、遅延モニタの近傍のモジュールの経年劣化を判定する。

(もっと読む)

半導体装置

【課題】無線通信により交信可能な半導体装置において、個体識別子を容易に付けることができるようにする。

【解決手段】薄膜トランジスタ119と、薄膜トランジスタ上に第1の層間絶縁膜156と、第1の層間絶縁膜上の、ソース領域またはドレイン領域の一方に電気的に接続される第1の電極114と、ソース領域またはドレイン領域の他方に電気的に接続される第2の電極110と、第1の層間絶縁膜、第1の電極、及び第2の電極上に形成された第2の層間絶縁膜135と、第2の層間絶縁膜上の、第1の電極または第2の電極の一方に電気的に接続される第1の配線177と、第2の層間絶縁膜上の、第1の電極または第2の電極の他方に電気的に接続されない第2の配線178とを有し、第2の配線と前記第1の電極または第2の電極の他方は、第2の層間絶縁膜中の分断領域169によって、電気的に接続されない半導体装置及びその作製方法に関するものである。

(もっと読む)

フィールドプログラマブルゲートアレイの性能を向上させるための装置および関連方法

【課題】性能が向上されたフィールドプログラマブルゲートアレイ(FPGA)を提供する。

【解決手段】フィールドプログラマブルゲートアレイ(FPGA)103であって、該FPGAは、該FPGA内の少なくとも1つの回路に対するプロセス、電圧、および温度の表示を提供するように適合された監視回路のセット115と、該少なくとも1つの回路に対するプロセス、電圧、および温度の該表示から該少なくとも1つの回路に対するボディバイアス値の範囲を導出するように適合されたコントローラ140と、該少なくとも1つの回路内の少なくとも1つのトランジスターにボディバイアス信号を提供するように適合されたボディバイアス生成器とを含み、該ボディバイアス信号は、該ボディバイアス値の範囲内の値を有する。

(もっと読む)

半導体集積回路

【課題】遷移スキャンテストにおいて遷移故障を短時間で精度良く検出できる半導体集積回路を提供する。

【解決手段】半導体集積回路1において、高速クロック動作ブロック(高速クロックグループ)及び低速クロック動作ブロック(低速クロックグループ)という、動作周波数の異なるブロック間にスキャンチェーンを配し、半導体集積回路1の遷移スキャンテストのキャプチャ動作時において、遷移スキャン用クロック制御回路7によって低速クロックグループのスキャンFFに供給されるクロックを止めるよう構成する。これにより、低速クロックグループのスキャンFFにおける信号マスクを不要にする。

(もっと読む)

半導体素子の破壊を検知する検知回路

【課題】監視対象の素子の破壊を直接的に検知することを可能にする。

【解決手段】監視対象の半導体素子近傍にモニタ用配線を敷設する一方、所定のクロックを出力するクロック出力手段を当該モニタ用配線の一端に接続し、同モニタ用配線の他端に監視手段を接続する。そして、クロック出力手段からモニタ用配線へ出力されるクロックを伝播を監視手段に監視させ、クロックの伝播が途絶えたことを検出した場合に、監視対象の半導体素子の破壊が生じた旨を通知する破壊通知信号を出力させる。

(もっと読む)

集積回路およびフィールド機器

【課題】パッケージの使用する端子を変更するときに、無駄な電力を消費せず、且つチップの設計を容易にして、値が不定な信号を生じないようにすることを目的とする。

【解決手段】本発明の集積回路1は、チップ3を搭載したパッケージ2に形成した入力、出力または入出力を行う端子11〜13と、チップ3に設けた機能ブロック4に端子11〜13からの信号を入力する入力バッファ31B〜33Bと機能ブロック4から端子11〜13に信号を出力する出力バッファ31C〜33Cとのうち少なくとも出力バッファ31C〜33Cを有するバッファ部31〜33と、端子11〜13が使用されていないときに、値が固定された固定信号を出力バッファ31C〜33Cに出力させる固定信号制御部41〜43と、を備えている。

(もっと読む)

半導体装置

【課題】複数の半導体チップの各々の信号端子が共通の外部端子に接続される場合であっても、半導体装置のオープン不良を検出する。

【解決手段】半導体装置は、複数の半導体チップと、外部と接続される電源端子、第1及び第2の外部端子と、を備え、複数の半導体チップのそれぞれは、第1の信号端子(第1の信号パッドT1)に供給される信号に基づくクロック信号によって計数を行うカウンタ部42と、複数の半導体チップの中で自己の半導体チップを固定的に識別し、識別情報を出力する識別情報認識部と、カウンタ部42の出力と識別情報を比較し、比較した比較結果に基づいて、第2の信号端子(第2の信号パッドT2)と電源端子との導通/非導通状態を制御する比較回路43と、を有し、複数の半導体チップの各々の第1の信号端子は、共通の第1の外部端子に接続され、複数の半導体チップの各々の第2の信号端子は、共通の第2の外部端子に接続される。

(もっと読む)

電子装置

【課題】大型化を招くことなく装置に関する情報を外部から好適に読み取り得る電子装置を提供する。

【解決手段】半導体チップ10は、装置に関する情報が外部から読み取り可能に記憶されるRFIDチップ30を搭載する回路ブロック11がモールド部材16によりモールドされてパッケージ化されている。このRFIDチップ30は、回路上に形成される複数のパッド13のうちモールド部材16によりモールドされた状態で外部に接続されていない検査用パッド20上に配置されている。

(もっと読む)

スキャンパス内蔵半導体集積回路

【課題】既存のテスト回路を用いて簡単な回路や制御を追加することでセキュリティ性を高める。

【解決手段】スキャンレジスタ方式の回路を保持したLSIにおいて、スキャン入力端子181〜183から入力したパスワードを、パスワード入力レジスタ101〜103に保持する。パスワード入力レジスタ101〜103とマスター・パスワード131〜133とをそれぞれ比較器111〜113で比較し、結果をパスワード判定回路100に送る。比較結果が全て一致していたら、スキャンパス・チェーン191〜193と出力バッファ151〜153との間の経路をスルーにする。逆に比較結果に不一致がある場合は、スキャンパス・チェーン191〜193と出力バッファ151〜153との間の経路を遮断する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】工程を追加せずに、アライメントマークの形成領域におけるゲート電極膜の残渣を低減する。

【解決手段】半導体装置の製造方法は、アライメントマーク10を有する第1領域R1と、抵抗体40が形成される第2領域R2と、ゲート電極15が形成される第3領域R3と、を主面1aに有する基板の主面1a上に、金属材料を含有するゲート電極膜11を形成する工程を有する。更に、第1及び第2領域R1、R2のゲート電極膜11を等方性エッチングにより除去する工程を有する。更に、ゲート電極膜11を除去した第2領域R2と、第3領域R3と、に導電膜(ポリシリコン膜13)を成膜する工程を有する。更に、導電膜を成膜する工程の後に、基板の主面1a上にフォトレジスト膜を形成し、アライメントマーク10をアライメントに用いて所定のパターンをフォトレジスト膜に転写する工程を有する。

(もっと読む)

半導体装置の製造方法

【課題】テスト時間の増加を防止しながら、低コストで、効率よく品種展開された半導体装置のテストを行う。

【解決手段】計算機3から、テストプログラム、テストパターン、および半導体装置のROMに書き込まれるROMファイルが、テスタ4に送信される。テスタは、品種固有テストであるRAM機能テスト、電源リーク測定、およびROMファイルを書き込むROM書き込みのそれぞれのテストの前に、ROMファイルに含まれるROMファイル番号が、’XXX’か、’YYY’かを判定し、テスト中の半導体装置が品種Aか、品種Bかを判定する。これら品種固有テストでは、品種の判定結果に基づいて、判定された品種に見合った規格値によるテスト判定が行われる。

(もっと読む)

半導体装置及びその製造方法

【課題】チップ面積を増大させることなく、半導体チップにそれぞれウエハのどの部分に位置していたのかを示す情報を付加した半導体装置及びその製造方法を提供する。

【解決手段】ウエハ上に所定の素子及び配線等を形成した後、パッシベーション膜を形成する。そして、このパッシベーション膜の表面に、ウエハ上の位置を示す位置情報パターンとして、溝を形成する。この溝は、ウエハから形成される複数に半導体チップに連続するパターンで形成され、例えば太線と細線とを組み合わせてX座標及びY座標を表す。

(もっと読む)

半導体装置

【課題】機能修正を行う場合でも速やかに製造することができるとともに、仕掛品の廃棄量を削減することが可能な半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、レビジョン信号発信回路が形成されたベース層と、前記ベース層上に積層された3層以上の配線層と、最上位の配線層に形成された電源配線あるいはグランド配線と、前記レビジョン制御回路を前記最上位の配線層の電源配線あるいはグランド配線にのみ接続するレビジョン信号線と、を備えている。

(もっと読む)

半導体装置および半導体装置アセンブリ

【課題】外部からの磁場を遮蔽する磁気シールド効果が高い半導体装置を提供する。

【解決手段】半導体基板SUBの主表面上に形成されたスイッチング素子TRを覆うように形成された層間絶縁膜III1と、平板状の引出配線LELと、引出配線LELとスイッチング素子TRとを接続する接続配線ICLと、磁化の向きが可変とされた磁化自由層MFLを含み、引出配線LEL上に形成された磁気抵抗素子TMRとを備える。磁化自由層MFLの磁化状態を変化させることが可能な配線DLと配線BLとを備えている。磁気抵抗素子TMRが複数並んだメモリセル領域において、磁気抵抗素子TMRの上部に配置された第1の高透磁率膜CLAD2が、上記メモリセル領域から、メモリセル領域以外の領域である周辺領域にまで延在している。

(もっと読む)

半導体装置およびその制御方法

【課題】電源遮断・復帰時に動作中の回路の誤動作を抑止しつつ、デバイスの製造ばらつきに応じて最適な速度での電源制御領域の電源遮断・復帰を可能とする半導体装置の制御技術を提供する。

【解決手段】半導体装置において、通常動作領域10と、電源制御領域20と、電源制御領域20に接続され、電源制御領域20への電源を供給または遮断する複数の電源スイッチSWとを有し、さらに、複数の電源スイッチSWのオンオフを制御し、半導体装置毎の製造後の性能に応じて電源遮断・復帰の遷移時間を変更し、電源遮断・復帰を行うスイッチ制御回路30を有する。さらに、半導体装置毎の製造後の性能を記録する記憶素子40を有する。

(もっと読む)

半導体集積回路および電子機器

【課題】不揮発性記憶素子にフューズ素子を用いた半導体集積回路において、目的とするデータと、検査データとしての目的とするデータの論理否定データとを記憶し、フューズ素子の不可逆性を利用することで、記憶回路と検証回路の回路規模をあまり大きくすることなく、またデータ検証の処理時間の増大を招くことなく、記憶データの信頼性と正真性を保証する。

【解決手段】記憶すべき情報を示す特定データを不可逆的に記憶する不揮発性記憶回路100aを有する半導体集積回路100において、該不揮発性記憶回路100aを、該特定データの非反転データを記憶する第1の記憶回路101と、該特定データの反転データを記憶する第2の記憶回路102とを有する構成とした。

(もっと読む)

半導体装置およびその製造方法

【課題】ダイシング時に、アクセサリパターンが剥離することを抑制する。幅の狭いスクライブラインを使用して、1枚の半導体基板から得る半導体チップの個数を増加させる。

【解決手段】半導体装置は、半導体チップと、半導体チップの周囲に接するように設けられ層間絶縁膜とアクセサリとを有するスクライブラインとを有する。アクセサリは、層間絶縁膜上に設けられた層状の第1の部分と、第1の部分から層間絶縁膜の厚み方向の下方に向かって伸長する第2の部分と、を有する。

(もっと読む)

半導体装置および配線用マスク判別方法

【課題】使用した配線用マスクを簡単かつ確実に判別でき、確認工数を削減する。

【解決手段】所定の配線パターンと共に両端に端子を備えた抵抗素子の複数41、42、43、を含む抵抗素子領域を形成するための所定配線用マスクを用いたリソグラフィステップと、半導体ウエハ特有の配線パターンと共に特有の配線パターンに応じて抵抗素子の端子間にて直列およびまたは並列接続された接続配線を含む識別領域50を形成するための識別配線51用マスクを用いたリソグラフィステップと、接続配線に接続され露出したパッド19を形成するためのパッド配線用マスクを用いたリソグラフィステップと、を含む。第1配線層および第2配線層の抵抗素子領域および識別領域の組がTEGチップまたはスクライブラインに形成されている。露出したパッドを介して抵抗素子の直列およびまたは並列接続された接続配線の抵抗値を測定するステップを更に含む。

(もっと読む)

半導体基板の製造方法

【課題】アライメントマークを形成する専用の工程の別途追加が無く、アライメントマークのサイズも自由に設定することができ、さらに、デバイス製造工程においてレジスト塗布斑やレジスト残り等の不具合を発生させない半導体基板の製造方法を提供する。

【解決手段】基板19を用意し、アライメントマーク領域15とPNコラム領域13とにアライメントマーク領域15のトレンチ幅がPNコラム領域13のトレンチ幅よりも広いトレンチ14、16を同時に形成する。続いて、PNコラム領域13のトレンチ14に単結晶半導体層21を完全に埋め込みつつアライメントマーク領域15のトレンチ16に隙間が残るように単結晶半導体層21の一部を形成する。この後、アライメントマーク領域15のトレンチ16内に空洞22が残るように当該トレンチ16を単結晶半導体層21で塞ぐ。

(もっと読む)

1 - 20 / 121

[ Back to top ]