Fターム[5F038DT14]の内容

Fターム[5F038DT14]に分類される特許

1 - 20 / 35

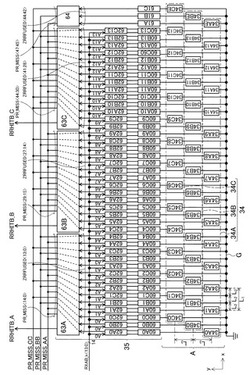

半導体装置及びトリミング方法

【課題】ヒューズ素子の列数増に伴うトリミング時間の伸長を抑制する。

【解決手段】x方向に延伸する接地配線Gと、接地配線のy方向の一方側に設けられたヒューズ素子領域Aにx方向に沿って3列に並べて配置され、かつそれぞれの一端が接地配線Gに共通に接続される複数のヒューズ素子と、ヒューズ素子領域Aを挟んで接地配線Gの反対側に設けられ、ヒューズ素子領域Aに配置された複数のヒューズ素子それぞれの他端と接続される救済回路とを備え、上記複数のヒューズ素子は、それぞれ1つの欠陥選択線を示すアドレス情報を記憶する複数のヒューズ素子グループに所定個ずつグループ化され、同一のヒューズ素子グループに属する所定個のヒューズ素子は、同一列に配置されることを特徴とする

(もっと読む)

半導体装置

【課題】半導体チップの面積を縮小することが可能な半導体装置を提供する。

【解決手段】半導体チップを有する半導体装置では、半導体チップに設けられた内部回路のテストを行うテスト回路と、そのテストが行われている間は内部回路を駆動せず、テストが行われた後に内部回路を駆動する駆動回路とを有し、内部回路に接続された信号線が、テスト回路と駆動回路とで共用される。

(もっと読む)

半導体ウエハ、半導体装置、および、半導体装置の製造方法

【課題】半導体チップのチップ面積の削減を図るとともに、半導体チップへの入力を記憶させる時間を短縮する。

【解決手段】本発明の半導体ウエハ1は、チップ領域10に形成され、絶縁膜を有し、電圧の印加による絶縁膜の絶縁破壊により導通状態となる複数のアンチヒューズ14を有するアンチヒューズ回路12と、チップ領域10を区画するダイシング領域20に複数のアンチヒューズ14の各々に対応して形成され、配線を有し、レーザー照射による配線の切断により非導通状態となる複数のレーザーヒューズ24を有するレーザーヒューズ回路22と、複数のアンチヒューズ14のうち、半導体チップへの入力に応じて非導通状態とされたレーザーヒューズ22に対応するアンチヒューズ14の有する絶縁膜に、電源からの電圧を印加させて、そのアンチヒューズ14を導通状態とする制御回路13と、を有する。

(もっと読む)

半導体装置

【課題】寿命が長い半導体装置を提供する。

【解決手段】このLSIは、2つのCPU1,2と、CPU1,2のうちのいずれか1つのCPUを示す論理レベルのデータ信号が書き込まれた記憶回路4と、リセット信号REが非活性化レベルにされてLSIのリセットが解除された場合、記憶回路4の記憶データの論理レベルに対応するCPUのみに電源電圧を供給するとともに、記憶回路4の記憶データを現在の論理レベルと異なる論理レベルのデータ信号に書き換える制御回路3,5とを備える。したがって、故障の検知や、厳密なタイミング制御を必要とせずに、CPUの長寿命化を図ることができる。

(もっと読む)

再構成可能な集積回路ユニットを備えた論理回路及びその論路回路のエラー修正方法

【課題】エラー箇所の特定を実施する際に、システムを停止しないでエラー発生前の高信頼性までシステム性能を復帰させる。

【解決手段】同一動作を行う複数個の再構成可能な集積回路ユニットを備え、複数の該集積回路ユニットのそれぞれに複数のバンクを有する論理回路において、入力されたデータを、複数個の前記集積回路ユニットの各バンクに振り分けて入力する入力データ制御部と、複数個の集積回路ユニットの各バンクから出力されるデータを比較して、データ間の不一致を検出するエラー解析部と、エラー解析部から、データ間の不一致の通知を受けた場合に、複数個の集積回路ユニットの該当するバンクの再構成を行う構成情報制御部と、を備える。

(もっと読む)

半導体集積回路

【課題】半導体集積回路において消費電力を低減するとともに、ノイズの発生を低減する。

【解決手段】半導体集積回路は、複数のDFFを有し、その少なくとも1つが冗長回路とされる。半導体集積回路が通常動作モードである際に、ANDゲート1によって冗長回路であるDFF3−3に印加されるクロック信号を停止する。冗長回路へのクロック信号が停止されると、当該冗長回路においてクロック信号が停止された状態における冗長回路のドレイン−グランド間容量よりもその容量を増加させる。

(もっと読む)

半導体集積回路及び電源電圧適応制御システム

【課題】フリップフロップを備える半導体集積回路において、エラーフリップフロップを効率的に検出する。

【解決手段】半導体集積回路は、冗長フリップフロップを含む複数のフリップフロップと、セレクタ部と、エラー検出部とを備える。セレクタ部は、再構成情報に応じて選択フリップフロップを選択し、入力端子に入力されたデータが選択フリップフロップのそれぞれによって出力端子に出力されるようにデータの流れを切り替える。テストモード時、フリップフロップはスキャンチェーンを構成し、そのスキャンチェーンにはスキャンデータが入力される。そして、エラー検出部は、それぞれのフリップフロップの入出力に基づいてエラーフリップフロップを検出し、当該エラーフリップフロップが選択フリップフロップから除外されるように再構成情報を作成する。

(もっと読む)

自己修正可能な半導体、および自己修正可能な半導体を備えたシステム

【課題】歩留りの向上を実現できる、自己修正可能な半導体を提供する。

【解決手段】自己修正可能な半導体は、同じ機能を実行しかつ副機能ユニットを有する、多数の機能ユニットを備える。半導体は、完全または部分的な1つ以上のスペア機能ユニットを備え、当該スペア機能ユニットは、半導体へと集積される、副機能ユニットの欠陥が検出されると、その副機能ユニットは、切り替えられて、完全または部分的なスペア機能ユニットにおける副機能ユニットと、置き換えられる。この再構成は、副機能ユニットと関連付けられたスイッチング・デバイスによって実現される。欠陥のある機能ユニットや副機能ユニットは、組立後に電源を投入している最中に動作中に周期的に検出されてよく、および/又は手動で検出してもよい。

(もっと読む)

半導体集積回路及び半導体集積回路の検査方法

【課題】メモリ及びメモリ周辺ロジック間のテストを、スキャンテストにて実現することができる半導体周期回路を提供する。

【解決手段】半導体集積回路は、メモリセル22〜25及び冗長セル26,27と、メモリセルに欠陥があった場合に冗長セルを選択するセレクタ28とを有するメモリ10と、外部からの情報に基づきセレクタに冗長セルを選択させるための第1の制御信号を生成する救済制御回路13と、救済制御回路13の第1の制御信号をラッチする救済情報保持ラッチ14と、を有する。そして、救済情報保持ラッチ14は、第2の制御信号に応じて救済制御回路13が生成した第1の制御信号をラッチする。

(もっと読む)

ヒューズ回路及びそれを備える半導体装置

【課題】ヒューズを含む電流経路で駆動される出力端の電圧レベルを所定の電圧レベルと比較できるヒューズ回路を提供すること。

【解決手段】本発明のヒューズ回路は、ヒューズイネーブル信号EN_ADDに応答してヒューズ412を含む電流経路を介して出力端COMを駆動するヒューズ部410と、所定レベルの基準電圧VREFと前記出力端の電圧レベルとを比較し、ヒューズ状態信号FOUTを生成する比較部450とを備える。

(もっと読む)

半導体装置

【課題】各機能モジュールに供給される電源電圧をプログラムによって変更可能な半導体装置を提供すること。

【解決手段】半導体装置1には、複数のプログラマブル機能モジュール(メモリ0〜N)15−0〜15−Nが搭載される。DC/DCコンバータ11は、複数の電源電圧(Vdd0〜Vdd2)を生成してPPSW13−0〜13−Nに出力する。PPSW13−0〜13−Nは、DC/DCコンバータ11によって生成された複数の電源電圧(Vdd0〜Vdd2)のいずれかを、プログラマブル機能モジュール15−0〜15−Nに選択的に接続する。したがって、プログラマブル機能モジュール15−0〜15−Nに供給される電源電圧をプログラムによって変更することが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、異なる種類の複数のヒューズを積層した構成や、当該構成に対する具体的な救済及び半導体装置の識別付与の製造方法を提供することを目的とする。

【解決手段】

本発明の1つの実施形態では、所定の電圧値を印加、又は所定の電流値以上を流すことで切断される第1ヒューズと、レーザ光を照射することで切断される第2ヒューズと、レーザ光を反射するリフレクタ層とを備える半導体装置である、さらに、本発明の1つの実施形態に係る半導体装置では、第1ヒューズ上に絶縁層を介してリフレクタ層を積層し、リフレクタ層上に絶縁層を介して第2ヒューズを積層する。

(もっと読む)

アンチヒューズ回路及びこれを備える半導体装置、並びに、アンチヒューズ回路へのアドレス書き込み方法

【課題】アンチヒューズ素子への書き込み処理を高速に行うことが可能なアンチヒューズ回路を提供する。

【解決手段】本発明によるアンチヒューズ回路は、不揮発的にデータを保持するアンチヒューズ素子330と、アンチヒューズ素子330に書き込むべきデータを一時的に保持するラッチ回路320とを備える。ラッチ回路320への書き込みはナノ秒オーダーで実行可能であることから、複数のチップにそれぞれ異なる不良アドレスを書き込む場合であっても、ラッチ回路320への書き込み処理を極めて短時間で完了することができる。これにより、アンチヒューズ素子330への実際の書き込み処理については、複数のチップについて並列に実行することができ、結果的にアンチヒューズ素子330への書き込み処理を高速に行うことが可能となる。

(もっと読む)

集積回路及び回路基板

【課題】集積回路とこの集積回路が実装された回路基板との間の信号伝送異常を低減させる。

【解決手段】複数の出力ピン3a,3bにそれぞれ接続され、接続されたいずれか1つの出力ピンへ出力信号を供給する複数のトライステートバッファ4a,4bと、複数の出力ピン3a,3bにそれぞれ接続され、接続された出力ピンから出力信号が供給され、又は複数のトライステートバッファ4a,4bのうち接続されたトライステートバッファから出力信号が供給される複数の入力バッファ5a,5bと、複数の入力バッファ5a,5bに供給された出力信号に基づいて、複数のトライステートバッファ4a,4bのいずれから出力信号を供給させるかを決定する送信信号正常性判定部6とを備える。

(もっと読む)

半導体装置および製造方法

【課題】面積効率を高めることが可能な半導体装置を提供すること。

【解決手段】所定層に形成された複数の導電体領域と、所定層の上層である絶縁層に形成され、少なくとも複数の導電体領域以外の領域を覆う絶縁膜領域と、絶縁膜領域に沿って形成され、複数の導電体領域間を接続する接続用配線と、を有する。

(もっと読む)

半導体装置

【課題】実装面積の増大を抑制し、処理速度不足の機能ブロックやロジック回路からなる機能ブロックも救済でき、消費電力の増大を抑えて電源設計を容易にすることが可能な半導体装置を提供する。

【解決手段】半導体装置は、主電源網を含む2系統以上の電源網と、複数の機能ブロックと、その複数の機能ブロックにおける1つ以上の機能ブロックの電源供給元とする電源網を主電源網以外の電源網に切り換える切換回路とを備える。

(もっと読む)

半導体集積回路

【課題】 半導体集積回路においては、アンチヒューズを利用した冗長回路が使用されている。これらのアンチヒューズの書き込みにはロングパルス、ロングサイクルのヒューズ書き込み制御信号が必要である。しかしテスター性能によりロングサイクルの信号が発生できず、テスターの有効活用ができないという問題がある。

【解決手段】 本発明の半導体集積回路は、テスターからのショートパルス信号を使って、ロングパルス、ロングサイクルのヒューズ書き込み制御信号を生成する内部信号生成回路を内蔵する。テスター性能に制限されることなく、内部信号生成回路により生成したロングパルス、ロングサイクルのヒューズ書き込み制御信号によりアンチヒューズへの書き込みを実施できる。そのためテスターの有効活用ができる。

(もっと読む)

半導体装置及びヒューズ素子の切断方法

【課題】信頼性を確保しつつヒューズ素子の配列ピッチを狭くすることが可能な半導体装置を提供する。

【解決手段】レーザビームの照射により切断可能な複数のヒューズ素子101〜105と、平面的に見て複数のヒューズ素子間に位置し、レーザビームを減衰可能な減衰部材140とを備える。減衰部材140は複数の柱状体によって構成されている。これにより、切断すべきヒューズ素子から半導体基板側へ漏れ出したレーザビームLは、複数の柱状体によって構成された減衰部材140によって吸収されるとともに、フレネル回折によって散乱する。これにより、このため、柱状体が過度のエネルギーを吸収することによって絶縁膜にクラックなどが生じることがなく、効率的にレーザビームを減衰させることが可能となる。

(もっと読む)

半導体装置のテスト方法

【課題】従来のテスト方法では、異なる条件で実行したテストの結果を比較していたために、レジスタや比較手段等の余分な回路が必要になる問題があった。

【解決手段】本発明にかかるテスト方法は、第1のテスト条件において検出手段で故障箇所を検出し、置き換え手段によって故障箇所を冗長回路に置き換える第1のステップ(ステップS1〜S5)と、第1のステップ完了後の状態を保持したままの半導体装置に対して、第1のテスト条件にて再度検出手段で故障箇所を検出する第2のステップ(ステップS6、S7)と、第2のステップにおいて、故障箇所が検出されなかった半導体装置に対して、第1のステップ完了後の状態を保持したまま、第2のテスト条件にて検出手段で故障箇所の検出を行う第3のステップ(ステップS8〜S10)と、第3のステップの結果に基づき半導体装置の良否判定を行う第4のステップ(ステップS11)とを有するものである。

(もっと読む)

半導体集積回路

【課題】ストラクチャードASICにおいて待機時の電力消費を削減することが可能な半導体集積回路を提供する。

【解決手段】M(Mは2以上の整数)列の回路部列と、任意の入力論理を一意に決めるルックアップテーブル(LUT)構造を有する(M−1)列のプログラム部列と、を有し、プログラム部列は、回路部列間に配置され、冗長前は、第1側に隣接する回路部列に接続される構造を有し、所定の回路部列に欠陥があると、欠陥回路部列が第1側に位置するプログラム部列から順次に配置されているプログラム部列は、第2側に隣接する回路部列と接続されるカラムシフト冗長方式によってセル配置が行われ、各回路部220は、構成素子ごとに電力を供給可能な構造を有し、回路部220において、回路動作に不要な構成素子は電源から切り離されている。

(もっと読む)

1 - 20 / 35

[ Back to top ]