Fターム[5F038DT15]の内容

Fターム[5F038DT15]に分類される特許

1 - 20 / 818

出力制御スキャンフリップフロップ、それを備えた半導体集積回路及び半導体集積回路の設計方法

半導体装置及びそのテスト方法

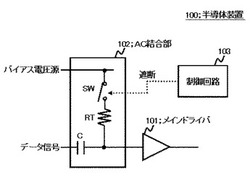

【課題】データ信号ラインにAC結合部が含まれる出力回路を備える半導体装置のDCテストの実施には、振幅を維持できないという問題がある。そのため、データ信号ラインにAC結合部が含まれる出力回路を備える半導体装置であって、DCテストを可能にする半導体装置が、望まれる。

【解決手段】半導体装置は、データ信号を外部に出力するメインドライバと、データ信号が伝達する配線と接続されているコンデンサと、一端がコンデンサと接続され、他の一端がバイアス電圧源に接続されている終端抵抗と、バイアス電圧源と終端抵抗との間に接続されている第1のスイッチと、を含むAC結合部と、テストモード時にAC結合部のバイアス電圧源と終端抵抗との接続を、第1のスイッチにより遮断する制御回路と、を備える。

(もっと読む)

半導体集積回路、そのテスト方法及びテストシステム

【課題】テスト時間が短い半導体集積回路のテストシステム及びテスト方法を提供する。

【解決手段】本発明にかかる半導体集積回路20は、複数の被試験回路81乃至83を有し、外部のテストシステム10と無線で通信することにより、被試験回路81乃至83をそれぞれテストする複数のテストパターンに、被試験回路81乃至83を識別するIDが付加されたテスト入力信号を受信する無線インターフェース部13と、IDを識別し、IDに対応する被試験回路81乃至83に、IDが付加されたテスト入力信号に含まれるテストパターンを入力し、被試験回路81乃至83からテストパターンに応じたテスト結果が出力される度に、テスト結果に、IDを付加したテスト出力信号を、無線インターフェース部を介して、外部のテストシステム10に出力する試験回路と、を有するものである。

(もっと読む)

論理回路の故障検出方法、テスト回路挿入方法、テスト回路挿入装置および半導体集積回路

【課題】 論理ゲートの一方の入力を含む信号パスの遅延故障と、論理ゲートの他方の入力を含む信号パスの遅延故障とを、1つの制御点により検出する。

【解決手段】 第1および第2ユーザロジックと、第1ユーザロジックの出力に接続される第1入力を有する第1論理ゲートと、第1論理ゲートの出力に接続された第3ユーザロジックと、第2ユーザロジックと第1論理ゲートとの間に挿入された制御点とを有する。制御点は、第1または第3ユーザロジックの第1スキャンフリップの1つのデータ出力がデータ入力に接続された第2スキャンフリップフロップと、一対の入力が第2スキャンフリップフロップのデータ出力および第2ユーザロジックの出力にそれぞれ接続され、出力が第1論理ゲートの第2入力に接続された第2論理ゲートとを有する。

(もっと読む)

スキャン・チェーン用動的クロック領域バイパス

【課題】スキャン・テスト回路およびスキャン・テスト回路を使用して試験を受けるさらなる回路を備える集積回路を提供すること。

【解決手段】スキャン・テスト回路は、それぞれ別個のクロック領域に関連した複数のサブチェーンを有する少なくとも1つのスキャン・チェーン、および1つまたは複数のサブチェーンを選択的にバイパスするように構成されたクロック領域バイパス回路を備える。スキャン・チェーンは、スキャン・シフト・モードの動作において、サブチェーンを全部よりは少なく含む直列シフト・レジスタを形成するように構成可能であり、サブチェーンの少なくとも残りの1つが、スキャン・シフト・モードにおいて直列シフト・レジスタの部分でないように、クロック領域バイパス回路によりバイパスされる。特定のクロック領域に関連するスキャン・チェーンの部分を選択的にバイパスすることにより、クロック領域バイパス回路は、スキャン・テスト期間の試験時間と電力消費を減らす役割を果たす。

(もっと読む)

半導体装置

【課題】半導体チップの面積を縮小することが可能な半導体装置を提供する。

【解決手段】半導体チップを有する半導体装置では、半導体チップに設けられた内部回路のテストを行うテスト回路と、そのテストが行われている間は内部回路を駆動せず、テストが行われた後に内部回路を駆動する駆動回路とを有し、内部回路に接続された信号線が、テスト回路と駆動回路とで共用される。

(もっと読む)

半導体装置

【課題】 貫通ビアを用い積層した半導体装置においては、信号を伝送する貫通ビアがオープンやショートした場合に、その貫通ビアを回避して積層チップ全体を正常動作させるために、複雑な回路を構成が必要であった。

【解決手段】 信号を伝送する貫通ビアにおいて、ビアの内壁を構成するシリコンに高い不純物の領域を形成して貫通導体とシリコン基板が接触したときに基板に接続されているVSSなどの基準電位に誘導する。故障モードを固定できるため、冗長化/復号化回路が簡単になるうえ、必要な冗長貫通ビアの本数を削減することができる。

(もっと読む)

半導体ウエハ、半導体ウエハ検査装置、及び半導体ウエハの検査方法

【課題】本発明は、半導体ウエハの検査において、半導体ウエハの裏面電極の端子としての機能を維持しつつ、半導体ウエハに過度の力がかかることを防止できる半導体ウエハ、半導体ウエハ検査装置、及び半導体ウエハの検査方法を提供することを目的とする。

【解決手段】本発明に係る半導体ウエハは、ダイシングラインを隔てて複数のチップが並ぶ半導体ウエハの表面側に形成された表面電極と、該半導体ウエハの裏面側に、該ダイシングラインを隔てて形成された複数の裏面電極と、該半導体ウエハの裏面側に、該ダイシングラインを跨いで該複数の裏面電極を電気的に接続する接続パターンと、を備える。該複数の裏面電極のうちの少なくともひとつは、該半導体ウエハのバイアホールを介して該表面電極と電気的に接続される。

(もっと読む)

マルチICデバイスをテストするための方法および装置

【課題】マルチICデバイスをテストするための方法および装置を提供する。

【解決手段】集積回路は、入力信号を受け取るように構成される第1の入力相互接続と、テスト・イネーブル信号を受け取るように構成される第1のテスト・イネーブル相互接続と、前記入力信号に対応する値に基づいて該集積回路のテストを実行するためのコントローラと、入力ポートと、前記第1の入力相互接続、前記コントローラ、および前記入力ポートに結合され、前記テスト・イネーブル信号がアサートされていないことに応答して前記入力信号を前記入力ポートに渡し、前記テスト・イネーブル信号がアサートされていることに応答して前記入力信号を前記コントローラに渡すように制御可能である第1のマルチプレクサとを備える。

(もっと読む)

半導体集積回路及びそのテスト方法

【課題】プローブ針を接触させる外部端子の数を抑制してDCテストを行うことが可能な半導体集積回路を提供すること

【解決手段】本発明にかかる半導体集積回路は、入出力端子P1を介して外部にデータを出力する出力バッファ21と、外部から入出力端子P1を介してデータが入力される入力バッファ22と、入出力端子P1と入力バッファ22の入力との間の信号線上のノードN1と第1入力端子T1との間に設けられたスイッチ26と、外部から第2入力端子T2に供給される第2基準電位とノードN1の電位とを比較して比較結果を出力する比較部23と、入力バッファ22から出力されるデータと比較部23の比較結果との何れかを選択しテスト結果として出力する選択部52と、を備える。

(もっと読む)

半導体テスト回路

【課題】スキャンチェーンを構成する回路でバーンイン試験を行う際に、シフトモードとキャプチャモードを切り替えるスキャンモードコントロール信号が接続された回路に対してもストレス印加を可能にする半導体テスト回路を提供する。

【解決手段】半導体テスト回路は、シフトモードとキャプチャモードを交互に切り替える内部スキャンモードコントロール信号と、スキャンチェーンのスキャンフリップフロップ回路に供給する内部クロック信号を生成するスキャンチェーン制御信号生成部を備える。スキャンチェーン制御信号生成部は、スキャンフリップフロップ回路の出力を遷移させる内部クロック信号のエッジのタイミングにおいて、内部スキャンモードコントロール信号がシフトモードになるように、内部スキャンモードコントロール信号と内部クロック信号の相互のタイミングを制御する。

(もっと読む)

半導体装置

【課題】

実施形態は、解析が簡便な半導体装置を提供する。

【解決手段】

本実施形態の半導体装置は、内部信号を伝送可能な第1配線101と、第1配線101

と電気的に接続された測定電極100と、測定電極100と隣接するように配置され、内

部信号を計測するときに接地電位VSSが印加され、内部信号を計測する以外のときに所

望の電圧が印加されたダミー電極102,103とを備える。

例えば、測定電極100は、環状に形成されており、ダミー電極は、第1電極102と

第2電極103とを有し、第1電極102は、測定電極100の内側に形成された空間に

隣接するように配置され、第2電極103は、測定電極100の外側に隣接するように配

置される。

(もっと読む)

半導体集積回路のテスト回路及びテスト方法

【課題】外部端子数の増加を抑えつつ、半導体集積回路のテスト時間を短縮する。

【解決手段】テスト回路は、入力されるリファレンスクロック109を逓倍して、テスト対象回路106をテスト動作させるための実動作クロック112及びサンプリングクロック105を生成するPLL108と、入力されるテストコマンドに従い、テスタ同期クロック103に同期してテスト対象回路106のテスト結果を出力するテスト結果出力回路107と、を備えるテスト回路であって、テストコマンドを含むテスト入力信号104とサンプリングクロック105とに基づきテスタ同期クロック103を生成するテスタ同期クロック生成回路100を備えるものである。

(もっと読む)

半導体装置

【課題】寿命が長い半導体装置を提供する。

【解決手段】このLSIは、2つのCPU1,2と、CPU1,2のうちのいずれか1つのCPUを示す論理レベルのデータ信号が書き込まれた記憶回路4と、リセット信号REが非活性化レベルにされてLSIのリセットが解除された場合、記憶回路4の記憶データの論理レベルに対応するCPUのみに電源電圧を供給するとともに、記憶回路4の記憶データを現在の論理レベルと異なる論理レベルのデータ信号に書き換える制御回路3,5とを備える。したがって、故障の検知や、厳密なタイミング制御を必要とせずに、CPUの長寿命化を図ることができる。

(もっと読む)

再構成可能な集積回路ユニットを備えた論理回路及びその論路回路のエラー修正方法

【課題】エラー箇所の特定を実施する際に、システムを停止しないでエラー発生前の高信頼性までシステム性能を復帰させる。

【解決手段】同一動作を行う複数個の再構成可能な集積回路ユニットを備え、複数の該集積回路ユニットのそれぞれに複数のバンクを有する論理回路において、入力されたデータを、複数個の前記集積回路ユニットの各バンクに振り分けて入力する入力データ制御部と、複数個の集積回路ユニットの各バンクから出力されるデータを比較して、データ間の不一致を検出するエラー解析部と、エラー解析部から、データ間の不一致の通知を受けた場合に、複数個の集積回路ユニットの該当するバンクの再構成を行う構成情報制御部と、を備える。

(もっと読む)

半導体集積回路、半導体集積回路の設計支援方法、及び設計支援プログラム

【課題】クロックゲーティング回路を搭載した半導体集積回路の回路規模の増大を抑制しながら、テスト時の消費電力を低減する。

【解決手段】本発明による半導体集積回路は、第1フリップフロップ回路5、第2フリップフロップ回路7、制御回路3、及びクロックゲーティング回路2を具備する。第1フリップフロップ5は、スキャンシフトによって第1データを格納する。第2フリップフロップ7は、スキャンシフトによって第2データを格納する。第3制御回路3は、第1データとスキャンイネーブル信号SMCとの論理演算結果と、第2データと組合せ回路9からの第1イネーブル信号EN1との論理演算結果との論理演算結果をゲート制御信号C1として出力する。クロックゲーティング回路2は、ゲート制御信号C1に応じて次段のフリップフロップ回路1へのクロック信号CLKの伝播を制御する。

(もっと読む)

集積回路

【課題】集積回路において電力消費量を容易に低減する。

【解決手段】集積回路は、クロック分配回路、同期動作回路、論理回路、および、電源供給部を備える。クロック分配回路は、所定のタイミングを指示するクロック信号を分配する。同期動作回路は、クロック信号に同期して動作する。論理回路は、同期動作回路の動作結果に基づいて所定の論理演算を実行する。電源供給部は、クロック分配回路を駆動させるクロック分配回路駆動電圧より低い電圧を論理回路に論理回路駆動電圧として供給する。

(もっと読む)

プローブカード、半導体装置、半導体装置の試験方法、及び、半導体装置の製造方法

【課題】差動伝送方式を採用した半導体装置の試験で行われるTDRタイミング測定の校正精度の低減を抑制すること。

【解決手段】複数のプローブ針を有し、プローブ針を半導体装置の電極パッドと接続させて所定の試験を行うためのプローブカードであって、互いに異なる電極パッドP1及びP2に接続するよう配置され、対となっている差動信号入力用の第1及び第2のプローブ針1a及び2aと、互いに異なる電極パッドP1及びP2に接続するよう配置された第3及び第4のプローブ針1b乃至2b´と、第3及び第4のプローブ針1b乃至2b´各々と接続して、第3及び第4のプローブ針1b乃至2b´を導通させる配線3及び抵抗部材RTと、を有し、第3及び第4のプローブ針1b乃至2b´、配線3及び抵抗部材RTは電気的にフローティングな状態となっている。

(もっと読む)

鍵格納回路、半導体集積回路、及びシステム

【課題】格納された鍵の値の推測を困難にすることができる、鍵格納回路、半導体集積回路、及びシステムを提供する。

【解決手段】LSI10に搭載された鍵格納ブロック20は、k個のヒューズメモリセル30を有するヒューズブロック22と、鍵生成回路24と、を備えており、ヒューズブロック22からは予め実装されているビット長kの固定出力値fout[k−1:0]が出力される。鍵生成回路24は、レジスタ及び復号器を含んで構成されており、復号器は、演算処理により、固定出力値fout[k−1:0]と、レジスタの出力値と、からビット長n(n>k)の鍵key[n−1:0]を生成して出力する。

(もっと読む)

出力制御スキャンフリップフロップ、それを備えた半導体集積回路及び半導体集積回路の設計方法

【課題】制御信号を必要とせずにスキャンテスト時のピーク消費電力を低減することが可能な出力制御スキャンフリップフロップを提供すること。

【解決手段】本発明にかかる出力制御スキャンフリップフロップは、通常動作時に第1データを、シフト動作時にテストデータを、クロック信号に同期して取り込んで出力するスキャンフリップフロップ203と、シフト動作時にスキャンフリップフロップ203から出力されたデータを、クロック信号に同期して取り込んで出力するスキャンフリップフロップ204と、通常動作時にスキャンフリップフロップ203から出力されたデータを出力データとして生成し、シフト動作時にスキャンフリップフロップ203,204からそれぞれ出力されたデータに基づいて論理値変化率の低い出力データを生成するゲーティング回路と、を備える。

(もっと読む)

1 - 20 / 818

[ Back to top ]