Fターム[5F064FF21]の内容

ICの設計・製造(配線設計等) (42,086) | 切り換え、選択 (3,709) | 切り換え、選択部分の素子 (1,619)

Fターム[5F064FF21]の下位に属するFターム

Fターム[5F064FF21]に分類される特許

1 - 6 / 6

再構成可能集積回路

【課題】基本の回路要素の基本タイルの間の配線状態を設定する複数のプログラマブル配線スイッチが不揮発性記憶素子で構成される再構成可能集積回路を提供する。

【解決手段】再構成可能集積回路は、複数の入力端子と出力端子を備えるマルチプレクサ型のプログラマブル配線スイッチを構成する複数の不揮発性記憶素子を備える。入力端子から出力端子への信号電圧の伝搬経路にスイッチ機能を有する電界効果トランジスタ構造の不揮発性記憶素子が配置されており、不揮発性記憶素子が入力端子からの信号電圧を選択的に出力端子に伝搬するマルチプレクサ型のプログラマブル配線スイッチを構成するため、不揮発性記憶素子に対して導通状態もしくは非導通状態とする結線情報を記憶する書き込み動作、結線情報を消去する消去動作と、不揮発性記憶素子の導通状態もしくは非導通状態を確認する読み出し動作を直接行う制御回路を備える。

(もっと読む)

回路装置および制御方法

【課題】イオン伝導層を用いたイオン伝導素子をより高速に動作させる。

【解決手段】第1電極101と、第2電極102と、第1電極101および第2電極102の間に配置されたイオン伝導層103とを備えるイオン伝導素子と、このイオン伝導素子に、正電圧の印加および負電圧の印加を行うことでイオン伝導素子の動作を制御する両極動作制御部104と、第1電極101に、異なる電圧の負電圧を印加することでイオン伝導素子の動作を制御する単極動作制御部105とを備える。

(もっと読む)

プログラマブル論理回路

【課題】配線の複雑化なく、短時間かつ容易に、論理の再構成を行う。

【解決手段】本発明の例に関わるプログラマブル論理回路は、第1の電源ノードN1と出力ノードO1との間に接続され、磁気固着層と磁気記録層の磁化方向の相対関係に応じてコンダクタンスが変化する第1のトランジスタSPと、第2の電源ノードN2と出力ノードO1との間に接続され、第1のトランジスタSPのコンダクタンスの最大値と最小値との間の値にコンダクタンスが設定される第2のトランジスタSNと、第3の電源ノードN3と出力ノードO1との間に直列接続される第3のトランジスタT1及び抵抗素子R1とを備える。入力信号A,Bを与え、かつ、第1及び第3の電源ノードN1,N2の間にスピン注入電流を流している状態で、出力ノードO1に出力される出力信号Yの検証を行う。

(もっと読む)

集積回路チップ上で電気的な機能を実行する方法、集積回路構造、および半導体構造を製造する方法

【課題】スペクトルに基づいて選択された外部光活動化によるチップに埋め込まれたフォトダイオードの活動化を通してヒュージング操作などの電気的な機能を実行する方法、ならびに対応する構造および回路を提供すること。

【解決手段】本発明は、集積回路への追加の回路素子に関連して、特定の強度/波長特性を有する入射光が、修復の実施を実行するようにする、すなわち歩留りまたは信頼性あるいはその両方のために欠陥回路素子を冗長回路素子に置き換え、さらに、この入射光が、パッケージ化されたチップがシステム内に配置された後にESD保護デバイスを入力パッドから切り離すようにすることに基づく。パッケージ上の追加のピンは不要である。

(もっと読む)

半導体装置及び製造方法

【課題】装置に対する外部入力によってキャパシタの絶縁膜が破壊されない半導体装置とその製造方法を提供する。

【解決手段】

半導体装置10の絶縁膜17は、P型半導体領域12上に第1易破壊領域17aを備え、N+型半導体領域13上に第2易破壊領域17bとを備える。P型半導体領域12と第1易破壊領域17aとキャパシタ電極20とは、リークパス部を構成する。N+型半導体領域13と第2易破壊領域17bとキャパシタ電極20とはMOSキャパシタを構成する。N型半導体基板11には電極22を介して電源電圧Vddが印加されているため、外部入力があった場合ダイオードの整流作用からリークパス部を電流が流れやすくなり、プログラミング目的以外で第2易破壊領域17bが破壊されるのを防ぐことができる。

(もっと読む)

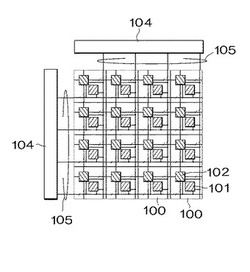

半導体チップおよびその製造方法

【課題】 ヒューズを有する半導体チップを製造する際のTATを短縮するとともに、信頼性の高い半導体チップを提供する。

【解決手段】 第二の半導体チップ100は、第一の論理回路102aおよび第二の論理回路104aを含む。第二の半導体チップ100は、第一の論理回路102aに電気的に接続された第一の端子108と、第二の論理回路104aに電気的に接続された第二の端子112と、第一の端子108と第二の端子112との間に形成された被切断領域110とを有するヒューズ106と、ヒューズ106の第一の端子108および第二の端子112と同一のパターンを有するとともに、第一の端子108および第二の端子112に対応するパターン(第一の残存部120および第二の残存部121)が電気的に接続されていない構成のヒューズ残存部118と、を含む。

(もっと読む)

1 - 6 / 6

[ Back to top ]