Fターム[5F064EE51]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 特定用途向け配線 (1,859)

Fターム[5F064EE51]の下位に属するFターム

電源、接地配線 (1,005)

ボンディングパッド用配線 (231)

クロック用配線 (448)

Fターム[5F064EE51]に分類される特許

1 - 20 / 175

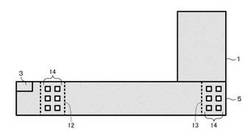

ダミーパターンの設計方法

【課題】金属配線パターンの寄生抵抗を低減可能なダミーパターンの設計方法を提供する。

【解決手段】切り欠きパターン2を一及び逆方向に各所定値Δx1だけ縮小して縮小図形4を生成した後、各所定値Δx1だけ拡大してダミーパターン5を生成し、その外形を抽出して矩形図形6を生成した後、各所定値Δx1だけ縮小して縮小図形7を生成し、ダミーパターン5から縮小図形7を論理減算して切り欠き図形8及び矩形図形9を生成し、切り欠き図形8を抽出してダミーパターン5から論理減算して矩形図形10を生成した後、各所定値Δx1だけ縮小して縮小図形11を生成し、矩形図形10から縮小図形11を論理減算して第1,第2のビア配置領域12,13を生成し、各ビア配置領域12,13にビア14をそれぞれ配置する。

(もっと読む)

設計支援装置

【課題】配線レイアウトのパターン形状に依存した効果をLPEに容易に取込む。

【解決手段】半導体集積回路の設計支援装置は、図形演算機能を有する第1の情報処理部110と、第2の情報処理部120とを備える。第1の情報処理部110は、レイアウト情報に含まれる各配線層のレイアウトパターンに対して図形演算を施すことによって、予め定める特定形状の配線パターンを抽出する。第2の情報処理部120は、製造プロセスに依存した配線または配線層間の絶縁層の厚みの設計値からのずれの大きさを、レイアウト情報から抽出した配線幅および配線密度の情報と、抽出された特定形状の配線パターンに関する情報とに基づいて予測する。そして、第2の情報処理部120は、予測した設計値からのずれの大きさを取り入れた配線および配線層間の絶縁層の厚みに基づいて、配線の寄生パラメータを抽出する。

(もっと読む)

配線設計装置、配線設計方法、及びプログラム

【課題】半導体集積回路に対し、ダミーパターン配置後に、ダミーパターンを使用したECO(Engineering Change Order)配線設計を行う。

【解決手段】配線設計装置は、半導体集積回路にダミーパターンを配置し、ダミーパターンをECO配線に変更し、ダミーパターンの再配置及び電気的ショートを発生することなくECO配線を行う。これにより、ECO配線を行う時に、ダミーパターン再挿入や、既存配線とのショートを発生せずに、設計TAT(Turn Around Time)増を抑制することを可能とする。

(もっと読む)

半導体集積回路、半導体集積回路の設計方法、および半導体集積回路の設計装置

【課題】配線層に形成される信号配線をなるべく迂回させずに配線できるように電源スタックビアが配置された半導体集積回路を提供すること。

【解決手段】半導体集積回路は、第1の方向に延伸された第1,第2の下層電源配線11A,11Bと、第2の方向に延伸された第1,第2の上層電源配線12A,12Bと、上層,下層電源配線を接続させる第1,第2接続部3A,3Bと、を備え、第1,第2接続部は、第1,第2の接続用配線26A,26Bと、第1,第2の位置変換用配線27A,27Bと、第1,第2の上側ビア28A,28Bと、を有して構成され、第1,第2の接続用配線は、第2の方向に沿った同一ライン上に配置され、第1,第2の位置変換用配線は、第1,第2の接続用配線を第2の方向に沿って延長した領域内に形成され、第1,第2の上側ビアは、第1の方向に沿った同一ライン上となる位置に配置される。

(もっと読む)

半導体装置及びその製造方法

【課題】トリミングや冗長に用いられるヒューズを有する半導体装置に関し、安定且つ確実に溶断しうるヒューズを有する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上に、第1の絶縁膜を形成し、第1の絶縁膜上に、ヒューズを形成し、ヒューズが形成された半導体基板上に、第1の絶縁膜に接して第2の絶縁膜を形成し、ヒューズ上の第2の絶縁膜に、開口部を形成し、第2の絶縁膜上及び開口部内に第3の絶縁膜を形成する。

(もっと読む)

発振器

【課題】 発振器に含まれる複数の遅延反転増幅回路の配線容量を高い精度で一定にすることにより、容易に正確、かつ高周波数の多相クロックを生成できる発振器を提供する。

【解決手段】 リング状に接続された遅延反転増幅回路101〜105を、1列にレイアウトし、かつ、遅延反転増幅回路102の出力端子から103の入力端子までの配線長と、遅延反転増幅回路103の出力端子から104の入力端子までの配線長と、遅延反転増幅回路104の出力端子から105の入力端子までの配線長と、遅延反転増幅回路105の出力端子から101の入力端子までの配線長と、遅延反転増幅回路101〜105の出力端子と接続されている配線の配線長を全て等しくする。

(もっと読む)

半導体装置及びそのレイアウト方法

【課題】再配線層形成工程、メタルポスト形成工程及び樹脂封止工程を経てウェハレベルで樹脂封止される半導体装置について、パッケージング工程で発生する応力を利用してPMOSFETの電流駆動能力を制御する。

【解決手段】メタルポスト21の形成に起因して半導体基板に圧縮応力が生じる範囲内にPMOSFET31が配置されている。PMOSFET31はそのチャネル方向がメタルポスト23の配置範囲の重心O及びPMOSFET31のチャネル領域の配置範囲の重心Gを通る直線と直交する向きに配置されている。重心Gで、メタルポスト21の形成に起因して半導体基板に生じる圧縮応力は、重心Gの位置で、重心Gと中心Oを通る直線に直交する方向に印加される。重心Gでの圧縮応力の方向とPMOSFET31のチャネル方向は一致するので、PMOSFET31の電流駆動能力は、当該圧縮応力が印加されない場合に比べて向上する。

(もっと読む)

信頼性を改良するための導電性層間のビア

【課題】ビアの信頼性を改良するための技術を提供する。

【解決手段】別の半導体デバイスが、複数の導電性配線(12−20)を含む第1層(21)および第2層(33)を含み、複数の非機能的ビアパッド(34)が、第2層または第1層と第2層との間に含まれる。複数のダングリングビア(40)は、第1層の特定の領域内に含まれる。ダングリングビアは、第1層の1つまたは複数の配線をビアパッドの対応する一つに接続する。

(もっと読む)

レイアウト設計装置、レイアウト設計方法およびプログラム

【課題】配線およびダミーパターンが配置された領域の割合を各メタル層において均一に保ちつつ、ダミーパターンの生成によって生じたタイミングエラーを解消できるようにすること。

【解決手段】レイアウト設計装置は、配線およびダミーメタルが配置されたメタル層において、エラーを生じた配線の周囲に配置された複数のダミーメタルの中から該エラーの原因となったダミーメタルを抽出し、該メタル層を分割して得られた複数の領域のそれぞれにおいて、配線およびダミーメタルを含むメタルが占める割合であるメタル密度が該メタル層に対して規定された所定のメタル密度以上となるようにしつつ、該エラーが解消されるように、抽出したダミーメタルの中から削除すべきダミーメタルを選択するダミーメタル選択部と、選択されたダミーメタルを削除するダミーメタル変更部と、を備えている。

(もっと読む)

レイアウト修正・ライブラリセル置換モジュール及び半導体装置設計用EDAツール

【課題】効率的に検出率を向上する方法及び未検出箇所が不良になる確率を低減させる手法により、多層配線層の検査工程を含む半導体製品の製造技術において、検査の迅速性を損なうことなく、半導体製品の製造歩留まりを向上させる技術を提供する。

【解決手段】不良の検出が困難な未検出領域について、パターン等の変更を行い検出率、致命率の改善を行う。例えば、検出が困難な未検出領域についてパターンを追加することで検出可能とする、パターンの間隔を広げることで不良率を低下させることなどが考えられる。

(もっと読む)

集積回路デバイス

【課題】プロセス寸法の縮小に伴う光相互作用の予測品質の低下を抑止する。

【解決手段】ゲートレベル仮想格子の、連続的に隣接して配置された少なくとも3本の仮想ラインのそれぞれは、その上に定義された少なくとも1つの線形導電体形状を有し、ゲートレベル仮想格子の少なくとも3本の仮想ラインの第1の仮想ラインは、その上に定義され、第1の終端−終端間スペーシングで分離された2つの線形導電体セグメントを有し、ゲートレベル仮想格子の少なくとも3本の仮想ラインの第2の仮想ラインは、その上に定義され、第2の終端−終端間スペーシングで分離された他の2つの線形導電体セグメントを有し、第1の仮想ラインに沿って測定された第1の終端−終端間スペーシングの寸法は、第2の仮想ラインに沿って測定された第2の終端−終端間スペーシングの寸法に等しく、ゲートレベル仮想格子の仮想ラインは、いかなる導電体形状によっても占有されない。

(もっと読む)

半導体装置及びその製造方法

【課題】ヒューズ配線を溶断する際に素子分離構造や半導体基板に与えるダメージを抑制することができる半導体装置を提供する。

【解決手段】半導体装置1は、半導体基板10と、半導体基板の主面の面内方向に互いに離間するように形成された一対の電極12A,12Bと、これら電極12A,12Bを被覆し、上面に凹部13cを有する下層絶縁膜13と、凹部13cに形成されたヒューズ配線20Cと、下層絶縁膜13及びヒューズ配線20Cを被覆する層間絶縁膜21と、層間絶縁膜21上に形成され、ヒューズ配線20Cの直上にレーザトリミング用の開口部1hを有する上層絶縁膜31とを備える。

(もっと読む)

半導体装置、パターンレイアウト作成方法および露光マスク

【課題】 高集積化に有効な複数の配線パターンを含む配線パターン群を備えた半導体装置を提供すること。

【解決手段】 同一の配線用途のN(N≧3)本の配線パターンを含む配線パターン群を含む。N本の配線パターンの各々は別の層の配線郡内の配線パターンと電気的に接続するための接続領域を含む。N本の配線パターンは、配線パターンN1と、配線パターンN1の長手方向と異なる一方向に配置された二つ以上の配線パターンNi(i≧2)を含む。二つ以上の配線パターンNiはiの値が大きいほど配線パターンN1から離れた位置に配置され、二つ以上の配線パターンNiは少なくとも一つ以上のパターンNp(2≦p<N)と少なくとも一つ以上の配線パターンNq(p<q≦N)を含む。少なくとも一つ以上の配線パターンNpはpの値が大きいほど長手方向の寸法が長く、少なくとも一つ以上の配線パターンNqは、qの値が大きいほど、長手方向の寸法が短い。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、ヒューズ層を覆う絶縁膜の膜厚を精度良く調整する。

【解決手段】半導体基板10上の第2の層間絶縁膜17上にヒューズ層18Tが形成され、ヒューズ層18Tは第3の層間絶縁膜20で覆われる。第3の層間絶縁膜20上には、キャップメタル24に覆われたパッド電極23が形成され、それらは第1及び第2のパッシベーション膜25,26に覆われる。次に、ヒューズ層18T上で開口する第1のレジスト層27をマスクとして、ヒューズ層18T上で第2のパッシベーション膜26から第3の絶縁膜の厚さ方向の途中までをエッチングする。その後、パッド電極23上で開口する第2のレジスト層30をマスクとして、パッド電極23上で第1及び第2のパッシベーション膜25,26及びキャップメタル層24をエッチングしてパッド電極23の表面を露出する。その後、保護膜32を形成する。

(もっと読む)

半導体装置

【課題】本発明は、工程を増やすこと無く、ヒューズカット時間を短縮することができる半導体装置を提供する。

【解決手段】半導体装置は、ヒューズ配線(10)と、加熱用配線(21、22)とを具備し、ヒューズ配線(10)と加熱配線(21、22)とに電圧を印加してヒューズ配線の溶断部を切断する。ヒューズ配線(10)は、回路素子を形成する配線層と同じ層に形成され、電気的に切断されうる溶断部を備える。加熱用配線(21、22)は、回路素子を形成する配線層と同じ層のうちのヒューズ配線(10)より上層の配線層に絶縁層を介して溶断部を複数回横断するように形成され、溶断部の配線幅より広い配線幅を有して溶断部を加熱する。

(もっと読む)

ダミーメタル配置評価装置、ダミーメタル配置評価方法及びダミーメタル配置評価プログラム

【課題】配線オブジェクトの敷設方向に対してずれを持たせたダミーメタルの配置を評価すること。

【解決手段】ダミーメッシュ情報作成部21は、配線オブジェクトの方向に対してずれを設けて規則的に配置したダミーメタルのブロック群を、各メッシュ内のダミーメタルの配置が同一となるようにメッシュ形状に分割する。重複判定部23は、分割によって得られた複数のダミーメッシュについて、配線オブジェクトとメッシュ内のダミーメタルのブロックとの重複を判定する。判定の結果、配線オブジェクトと重複するダミーメタルのブロックを除去したダミー情報をダミー情報算出部25が算出し、情報統合部26が配線オブジェクトの情報と統合する。評価部27は、統合したダミー挿入後の回路レイアウトが設計基準を満たすかを評価する。

(もっと読む)

半導体集積回路の設計方法

【課題】設計期間の短縮が可能な半導体集積回路の設計方法を提供する。

【解決手段】本実施形態によれば、半導体集積回路の設計方法は、第1配線層、前記第1配線層上に設けられる第2配線層、及び前記第2配線層上に設けられる第3配線層を有する半導体集積回路の設計方法である。この方法は、前記第2配線層に、第1方向に沿って複数のスペア配線を配置し、前記第3配線層に、前記第1方向に直交する第2方向に沿って複数のスペア配線を配置する工程を備える。さらに、この方法は、前記スペア配線の配置後に、前記第1配線層に素子を配置する工程と、前記素子の配置後に、前記第1乃至第3配線層の少なくともいずれか1つに信号配線を配置する工程と、前記スペア配線を用いて、配線の設計変更を行う工程と、を備える。

(もっと読む)

半導体集積回路装置

【課題】設計工数をほとんど掛けないで、CMP対策及び短時間光アニール対策の両対策に最適化されたダミーパターンを有する半導体集積回路装置を提供すること。

【解決手段】基板上に、メモリマクロ領域10及び機能回路領域20を有する半導体集積回路装置1において、機能回路領域20間、及び、メモリマクロ領域10と機能回路領域20との間に配置されるとともにダミーパターン41を含むダミーパターン領域40を備え、ダミーパターン41は、前記メモリセルアレイ領域におけるメモリセルパターン11の拡散層12、13及びゲート電極14と同等のパターンであり、ダミーパターン領域40におけるダミー拡散層42、43及びダミーゲート電極44の面積率は、メモリセルアレイ領域における拡散層12、13及びゲート電極14の面積率と同等以上である。

(もっと読む)

半導体集積回路及びその製造方法

【課題】金属層からなるガードリングで囲まれたトリミング素子形成領域のヒューズ上の保護膜の開口からヒューズ上の層間絶縁膜に浸入した水分等がガードリングに形成されたヒューズ引き出し電極用の開口を通ってデバイス形成領域に浸入することを防止する。

【解決手段】ヒューズ5aを取り囲む第1ガードリング30とその外側の第2ガードリング40に囲まれたヒューズ電極引き出し領域41を形成する。ヒューズ5aと連続し層間絶縁膜6とフィールド酸化膜4の間をヒューズ電極引き出し領域41まで延在するヒューズ電極5と、該ヒューズ電極5と接続する第1ヒューズ引き出し電極7cと、該第1ヒューズ引き出し電極7cと接続する第2ヒューズ引き出し電極9cとを形成し、該第2ヒューズ引き出し電極9cを層間絶縁膜8上に形成された第2ガードリング40を構成する第2電極の開口24を通してデバイス素子形成領域80に引き出す。

(もっと読む)

半導体装置及びそのレイアウト作成方法

【課題】半導体装置及びその製造方法において、ゲート電極部の幅及びゲート電極部からの突き出し長のばらつきを低減する。

【解決手段】半導体装置は、ゲート電極部及び突き出し部を有する実パターン431と、実パターン431に並んで配置されるダミーパターン433とを含む複数のラインパターンを備える。2つのダミーパターン433と、これらに挟まれ且つ実パターン432を含むラインパターンとにより、同一間隔を空けて並走するラインパターン並走部が構成される。ラインパターン並走部の各ラインパターンは、同一の幅を有すると共に、互いに実質的に面一なライン終端部414を有する。各ライン終端部414の延長線上に、同一の終端部間距離403を空けて、ライン終端部均一化ダミーパターン420が形成される。ライン終端部均一化ダミーパターン420は、ラインパターンと同一幅で且つ同一間隔に形成された複数のライン状のパターンを含む。

(もっと読む)

1 - 20 / 175

[ Back to top ]