Fターム[5F064EE52]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 特定用途向け配線 (1,859) | 電源、接地配線 (1,005)

Fターム[5F064EE52]に分類される特許

1 - 20 / 1,005

スタンダードセル、および、半導体集積回路

半導体装置

半導体集積回路

【課題】回路規模を低減しつつ任意の論理を実現可能な半導体集積回路を提供する。

【解決手段】実施形態の半導体集積回路は、第1論理ブロックを少なくとも1つ含む第1回路群と、第1論理ブロックよりも多い数の第2論理ブロックを含む第2回路群と、入力データを第1論理ブロックまたは第2論理ブロックへ入力する機能、および、第1論理ブロックまたは第2論理ブロックから出力される出力データを外部へ出力する機能を有する入出力部とを含む。第1回路群は、第1スイッチブロックと、第1電源制御回路とを有する。第1電源制御回路は、第1回路群に含まれる第1論理ブロックおよび第1スイッチブロックに対する電力の供給および停止を共通に制御する。第2回路群は、第2スイッチブロックと第2電源制御回路とを有する。第2電源制御回路は、第2回路群に含まれる論理ブロックおよび第2スイッチブロックに対する電力の供給および停止を共通に制御する。

(もっと読む)

半導体集積回路の製造方法

【課題】常時動作領域と電源遮断可能領域とが混在する半導体集積回路を提供する。

【解決手段】半導体基板に設けられ、複数の基本セル(10)の配置が可能なセル配置領域と、空間的に前記セル配置領域と重なって設けられた基本電源配線(11)と、前記基本電源配線(11)から前記セル配置領域への電源供給を停止するスイッチセル(6)と、前記スイッチセル(6)に隣接して前記セル配置領域に配置され、前記スイッチセル(6)が前記セル配置領域への電源供給を停止した場合においても、前記スイッチセル(6)から電源供給を受ける常時動作セル(5)とを具備する。

(もっと読む)

ノイズ解析モデル及びノイズ解析方法

【課題】解析対象回路内に設けられた素子のそれぞれに対する基板ノイズの影響を解析することができるノイズ解析モデル及びノイズ解析方法を提供すること。

【解決手段】本発明の一態様にかかるノイズ解析モデル100は、抵抗RS1〜RS4、抵抗RGB1〜RGB4及び接地抵抗RGNDを有する。抵抗RS1〜RS4は、ノイズ発生源から半導体基板を介して基板ノイズが伝搬する接続点1と、バックゲート直下の半導体基板中の点BG1〜BG4の間にそれぞれ接続される。抵抗RGB1〜RGB4は、バックゲート直下の半導体基板中の点BG1〜BG4とガードバンド4との間に接続される。接地抵抗RGNDは、ガードバンド4と接地電位との間に接続される。

(もっと読む)

半導体集積回路のレイアウト設計方法

【課題】SETUP時間とHOLD時間のどちらも満足させるタイミングの調整が可能な技術を提供する。

【解決手段】半導体集積回路の配置配線レイアウトを決定した後に、所定の信号線を伝搬するデータのタイミング情報に基づいて、タイミング違反を有する違反データの遅延情報を抽出する。その抽出された遅延情報に基づいて、タイミング違反を解消するための追加すべき容量値を算出する。また、違反データを伝搬する配線のレイアウト配置情報に基づいて、違反データを伝搬する配線の近傍の電源容量セルを検出する。また、算出された容量値に基づいて、検出された電源容量セルを、電源容量セルとレイアウト外形・電源/GND配線配置位置が同じ調整容量セルに置き換える。そして、置き換えた調整用容量セルのゲートと違反データを伝搬する配線とを接続して再配線を実行する。

(もっと読む)

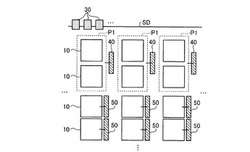

半導体集積回路、半導体集積回路の設計方法及び設計装置並びにプログラム

【課題】セルベースの半導体集積回路において、異なるセル高さを有するセルを効率良く配置するための技術を提供する。

【解決手段】半導体集積回路が、基準ハイトセル30、マルチハイトセル40、VDD電源配線、VSS電源配線を備え、マルチハイトセルは、Y軸方向に延伸するVDD側電源供給配線5B、VSS側電源供給配線6Bを備え、基準ハイトセルの高さをa、マルチハイトセルの高さをb、VDD、VSS電源配線の幅をwとしたときに、VSS側電源供給配線は、少なくとも、マルチハイトセルの下端からw/2高さ方向に離れた位置とマルチハイトセルの下端からb−a−w/2高さ方向に離れた位置の間の高さ範囲をカバーするように設けられ、VDD側電源供給配線は、少なくとも、マルチハイトセルの下端からa+w/2高さ方向に離れた位置とマルチハイトセルの下端からb−w/2高さ方向に離れた位置の間の高さ範囲をカバーするように設けられる。

(もっと読む)

省面積及び省電力のスタンダードセル方法

【課題】省面積及び省電力のための半導体集積回路の設計方法を提供する。

【解決手段】主回路217と適応電圧用調整回路を含む半導体集積回路であって、適応電圧調整用回路は、クロック信号を受け取るように構成された整合回路211と、整合回路211の出力を受け取り、また、クロック信号を受け取るように構成された位相検出器213と、電源電圧を増加又は減少させるように構成された電圧レギュレータ215とを含み、主回路217は電圧レギュレータ215から電源電圧を受け取るように構成され、整合回路211は電源電圧を受け取って、電源電圧における増加又は減少に基づいて、信号伝搬における遅延を調整するように構成される。

(もっと読む)

半導体装置の設計方法、半導体装置の設計プログラム、半導体装置の設計装置

【課題】IRドロップの制約を満たしつつチップレイアウトを小型化できる半導体装置の設計方法、半導体装置の設計プログラム、半導体装置の設計装置を提供すること。

【解決手段】本発明の一態様である半導体装置の設計方法は、複数の電源用パッド及び信号用パッドを、半導体チップ上のチップコアの周囲に配置する。そして、複数の電源用パッド及び信号用パッドの数から決まるチップサイズSpと、チップコアの大きさから決まるチップサイズScと、を比較する。その後、Sp≧Scであれば、IRドロップが制約値を満たす限り、配置した複数の電源用パッドのうちの1又は2以上の電源用パッドを削除する。

(もっと読む)

半導体集積回路装置

【課題】半導体集積回路装置において、I/Oセルの高さを低減すると同時に幅の増大を防ぐことでI/Oセルの占める領域の面積を削減すること。

【解決手段】レベルシフタ回路、I/Oロジック回路およびI/Oバッファ回路を含むI/Oセルがコア領域の周囲に配置された半導体集積回路装置であって、I/Oロジック回路が配置されたI/Oロジック領域、および、I/Oバッファ回路が配置されたI/Oバッファ領域は、I/Oセルに対するパッドが配置された領域と重なり合うとともに、コア領域の辺に平行な方向に互いに並んで配置されている。

(もっと読む)

半導体装置

【課題】配線間の影響を抑制することができる多層配線を有する半導体装置を実現する。

【解決手段】本発明の実施形態における半導体装置は、下層の配線層に第1の方向に沿って形成された信号配線11と、下層の配線層と絶縁膜を介して配置される上層の配線層に第1の方向と交差する第2の方向に沿って形成された基準電位配線13と、 上層の配線層に基準電位配線13に沿って近接して形成されたシールド線14a、14bと、を有し、信号配線11と基準電位配線13の交差部15cにおいて基準電位配線13とシールド線14a、14bとの距離が他の部分に比べてより狭くなっていることを特徴とする。

(もっと読む)

回路設計装置、デカップリング容量効果最適化方法、及びプログラム

【課題】 本発明の課題は、デカップリング容量効果を最適化した回路設計を行うことを目的とする。

【解決手段】 上記課題は、回路を構成する複数のセル間のネット毎の高電位電源側及び低電位電源側の配線容量と、各入力ピンの該高電位電源側及び該低電位電源側の容量とを記憶する記憶部と、前記記憶部に記憶された前記各ネットの配線容量と、前記各入力ピンの容量とを参照して、前記構成における非動作パスに対して、セルの置換前の該セルの組み合せと、セルを置換する際の制約に従った置換後のセルの組み合せのうち、該非動作パスの信号値の遷移状態に応じた、各ネット及び各入力ピンの前記高電位電源側又は前記低電位電源側の容量を加算した総容量に基づいて、該総容量が最大となるセルに置換することによって、デカップリング容量効果を最適化する最適化処理部と、を有する回路設計装置により達成される。

(もっと読む)

半導体集積回路

【課題】設計する回路の中で電流の多く流れる信号線を容易に見つけ出すことができ、容

易にその部分の電流を測定できるスタンダードセルを提供することを課題とする。

【解決手段】電流検出用テストパッドを少なくとも2つ有するスタンダードセルを自動レ

イアウトで配置する。そして、2つのテストパッド間を接続する配線を切断することで、

該2つのテストパッドを電流測定用テストパッドとして利用する。なお、スタンダードセ

ル内の2つのテストパッド間は、過電流が流れることにより電流の流れる経路が遮断され

る配線によって接続される構成としてもよい。また、2つのテストパッド間をつなぐ配線

部にメモリ又はアナログスイッチを設ける構成としてもよい。

(もっと読む)

集積回路

【課題】電力消費量の増大を抑制しつつ、タイミング信号のスキューを低減する。

【解決手段】主クロック分配回路は、タイミング信号を複数の主タイミング信号に分岐して分配する。副クロック分配回路は、タイミング信号の分配が指示された場合にはタイミング信号を複数の副タイミング信号に分岐して分配する。最小遅延タイミング信号出力部は、複数の主タイミング信号のいずれかと複数の副タイミング信号のいずれかとのうち先に分配された信号を最小遅延タイミング信号として出力する。同期動作回路は、最小遅延タイミング信号に同期して動作する。測定部は、複数の主タイミング信号のいずれかの遅延のばらつきを示す値を測定する。クロック分配回路制御部は、測定された値の示す前記ばらつきが前記所定値以上であるときに副分配回路に前記タイミング信号の分配を指示する。

(もっと読む)

半導体集積回路、半導体集積回路の設計方法、および半導体集積回路の設計装置

【課題】配線層に形成される信号配線をなるべく迂回させずに配線できるように電源スタックビアが配置された半導体集積回路を提供すること。

【解決手段】半導体集積回路は、第1の方向に延伸された第1,第2の下層電源配線11A,11Bと、第2の方向に延伸された第1,第2の上層電源配線12A,12Bと、上層,下層電源配線を接続させる第1,第2接続部3A,3Bと、を備え、第1,第2接続部は、第1,第2の接続用配線26A,26Bと、第1,第2の位置変換用配線27A,27Bと、第1,第2の上側ビア28A,28Bと、を有して構成され、第1,第2の接続用配線は、第2の方向に沿った同一ライン上に配置され、第1,第2の位置変換用配線は、第1,第2の接続用配線を第2の方向に沿って延長した領域内に形成され、第1,第2の上側ビアは、第1の方向に沿った同一ライン上となる位置に配置される。

(もっと読む)

半導体装置

【課題】少しの設計方法の変更で設計できる、一層低消費電力化した半導体装置の実現。

【解決手段】複数の電源供給領域23と、複数の電源供給領域に供給する電源の電圧を切り替える複数の電源切替ユニットSWA,SWBと、を有し、複数の電源供給領域に含まれる回路要素を組み合わせて少なくとも1つの機能ブロックが形成され、少なくとも1つの機能ブロックは、内部に異なる電圧で動作する回路要素を含む半導体装置。

(もっと読む)

鍵格納回路、半導体集積回路、及びシステム

【課題】格納された鍵の値の推測を困難にすることができる、鍵格納回路、半導体集積回路、及びシステムを提供する。

【解決手段】LSI10に搭載された鍵格納ブロック20は、k個のヒューズメモリセル30を有するヒューズブロック22と、鍵生成回路24と、を備えており、ヒューズブロック22からは予め実装されているビット長kの固定出力値fout[k−1:0]が出力される。鍵生成回路24は、レジスタ及び復号器を含んで構成されており、復号器は、演算処理により、固定出力値fout[k−1:0]と、レジスタの出力値と、からビット長n(n>k)の鍵key[n−1:0]を生成して出力する。

(もっと読む)

半導体集積回路システムおよび半導体集積回路システムの配置配線方法

【課題】EMI低減に有効な半導体集積回路システムを提供する。

【解決手段】バスライン8上に配置された中央演算処理装置1と、演算論理装置6と、デカップリングキャパシタ形成領域100・合成論理形成領域200・インピーダンス形成領域300を有する半導体集積回路400と、論理ライブラリ情報格納部22・デカップリングキャパシタ配置配線情報格納部24・インピーダンス配置配線情報格納部26・電源配線配置配線情報格納部28を有する記憶装置2とを備え、論理ライブラリ情報格納部22・デカップリングキャパシタ配置配線情報格納部24・インピーダンス配置配線情報格納部26のそれぞれの格納データに基づいて、それぞれ合成論理形成領域200・デカップリングキャパシタ形成領域100・インピーダンス形成領域300における配置配線を実行する半導体集積回路システム10。

(もっと読む)

配置配線装置

【課題】効率的にIR−Dropを防止することが可能な配置配線装置を提供すること。

【解決手段】複数のセルを配置した後、セル間の隙間が所定の大きさよりも小さい場合にはセル間の隙間が所定の大きさ以上となるようにセルの配置を変更する(S17)。そして、配置された複数のセルの間に容量セルを挿入し(S15)、配置された複数のセルの配線を行なう(S14,S16)。したがって、効率的にIR−Dropを防止することが可能となる。

(もっと読む)

フィールドプログラマブルゲートアレイの性能を向上させるための装置および関連方法

【課題】性能が向上されたフィールドプログラマブルゲートアレイ(FPGA)を提供する。

【解決手段】フィールドプログラマブルゲートアレイ(FPGA)103であって、該FPGAは、該FPGA内の少なくとも1つの回路に対するプロセス、電圧、および温度の表示を提供するように適合された監視回路のセット115と、該少なくとも1つの回路に対するプロセス、電圧、および温度の該表示から該少なくとも1つの回路に対するボディバイアス値の範囲を導出するように適合されたコントローラ140と、該少なくとも1つの回路内の少なくとも1つのトランジスターにボディバイアス信号を提供するように適合されたボディバイアス生成器とを含み、該ボディバイアス信号は、該ボディバイアス値の範囲内の値を有する。

(もっと読む)

1 - 20 / 1,005

[ Back to top ]