Fターム[5F064EE53]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 特定用途向け配線 (1,859) | ボンディングパッド用配線 (231)

Fターム[5F064EE53]に分類される特許

1 - 20 / 231

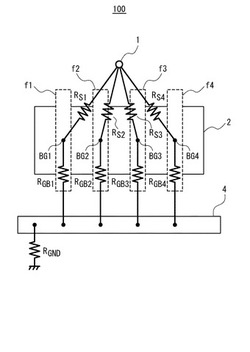

ノイズ解析モデル及びノイズ解析方法

【課題】解析対象回路内に設けられた素子のそれぞれに対する基板ノイズの影響を解析することができるノイズ解析モデル及びノイズ解析方法を提供すること。

【解決手段】本発明の一態様にかかるノイズ解析モデル100は、抵抗RS1〜RS4、抵抗RGB1〜RGB4及び接地抵抗RGNDを有する。抵抗RS1〜RS4は、ノイズ発生源から半導体基板を介して基板ノイズが伝搬する接続点1と、バックゲート直下の半導体基板中の点BG1〜BG4の間にそれぞれ接続される。抵抗RGB1〜RGB4は、バックゲート直下の半導体基板中の点BG1〜BG4とガードバンド4との間に接続される。接地抵抗RGNDは、ガードバンド4と接地電位との間に接続される。

(もっと読む)

半導体装置および半導体パッケージ

【課題】パッドが設けられた面の向きを変えても、パッドを基板に接続するボンディングワイヤが交差しない半導体装置を提供する。

【解決手段】複数のパッドを含む第1のパッド群と、第1のパッド群に平行に一列に配置された複数のパッドを含む第2のパッド群と、第1のパッド群を基準にして第2のパッド群とは反対側に設けられた複数のバッファ回路を含む第1のバッファ回路群と、第2のパッド群を基準にして第1のパッド群とは反対側に設けられた複数のバッファ回路を含む第2のバッファ回路群と、第1のパッド群の複数のパッドのそれぞれを第2のバッファ回路群の複数のバッファ回路のそれぞれに対応して接続する複数の第1の配線と、第2のパッド群の複数のパッドのそれぞれを第1のバッファ回路群の複数のバッファ回路のそれぞれに対応して接続する複数の第2の配線と、を有する。

(もっと読む)

半導体装置、半導体ウェハ及び半導体装置の製造方法

【課題】ダイシングの際にクラック発生を抑制できる半導体装置を提供する。

【解決手段】半導体基板の上に形成された複数の配線層と、前記複数の配線層の間に配置されたビア層と、前記複数の配線層に形成された導電膜と、前記ビア層の上下の前記配線層の前記導電膜と接続するビアプラグV5とを有し、スクライブ領域31は、チップ領域の外周であって前記半導体基板の縁に接して位置し、前記スクライブ領域31は前記縁に接するパッド領域33を有し、前記パッド領域33は、前記複数の配線層の各々に、平面視において相互に重なって配置され、前記複数の配線層は、第1の配線層と第2の配線層を有し、前記第1の配線層の前記導電膜は、前記パッド領域33の全面に形成された第1の導電パターン55を有し、前記第2の配線層の前記導電膜は、前記パッド領域の一部に形成された第2の導電パターン50を有する。

(もっと読む)

基板導通を利用した積重ねダイ式の構成をもつ集積回路

【課題】積重ねダイ式の集積回路で使用するのに適した基板導通技術を提供すること。

【解決手段】集積回路が、積み重ねて配置された複数の集積回路のダイを備え、積重ねの頂部のダイを除く任意のダイが、それ自身および追加のダイ少なくとも1つのための電流を基板導通により担持する。1つの形態では、積重ねの底部のダイを除く各ダイが、下側のダイのバスまたはその他の電源導体を介して基板導通によりその電源電流を担持する。

(もっと読む)

半導体集積装置

【課題】共通放電経路との間の異種電源間ESD保護回路をそれぞれの電源のパッドの近くに配置することのできる半導体集積装置を提供する。

【解決手段】実施形態の半導体集積装置1は、パッドPと、自己電源用ESD保護回路ESD1とを有し、VDDc系統の電源供給に使用の電源用I/OセルIOC1と、パッドPと、自己電源用ESD保護回路ESD1と、異種電源間ESD保護回路ESD2とを有し、VDDa、VDDb系統の電源供給に使用の電源用I/OセルIOC2とを備える。信号入出力用I/OセルIOC100と同一外形寸法の電源用I/OセルIOC1およびIOC2が、列状に配置されたIOC100と同列に配置され、電源用I/OセルIOC2の異種電源間ESD保護回路ESD2へ接続される共通放電経路CDLが、電源用I/OセルIOC1から、列状に配置されたIOC100を貫通して、電源用I/OセルIOC2へ配線される。

(もっと読む)

半導体装置及びそのレイアウト方法

【課題】再配線層形成工程、メタルポスト形成工程及び樹脂封止工程を経てウェハレベルで樹脂封止される半導体装置について、パッケージング工程で発生する応力を利用してPMOSFETの電流駆動能力を制御する。

【解決手段】メタルポスト21の形成に起因して半導体基板に圧縮応力が生じる範囲内にPMOSFET31が配置されている。PMOSFET31はそのチャネル方向がメタルポスト23の配置範囲の重心O及びPMOSFET31のチャネル領域の配置範囲の重心Gを通る直線と直交する向きに配置されている。重心Gで、メタルポスト21の形成に起因して半導体基板に生じる圧縮応力は、重心Gの位置で、重心Gと中心Oを通る直線に直交する方向に印加される。重心Gでの圧縮応力の方向とPMOSFET31のチャネル方向は一致するので、PMOSFET31の電流駆動能力は、当該圧縮応力が印加されない場合に比べて向上する。

(もっと読む)

半導体装置

【課題】隣接する2つのトランジスタ同士が接続された構成を有し、省スペースと電流集中による信頼性の低下の抑制とを両立させた半導体装置を実現できるようにする。

【解決手段】半導体装置は、第1のトランジスタ101と接続された第1のバス111、第2のトランジスタ102と接続された第2のバス112と、第1のバス111と第2のバス112との間に形成され、第1のバス111と第2のバス112とを接続するバス間配線121とを備えている。バス間配線121は、第1のバス111における第2のバス112と対向する辺の一部及び第2のバス112における第1のバス111と対向する辺の一部と接続されている。第1のコンタクトパッド131は、第1のバス111の一部と接続され、第2のコンタクトパッド132は、第2のバス112の一部と接続されている。

(もっと読む)

半導体集積回路

【課題】内側のセル列と外側のセル列とでセルの形状が同じ場合において、内側のセル列におけるセルの配列ピッチを外側のセル列におけるセルの配列ピッチより大きくしなくても外側のセル列のセルに接続される配線のための領域を確保することができる。

【解決手段】半導体集積回路は、半導体チップの外周11に沿って配置される複数の第1セル40と、複数の第1セル40の内側で外周11に沿って配置される複数の第2セル40とを具備する。複数の第1セル40及び複数の第2セル40は同一の長方形形状に形成される。複数の第1セル40のそれぞれの長辺4aは外周11に平行である。複数の第2セル40のそれぞれの長辺4aは外周11に垂直である。

(もっと読む)

貫通電極を有する積層構造の半導体装置、半導体メモリ装置、半導体メモリ・システム及びその動作方法

【課題】貫通電極を有する積層構造の半導体装置、半導体メモリ装置、半導体メモリ・システム及びその動作方法を提供する。

【解決手段】複数の半導体レイヤ間で伝送される情報の衝突を防止する構造を有する半導体装置であり、該半導体装置は、第1温度情報を出力する第1温度センサ回路を含む少なくとも1つの第1半導体チップと、貫通電極に電気的に連結されずに、第1温度センサ回路に電気的に連結される第1バンプと、第1半導体チップの貫通電極に電気的に連結される第2バンプと、を具備する半導体装置であることを特徴とする。

(もっと読む)

半導体装置

【課題】半導体装置の特性を向上させる。

【解決手段】本発明の半導体装置は、半導体基板の上方に形成された半導体素子と、半導体素子の上方に形成された第1絶縁膜と、第1絶縁膜上に形成されたアルミニウム(Al)を含有する第1導電性膜よりなるヒューズ素子Fと、を有する。さらに、第1絶縁膜上に形成され、第1導電性膜よりなる第1配線と、第1配線上に形成された第2絶縁膜と、を有し、ヒューズ素子Fのプログラム領域は、第2絶縁膜に設けられた開口部OA1から露出している。また、ヒューズ素子Fのプログラム期間およびヒューズ素子にプログラムされたデータの読み出し期間以外の期間において、ヒューズ素子Fの両端を接地電位に維持する。例えば、ヒューズ素子Fの一端は、接地電位に接続され、他端は、スイッチング素子を介して接地電位に接続されている。

(もっと読む)

半導体装置

【課題】積層チップシステムにおいて、各チップのIO回路の大きさを、そのドライブ能力やESD耐性能力を維持した上で、従来のサイズから縮小し、積層システムでは積層数に応じてIO数を変化させることができる半導体装置を提供する。

【解決手段】積層チップシステムにおいて、各チップは、各IO用の貫通ビア接続用パッド201に接続するIO回路202、スイッチ回路206にてIOチャネル207を構成し、このIOチャネル207を最大積層予定数のIOチャネル分まとめて接続してIOグループを構成し、このIOグループを1個以上持つ。各IO用の貫通ビア接続用パッド201は、貫通ビアにて別層のチップの同一位置のIO端子と接続される。インターポーザにおいては、実際の積層数が最大積層予定数に満たない場合はインターポーザ上で隣接するIOグループ内のIO用の接続用パッドが導体で接続されている。

(もっと読む)

フリップチップ半導体ダイのパッドレイアウトを形成する半導体素子および方法

【課題】半導体素子を作製する方法を提供する。

【解決手段】主に半導体ダイの周辺領域中に位置する信号パッドと、主に前記信号パッドから半導体ダイの内部領域中に位置する電力パッドおよび接地パッドとを伴う、ダイパッドレイアウトを有する半導体ダイを提供するステップと、前記信号パッド、電力パッド、および接地パッド上に複数のバンプを形成するステップと、基板を提供するステップと、前記基板上に相互接続部位を伴う複数の伝導性トレースを形成するステップであって、前記バンプは、相互接続部位よりも幅広い、ステップと、前記バンプが前記相互接続部位の頂面および側面を覆うように、前記バンプを前記相互接続部位に接着するステップと、前記半導体ダイと基板との間で前記バンプの周囲に封入材を堆積させるステップとを含む、半導体素子を作製する方法。

(もっと読む)

半導体装置、液晶ディスプレイパネル及び携帯情報端末

【課題】外部駆動端子の狭ピッチ化に充分答えることができる半導体装置を提供する。

【解決手段】長方形の半導体基板の一方の長辺に沿ってそれぞれ配置された、複数の外部駆動端子(3A,3B,3C)、対応する前記外部駆動端子に接続されたESD保護回路(4A,4B,4C)、及び対応する外部駆動端子に接続された出力回路(5)を備え、複数個の外部駆動端子は、Y方向に沿って複数列であるn列で配置され、各列の間で外部駆動端子の位置が相互にずらされた千鳥状配置を有し、前記出力回路は、Y方向に交差するX方向にn個の外部駆動端子毎に対応して一列に配置されるn個の出力ユニット(5A,5B,5C)を有する。n列の千鳥状配置によって外部駆動端子を狭ピッチにできる。n個の外部駆動端子毎に対応される出力回路にはX方向に一列で配置されたn個の出力ユニットを配置することにより、n個分の出力ユニットの幅を1個分の幅に集約できる。

(もっと読む)

半導体装置

【課題】並列駆動構成のI/Oバッファから出力される信号を安定化し、信頼性を向上する。

【解決手段】I/Oセル2は、1つの出力信号を正転信号と反転信号からなる相補信号として出力する相補型I/Oセルからなり、2つのI/Oセル2が並列接続された構成からなる。2つのI/Oセル2の出力部となるインバータ6の出力部は、配線17によってそれぞれ接続されており、2つのI/Oセル2の出力部となるインバータ7の出力部は、配線18によってそれぞれ接続されている。配線17は、I/Oセル2の下辺側に2つのI/Oセル2を横断するように形成され。配線18は、該配線17の上方に形成されており、2つのI/Oセル2を横断するように形成されている。また、配線17の配線長と配線18の配線長は、略同等となるようにレイアウトされている。

(もっと読む)

半導体装置、半導体集合部材及び半導体装置の製造方法

【課題】様々なオン抵抗の素子を容易に製造することができる半導体装置、半導体集合部材及び半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、素子部と、第1の電極部と、第2の電極部と、延出部と、を備える。素子部は、基板に設けられる。第1の電極部は、素子部の上に設けられ、素子部と導通する。第2の電極部は、素子部の上において第1の電極部と離間して設けられ、素子部と導通する。延出部は、素子部の上に設けられ、第1の電極部及び第2の電極部の周縁部から基板の周縁部に向けて延出して設けられる。

(もっと読む)

レイアウト設計装置、レイアウト設計方法、及びプログラム

【課題】シミュレーションを実行することなく、最適な配線幅の取得を行えるようにすることにより、シミュレーションの複数回実行による処理時間増大を防ぐ。

【解決手段】レイアウト設計装置は、フリップチップ構造の半導体集積回路のRDL(パッド−I/O端子間)配線処理において、I/Oセルの所要電流量と配線長に適した配線幅を取得するためのテーブルをライブラリ化して保持する手段と、パッドとI/Oセルの位置関係から配線に必要な距離を算出する手段と、パッドとI/Oセル端子間の配線に必要な距離とI/Oセルの所要電流量と前記テーブルから適切な配線幅を取得する手段とを有することを特徴とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】入出力端子と半導体スイッチとの間を接続する配線同士が交差する箇所が発生しても、端子間のアイソレーション特性を向上させつつ、サイズ及びコストを抑制可能な半導体装置を提供する。

【解決手段】半導体スイッチ回路(20)は、複数の入力端子(31,32)のうち任意の入力端子を配線層(51)又は再配線層(251)を介して複数の出力端子(41〜44)のうち任意の出力端子と接続させるように構成される。複数の入力端子及び複数の出力端子のうち、ある端子と半導体スイッチ回路との間を接続する配線と、他の端子と半導体スイッチ回路との間を接続する配線とが交差している箇所において、交差する配線のうち、一方の配線を配線層とし、他方の配線を再配線層とする。

(もっと読む)

銅技術相互接続構造を使用する集積回路デバイス用のアルミニウム・パッド電力バスおよび信号ルーティング技術

【課題】電力バス相互接続構造の工程数を低減して製造できる半導体装置の製造方法を提供する。

【解決手段】第1のパッシベーション・スタック149を、導電性ランナ132、134および誘電体層162の上に形成する。開口を、通常のリソグラフィ技術および誘電エッチング技術によって、第1のパッシベーション・スタックを貫通して画定し形成する。露出された表面上に導電性バリア層166を形成する。アルミニウム層をブランケット堆積して、開口を充填する。パターニング、エッチング工程によって、開口内に、アルミニウム・パッド170を形成する。開口内に、ランナ134と導電性接触する導電性バイア172を形成する。アルミニウム・パッドを形成するために用いられるのと同じパターニング、エッチング工程において、アルミニウム層内に電力バス174も形成する。

(もっと読む)

半導体装置、および、配線設計方法

【課題】チップサイズを縮小し、再配線層の配線を容易にすることが可能な半導体装置を提供する。

【解決手段】略矩形のLSI基板1の上面に、パッド電極4a1、4a2、4c1を被覆する絶縁膜3a、3bが設けられ、前記絶縁膜3b上に、前記パッド電極4a1、4a2、4c1の何れかに接続された第1のコンタクト配線7a1、7a2、7c、および前記第1のコンタクト配線7a1、7a2に接続された再配線8b1、8b2が設けられ、第1の再配線エリア3上に設けられたボール電極2b、2cと、第1のパッド電極4c1が上面の端部に設けられたLSIコア1a3と、前記第1のパッド電極4c1に接続された第2のコンタクト配線9b1に接続された配線層6b1と前記パッド電極4a1、4a2のうちの第2のパッド電極4a1とに接続された第3のコンタクト電極9b2が形成され、前記LSIコア1a3に隣接した第2の再配線エリア1a2、とを有する。

(もっと読む)

半導体装置

【課題】電源配線と接地配線とを有する半導体装置において、配線の一部における電圧ドロップや、電圧ドロップに伴うマイグレーションの発生を抑制することが可能な半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、主表面に沿うように層状に広がる電源シート状配線PPWRと、主表面に沿うように、主表面に交差する方向に関して電源シート状配線と一定の距離を隔てて層状に広がる接地シート状配線PGNDと、上記主表面上に形成され、主表面内の一の方向に延在する電源配線PWRと、主表面上に形成され、一の方向に沿う方向に延在し、電源配線PPWRと一定の距離を隔てて形成された接地配線GNDとを備える。上記電源シート状配線PPWRは、電源配線PWRと電気的に接続されており、接地シート状配線PGNDは、接地配線GNDと電気的に接続されている。

(もっと読む)

1 - 20 / 231

[ Back to top ]