Fターム[5F083LA10]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | 周辺回路(制御回路) (893)

Fターム[5F083LA10]に分類される特許

1 - 20 / 893

記憶装置

半導体集積回路

半導体装置

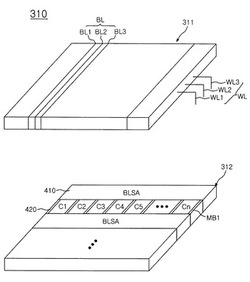

【課題】複数個のメモリチップが積層された構造を有する半導体装置の信頼性を向上させる。

【解決手段】半導体装置は、複数のビットラインと複数のワードラインとの交差点に複数個のメモリセルが配列される複数個のメモリチップが垂直方向に積層され、いずれか一つのメモリチップには複数個のメモリチップの各々に配列された複数のビットラインと連結されアクティブにされるメモリチップのビットラインをイネーブルさせるためのビットラインセンスアンプと、複数個のメモリチップの各々に配列された複数のワードラインと連結されアクティブされるメモリチップのワードラインをイネーブルさせるためのサブワードラインドライバを含み、ビットラインセンスアンプとサブワードラインドライバがいずれか一つのメモリチップに備わる。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板上の複数の半導体層のうちの1つを正確に選択する。

【解決手段】実施形態に係わる半導体装置は、第1乃至第3の半導体層12−1〜12−3と、第1乃至第3の半導体層12−1〜12−3のうちの1つを選択するレイヤー選択トランジスタ15(LST)とを備える。第1のノーマリーオン領域17−1は、第1の半導体層12−1内において第1乃至第3のゲート電極16−1〜16−3に隣接するチャネルをノーマリーオンチャネルにし、第2のノーマリーオン領域17−2は、第2の半導体層12−2内において第2乃至第4のゲート電極16−2〜16−4に隣接するチャネルをノーマリーオンチャネルにし、第3のノーマリーオン領域17−3は、第3の半導体層12−3内において第3乃至第5のゲート電極16−3〜16−5に隣接するチャネルをノーマリーオンチャネルにする。

(もっと読む)

相変化メモリ・セルをプログラミングするための方法、コンピュータ・プログラム、および装置、ならびに相変化メモリ・デバイス(相変化メモリ・セルのプログラミング)

【課題】s>2通りのプログラム可能セル状態を有する相変化メモリ・セルをプログラミングするための方法および装置を提供する。

【解決手段】少なくとも1つの制御信号VBLを印加して、セルをプログラミングするためのプログラミング・パルスを発生する。プログラミング・パルス中に少なくとも1つの前記制御信号VBLを変更して、プログラミングすべきセル状態に依存してプログラミング・パルスを整形し、前記セル状態をプログラミングするためのそれぞれのプログラミング軌道に対応する複数のプログラミング・パルス波形(波形A〜D)のうちの選択された1つを発生する。選択されたプログラミング・パルス波形は、プログラミングすべきセル状態を含むプログラミング軌道に対応する。

(もっと読む)

半導体集積回路及びその設計方法

【課題】チップサイズを増大することなく、キャパシタの容量を増やすことができる半導体集積回路を提供する。

【解決手段】半導体基板10上にメインブロック11と周辺ブロック12とが混載された半導体集積回路において、半導体基板10上のメインブロック11に形成され、第1のトレンチキャパシタを有するメイン回路と、半導体基板10上の周辺ブロック12に形成され、第2のトレンチキャパシタを有するアナログ回路とを備える。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】容量素子の容量を低減し、また、集積度の高い半導体メモリ装置を提供する。

【解決手段】1つのビット線BL_mに複数個のメモリブロックを接続させる。メモリブロックMB_n_mはサブビット線SBL_n_mと書き込みスイッチと複数のメモリセルを有する。サブビット線SBL_n_mと隣接するサブビット線SBL_n+1_mは2つのインバータと2つの選択スイッチよりなる増幅回路AMP_n/n+1_mに接続し、増幅回路は選択スイッチによりその回路構成を変更できる。また、増幅回路は読み出しスイッチを介してビット線BL_mに接続する。サブビット線SBL_n_mの容量は十分に小さいため、各メモリセルの容量素子の電荷による電位変動を増幅回路AMP_n/n+1_mでエラーなく増幅でき、ビット線BL_mに出力できる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】制御性の高い不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、第1のメモリセルアレイ層と、第1のメモリセルアレイ層の上に形成された第1の絶縁層と、第1の絶縁層の上に形成された第2のメモリセルアレイ層と、第1の絶縁層を介して上下に位置する第1及び第2の浮遊ゲートの第1の方向の両側面にゲート間絶縁層を介して形成され、第1の方向と直交する第2の方向に延びる制御ゲートと、第1の絶縁層を介して上下に位置する第1及び第2の選択ゲートの第1の方向の両側面にゲート間絶縁層を介して形成され、第2の方向に延び、第1及び第2の半導体層並びに第1及び第2のゲート絶縁層と共に補助トランジスタを形成する補助ゲートとを備える。

(もっと読む)

半導体装置

【課題】メモリセルの動作を従来よりも高速化できる半導体装置を提供する。

【解決手段】フローティングゲートFGとコントロールゲートCG、第1導電型ソース13s及び第1導電型ドレイン13dを有する第1導電型MOSトランジスタ13と、前記フローティングゲートFGと前記コントロールゲートCG、第2導電型ソース14s及び第2導電型ドレイン14dを有する第2導電型MOSトランジスタ14と、前記第1導電型ドレイン13d及び前記第2導電型ドレイン14dに接続される第1のソース/ドレイン11bと、第2のソース/ドレイン11aと、ゲートを有する選択トランジスタ11と、前記第1導電型ソースに接続される第1電源線VpLと、前記第2導電型ソースに接続される第2電源線VnLと、前記選択トランジスタ11の第2のソース/ドレイン11aに接続されるビット線BLと、前記選択トランジスタ11のゲートに接続されるワード線WLと、を有する。

(もっと読む)

不揮発性メモリ

【課題】メモリセルへのデータの書き込みと読出しの信頼性を高くした不揮発性メモリを提供する。

【解決手段】2つのメモリセルを隣接させた基本ユニットを単位にするメモリセルアレイを有し、前記基本ユニットの2つのメモリセルのメモリセル選択用トランジスタのソース端子を共通のソース線に接続し、前記2つのメモリセルを2つのビット線に接続した抵抗変化型メモリであって、前記ソース線の配線パターンと前記ビット線の配線パターンを平行に走行させ、前記ソース線の配線パターンと前記ビット線の配線パターンの一部の領域を上下で重ねあわせて対向させる。

(もっと読む)

半導体装置

【課題】有機化合物を含む層を有する素子が設けられたフレキシブルな記憶装置及び半導

体装置を歩留まり高く作製する。また、信頼性の高いフレキシブルな記憶装置及び半導体

装置を歩留まり高く作製する。

【解決手段】剥離層を有する基板上に素子層及び素子層を封止する絶縁層を有する積層体

を形成し、剥離層から積層体を剥離してフレキシブルな記憶装置及び半導体装置を作製す

る方法であって、素子層において第1の電極層及び第2の電極層からなる一対の電極間に

有機化合物を含む層を有する記憶素子を含み、少なくとも一方の電極層はスズを含む合金

層で形成する。また、第1の電極層及び第2の電極層からなる一対の電極間に有機化合物

を含む層を有する記憶素子を含み、少なくとも一方の電極層はスズを含む合金層で形成さ

れるフレキシブルな記憶装置及び半導体装置である。

(もっと読む)

半導体装置及びトリミング方法

【課題】ヒューズ素子の列数増に伴うトリミング時間の伸長を抑制する。

【解決手段】x方向に延伸する接地配線Gと、接地配線のy方向の一方側に設けられたヒューズ素子領域Aにx方向に沿って3列に並べて配置され、かつそれぞれの一端が接地配線Gに共通に接続される複数のヒューズ素子と、ヒューズ素子領域Aを挟んで接地配線Gの反対側に設けられ、ヒューズ素子領域Aに配置された複数のヒューズ素子それぞれの他端と接続される救済回路とを備え、上記複数のヒューズ素子は、それぞれ1つの欠陥選択線を示すアドレス情報を記憶する複数のヒューズ素子グループに所定個ずつグループ化され、同一のヒューズ素子グループに属する所定個のヒューズ素子は、同一列に配置されることを特徴とする

(もっと読む)

演算処理装置

【課題】キャッシュメモリから高速にデータを読み出すことができる演算処理装置を提供することを課題とする。

【解決手段】演算処理装置は、複数の記憶素子にそれぞれ複数のデータを記憶するキャッシュメモリと、前記キャッシュメモリからデータが読み出されたタイミングが閾値より遅いときにはエラーを検出するエラー検出回路(500)と、前記エラーが検出されないときには前記キャッシュメモリから読み出されたデータをラッチし、前記エラーが検出されたときには待機期間経過後に前記キャッシュメモリから読み出されたデータをラッチするラッチ回路(517)と、前記ラッチ回路によりラッチされたデータの処理を行う演算処理装置コアとを有する。

(もっと読む)

半導体記憶装置及び半導体装置

【課題】 可変抵抗素子への電圧印加極性が異なる2種類の書き込み動作後の各ベリファイ動作を夫々低消費電力且つ高速に実行可能な半導体記憶装置を提供する。

【解決手段】 書き込み回路22が、メモリセルの一端側から可変抵抗素子を経由して他端側へ電流を流すことで可変抵抗素子の電気抵抗を低抵抗化させるセット動作と、メモリセルの他端側から可変抵抗素子を経由して一端側へ電流を流すことで可変抵抗素子の電気抵抗を高抵抗化させるリセット動作を夫々実行可能に構成され、読み出し回路21が、メモリセルの一端側から可変抵抗素子を経由して他端側へ電流を流すことで可変抵抗素子の抵抗状態を読み出す第1読み出し動作と、メモリセルの他端側から可変抵抗素子を経由して一端側へ電流を流すことで可変抵抗素子の抵抗状態を読み出す第2読み出し動作を夫々実行可能に構成されている。

(もっと読む)

半導体ウエハ、半導体装置、および、半導体装置の製造方法

【課題】半導体チップのチップ面積の削減を図るとともに、半導体チップへの入力を記憶させる時間を短縮する。

【解決手段】本発明の半導体ウエハ1は、チップ領域10に形成され、絶縁膜を有し、電圧の印加による絶縁膜の絶縁破壊により導通状態となる複数のアンチヒューズ14を有するアンチヒューズ回路12と、チップ領域10を区画するダイシング領域20に複数のアンチヒューズ14の各々に対応して形成され、配線を有し、レーザー照射による配線の切断により非導通状態となる複数のレーザーヒューズ24を有するレーザーヒューズ回路22と、複数のアンチヒューズ14のうち、半導体チップへの入力に応じて非導通状態とされたレーザーヒューズ22に対応するアンチヒューズ14の有する絶縁膜に、電源からの電圧を印加させて、そのアンチヒューズ14を導通状態とする制御回路13と、を有する。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】熱工程による負担を減らし、メモリセル特性の向上を図る。

【解決手段】本実施形態による不揮発性半導体記憶装置の製造方法よれば、基板上30に、コントロールゲートCGとなる導電膜を形成する。前記導電膜の上面から下面まで貫通するホール40を形成する。前記ホールの内面上に、ブロック絶縁膜150を形成する。前記ブロック絶縁膜上に、電荷蓄積膜151を形成する。前記電荷蓄積膜上に、トンネル絶縁膜152を形成する。前記トンネル絶縁膜上に、半導体層SPを形成する。前記半導体層上に、前記ホールが埋め込まれないように酸素乖離の触媒作用を有する材料を含む膜153を形成する。前記ホールの内側から前記膜を介して、前記トンネル絶縁膜と前記半導体層との界面を酸化する。

(もっと読む)

半導体記憶装置

【課題】消費電力を低減出来る半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、選択トランジスタ、メモリセル、ワード線、セレクトゲート線、ドライバ回路12、ロウデコーダ11−0、及び検知回路16を備える。ドライバ回路12は、第1電圧Vss,Vccを出力する。ロウデコーダ11−0内の第1転送トランジスタは、ワード線及びセレクトゲート線の各々に関連付けられ、ドライバ回路12から出力された第1電圧を、ワード線及びセレクトゲート線に転送する。検知回路16は、データの消去時において、ビット線及び/またはソース線に印加される第2電圧を検知して、検知結果に応じてフラグを生成する。ドライバ回路12は、フラグが生成されたことに応答して第1電圧の値を変更して、第1転送トランジスタをカットオフさせる。

(もっと読む)

電子機器

【課題】非接触でデータの送受信が可能な半導体装置は、鉄道乗車カードや電子マネーカ

ードなどの一部では普及しているが、さらなる普及のためには、安価な半導体装置を提供

することが急務の課題であった。上記の実情を鑑み、単純な構造のメモリを含む半導体装

置を提供して、安価な半導体装置及びその作製方法の提供を課題とする。

【解決手段】有機化合物を含む層を有するメモリとし、メモリ素子部に設けるTFTのソ

ース電極またはドレイン電極をエッチングにより加工し、メモリのビット線を構成する導

電層とする。

(もっと読む)

半導体装置

【課題】適切に電源電圧を負荷回路に供給することができる、半導体装置を提供する。

【解決手段】電圧トランスファ20及びセンスノード配線33が設けられており、電圧トランスファ20は、各Sub−Arrayに応じて設けられたNMOSトランジスタTRにより、ノード32とノード30との間が接続される。電圧トランスファ20のトランジスタTRは、ソース及びドレインの一方が電源線31の各Sub−Arrayに応じた位置に接続されており、ソース及びドレインの他方がセンスノード配線33に接続されている。また、トランジスタTRのゲートには、対応するSub−Arrayのデコード信号A0〜AXが入力される。

(もっと読む)

半導体装置

【課題】半導体チップに構成されるメモリコアにおける電源系を容易に分離可能な配線構造を実現しスループットの向上が可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、半導体チップC1に複数のメモリコア(DRAMコア)が構成される。各メモリコアは、第1電源によって動作しパラレルデータを双方向に伝送するデータバスを駆動する第1回路領域と、第1電源と分離された第2電源によって動作しデータバスを伝送されるパラレルデータと外部端子を介して入出力されるシリアルデータとを双方向に変換する第2回路領域と含む。第1貫通電極群23は、第1回路領域に第1電源を供給する複数の貫通電極をY方向に並べて配置され、第2貫通電極群21は、第2回路領域に第2電源を供給する複数の貫通電極をY方向と交差するX方向に並べて配置される、それぞれの貫通電極群を経由して第1及び第2電源の配線群が互いに分離した配置で形成される。

(もっと読む)

1 - 20 / 893

[ Back to top ]